# Ke Se Deig AC ac, Hg -Efficie c PFC Sage Ui g NCP1623A AND90156/D

#### Description

This paper describes the key steps to rapidly design a CrM/DCM PFC stage driven by the NCP1623. The process is illustrated in a practical 100–W, universal mains application:

- Maximum Output Power: 100 W

- Rms Line Voltage Range: from 90 V to 264 V

- Regulation output voltage:

- ◆ 250 V in low line (115–V mains)

- 390 V in high line (230–V mains)

#### Introduction

There're several options of the NCP1623. This application note focuses on the A version (NCP1623A) which mainly differs from the other versions in the follower boost capability.

Housed in either SOIC-8 or TSOP-6 packages, the NCP1623A is an extremely compact PFC controller

• *Redundant over-voltage protection (OVP2):* CS/ZCD multi-functional pin is used to detect excessive output voltage levels and prevent a destructive output voltage

# **STEP 1: DEFINE KEY SPECIFICATIONS**

• *Line frequency, f<sub>line</sub>:*

For instance, at low line, full load (top of the sinusoid), the switching frequency is:

$$f_{sw} = \frac{\left(\sqrt{2} \cdot 90\right)^2 \cdot \left(250 - \sqrt{2} \cdot 90\right)}{4 \cdot 105 \cdot 250 \cdot 200 \cdot 10^{-6}} \cong 95 \text{ kHz}$$

## **STEP 3: IC CONTROL CIRCUIT DESIGN**

#### **FB Pin Circuit**

As shown by Figure 1, the feed-back arrangement consists of:

• A resistor divider that scales down the bulk voltage to provide the FB pin with the feedback signal. The upper resistor of the divider generally consists of two or three resistors for safety considerations. If not, any accidental shortage of  $R_{FB1}$  would apply the output high voltage to the controller and destroy it.

•

## **VCTRL Pin Circuit**

In order to find the control to output transfer function, the output voltage is defined by the multiplication of the output current and the output impedance. Using equation 2 and assuming the efficiency is 100%, the output current is given by:

$$\begin{split} i_{out} \left( v_{ctrl}, \ v_{out} \right) &= \frac{p_{in}}{v_{out}} = \frac{V_{line,rms}^2 \cdot t_{on}}{2 \cdot L \cdot v_{out}} \\ &= \frac{V_{line,rms}^2 \cdot T_{on.max} \cdot \left( v_{ctrl} - 0.5 \right)}{8 \cdot L \cdot v_{out}} \qquad (eq. 33) \end{split}$$

The output current partial differentiation by the output voltage is equivalently the output load resistance,  $R_{load}$ , based on the equation:

$$\frac{\delta i_{out}}{\delta v_{out}} = -\frac{V_{\text{line,rms}}^2 \cdot T_{\text{on.max}} \cdot (V_{\text{ctrl}} - 0.5)}{8 \cdot L \cdot v_{\text{out}}^2}$$

$$= -\frac{i_{\text{out}}}{v_{\text{out}}} = -\frac{1}{R_{\text{load}}}$$

(eq. 34)

Therefore,  $\delta i_{out} / \delta v_{out}$  can be included in the output impedance and total output impedance is:

$$z_{out}(s) = R_{load} \parallel R_{load} \parallel \frac{1}{s \cdot C_{BULK}}$$

(eq. 35)

The output current partial differentiation by the control voltage is:

$\delta i_{out}$

$$\begin{split} \mathsf{R}_{0} &= \frac{390 \text{ V}}{2.5 \text{ V} \cdot 20 \,\mu\text{S}} = 780 \text{ k}\Omega \\ \mathsf{G}_{0} &= \frac{264 \text{ V}^{2} \cdot 5 \,\mu\text{s} \cdot 1.52 \text{ k}\Omega}{16 \cdot 200 \,\mu\text{H} \cdot 390 \text{ V}} = 424 \\ \mathsf{C}_{Z} &= \frac{424}{2\pi \cdot 25 \text{ Hz} \cdot 780 \text{ k}\Omega} = 3.46 \,\mu\text{F} \approx 3.3 \,\mu\text{F} \\ \mathsf{R}_{Z} &= \frac{1.52 \,k\Omega \cdot 68 \,\mu\text{F}}{2 \cdot 3.3 \,\mu\text{F}} = 15.6 \,k\Omega \approx 15 \,k\Omega \\ \mathsf{C}_{\mathsf{P}} &= \frac{\tan\left(\frac{\pi}{2} - \frac{\pi}{3}\right)}{2\pi \cdot 25 \text{ Hz} \cdot 15 \,k\Omega} = 245 \,\text{nF} \approx 220 \,\text{pF} \end{split}$$

(eq. 46)

#### **CS/ZCD** Pin Circuit

The circuit detects an over–current situation if the voltage across the current sense resistor exceeds 0.5 V. Hence:

$$R_{SENSE} = \frac{0.5 \text{ V}}{\left(I_{L,pk}\right)_{max}}$$

(eq. 47)

Combining the result in equation 6 leads to:

$$R_{SENSE} = \frac{0.5 \text{ V}}{3.3 \text{ A}} = 0.15 \Omega$$

(eq. 48)

In our practical case, 0.12  $\Omega$  resistor is selected to have a bit of margin.  $R_{SENSE}$  losses can be computed using equation 10 giving the MOSFET conduction losses where  $R_{SENSE}$  replaces  $R_{DS(on)}$ :

$$\begin{split} (\mathsf{P}_{\mathsf{RSENSE}})_{max} &= \frac{4}{3} \cdot \mathsf{R}_{\mathsf{SENSE}} \cdot \left( \frac{\mathsf{P}_{\mathsf{out},max}}{\eta \cdot (\mathsf{V}_{\mathsf{line},\mathsf{rms}})_{\mathsf{LL}}} \right)^2 \\ & \cdot \left( 1 - \frac{8\sqrt{2} \cdot (\mathsf{V}_{\mathsf{line},\mathsf{rms}})_{\mathsf{LL}}}{3\pi \cdot \mathsf{V}_{\mathsf{out},\mathsf{LL}}} \right) \qquad (\mathsf{eq.}\ 49) \end{split}$$

Hence, our 0.12  $\Omega$  current sense resistor will dissipate about 124 mW at full load, low line.

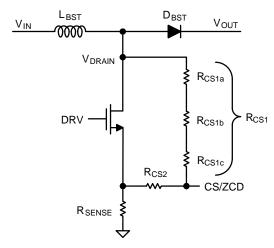

Figure 3. Drain Sensing for ZCD

The drain sensing based ZCD circuitry is shown in Figure 3. Drain voltage is sensed by CS resistor network and scaled down by  $K_{CS}$ :

$$K_{CS} = \frac{R_{CS1} + R_{CS2}}{R_{CS2}}$$

(eq. 50)

where  $K_{CS}$  is 133 and  $R_{CS2}$  is 62 k $\Omega$  in general. The values of  $R_{CS1}$  and  $R_{CS2}$

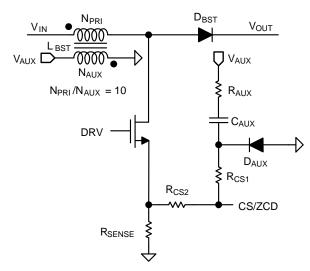

Figure 4. Aux. Winding Sensing for ZCD

It is possible to use the schematic shown in Figure 4 to generate the signal of CS/ZCD pin. Thanks to the auxiliary winding voltage capacitor  $C_{AUX}$ ,  $R_{AUX}$  and  $D_{AUX}$ , it is possible to generate at the cathode of  $D_{AUX}$  a voltage equal to the power MOSFET drain voltage multiplied by the auxiliary ( $N_{AUX}$ ) to primary ( $N_{PRI}$ ) transformer turns ratio. The parameter  $K_{CS}$  previously described is now defined by:

$$K_{CS} = \frac{N_{PRI}}{N_{AUX}} \cdot \frac{R_{CS1} + R}{N_{AUX}}$$

## SUMMARY

## Table 1. MAIN EQUATIONS

| Step                             | Components                                                                                                                                                                                                                                                                                                                                         | Formula                                                                                                                                                                              | Comments                                                            |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Step 1:<br>Key<br>Specifications | $f_{line}$ : Line frequency. It is generally specified in a range of 47 – 63 Hz for 50 Hz/60 Hz applications.<br>$(V_{line,rms})_{HL}$ : Lowest Level of the line voltage, e.g., 90 V.                                                                                                                                                             |                                                                                                                                                                                      |                                                                     |

|                                  | $(V_{line,rms})_{LL}$ : Level for the line voltage, e.g., 264 V.                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                      |                                                                     |

|                                  | V <sub>out,nom</sub> : Nominal Output Voltage at high–line, e.g., 390 V.<br>V <sub>out.LL</sub> : Output voltage at low–line (by follower boost) , e.g., 250 V.                                                                                                                                                                                    |                                                                                                                                                                                      |                                                                     |

|                                  | $(\delta V_{out})_{pk-pk}$ : Peak-to-Peak output voltage ripple in the line frequency                                                                                                                                                                                                                                                              |                                                                                                                                                                                      |                                                                     |

|                                  | $t_{HOLD-UP}$ : Hold-up Time that is the amount of time the output will remain valid during line drop-out, e.g., 10 ms. $V_{out,min}$ : Minimum output voltage allowing for operation of the downstream converter, e.g., 180 V. $P_{out,max}$ : Maximum output power consumed by the PFC load, e.g., 100 W. $\eta$ : System efficiency, e.g., 95%. |                                                                                                                                                                                      |                                                                     |

|                                  | $(P_{in,avg})_{max}$ : Maximum input power from the mains line at full load and low–line, e.g., 105 W assuming $\eta$ = 95%.                                                                                                                                                                                                                       |                                                                                                                                                                                      |                                                                     |

| Step 2:<br>Power Stage<br>Design | PFC Inductor                                                                                                                                                                                                                                                                                                                                       | $L \leq \frac{\left(V_{\text{line,rms}}\right)_{LL}^{2}}{2 \cdot \left(P_{\text{in,avg}}\right)_{\text{max}}} \cdot T_{\text{on,max}}$                                               | Maximum inductance<br><i>T<sub>on,max</sub></i> : max turn–on time  |

|                                  |                                                                                                                                                                                                                                                                                                                                                    | $\left(I_{L,pk}\right)_{max} = 2\sqrt{2} \frac{\left(P_{in,avg}\right)_{max}}{\left(V_{line,rms}\right)_{LL}}$                                                                       | Maximum peak current                                                |

|                                  |                                                                                                                                                                                                                                                                                                                                                    | $(I_{L,rms})_{max} = 2\sqrt{2} \frac{(I_{L,pk})_{max}}{\sqrt{6}}$                                                                                                                    | Maximum rms current                                                 |

|                                  | Bridge Diode                                                                                                                                                                                                                                                                                                                                       | $\left(P_{bridge}\right)_{max} \approx \frac{1.8 \cdot V_{f} \cdot P_{out,max}}{\left(V_{line,rms}\right)_{LL} \cdot \eta}$                                                          | Maximum power loss<br>V <sub>f</sub> : bridge diode forward voltage |

|                                  | MOSFET                                                                                                                                                                                                                                                                                                                                             | $(P_{on})_{max} = \frac{4}{3} \cdot R_{DS(on)} \cdot \left(\frac{P_{out,max}}{\eta \cdot \left(V_{line,rms}\right)_{LL}}\right)^2$                                                   | Maximum conduction loss $R_{DS(on)}$ : FET on–state resistance      |

|                                  |                                                                                                                                                                                                                                                                                                                                                    | $\cdot \left(1 - \frac{8\sqrt{2} \cdot \left(V_{\text{line,rms}}\right)_{\text{LL}}}{3\pi \cdot V_{\text{out,LL}}}\right)$                                                           |                                                                     |

|                                  | Boost Diode                                                                                                                                                                                                                                                                                                                                        | $(P_{diode})_{max} = V_{f} \cdot \frac{P_{out,max}}{V_{out,LL}}$                                                                                                                     | Maximum conduction loss                                             |

|                                  | Bulk Capacitor                                                                                                                                                                                                                                                                                                                                     | $C_{BULK} \geq \frac{P_{out,max}}{(\deltaV_{out})_{pk-pk}\cdot\omega\cdotV_{out,LL}}$                                                                                                | Minimum capacitance<br>to meet output ripple spec                   |

|                                  |                                                                                                                                                                                                                                                                                                                                                    | $C_{BULK} \geq \frac{2 \cdot P_{out,max} \cdot t_{HOLD-UP}}{V_{out,LL}^{2} - V_{out,min}^{2}}$                                                                                       | Minimum capacitance<br>to meet hold-up time spec                    |

|                                  |                                                                                                                                                                                                                                                                                                                                                    | $(I_{c,rms})_{max}$                                                                                                                                                                  | Maximum rms current                                                 |

|                                  |                                                                                                                                                                                                                                                                                                                                                    | $\cong \sqrt{\frac{32\sqrt{2}}{9\pi} \cdot \frac{\left(P_{in,avg}\right)_{max}^2}{\left(V_{line,rms}\right)_{LL} \cdot V_{out,LL}} - \left(\frac{P_{out,max}}{V_{out,LL}}\right)^2}$ |                                                                     |

## Table 1. MAIN EQUATIONS (continued)

Step

Comments

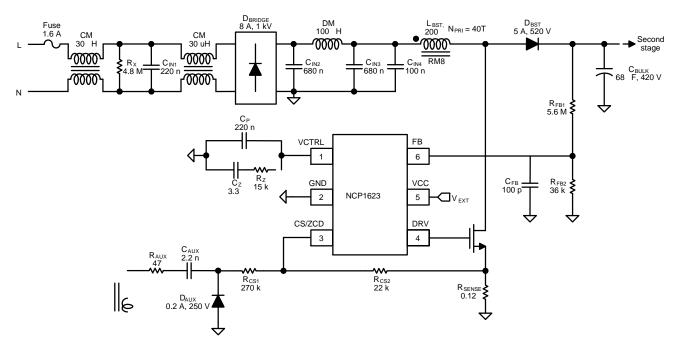

Figure 5. System Schematic of 100 W Design