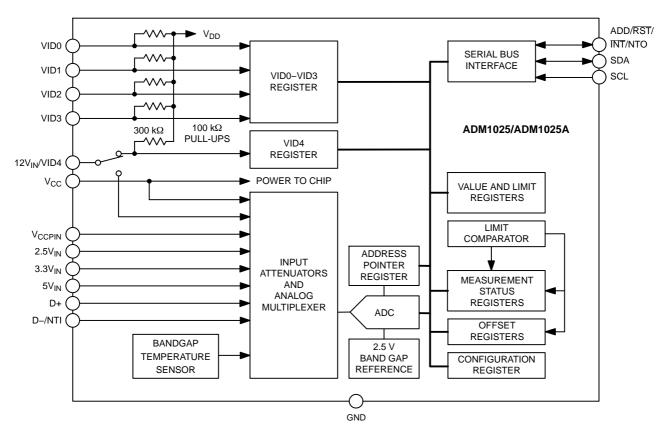

The ADM1025/ADM1025A1 is a complete system hardware monitor for microprocessor-based systems, providing measurement and limit comparison of various system parameters. Five voltage measurement inputs are provided for monitoring 2.5 V, 3.3 V, 5 V, and 12 V power supplies and the processor core voltage. The ADM1025/ADM1025A can monitor a sixth power supply voltage by measuring its own V<sub>CC</sub>. One input (two pins) is dedicated to a remote temperature-sensing diode, and an onchip temperature sensor allows ambient temperature to be monitored. The ADM1025A has open-drain VID inputs while the ADM1025 has on-chip 100 k $\Omega$  pull-ups on the VID inputs.

Measured values and in/out of limit status can be read out via an  $l^2C$  compatible serial System Management Bus. The device can be controlled and configured over the same serial bus. The device also has a programmable  $\overline{INT}$  output to indicate undervoltage, overvoltage, and overtemperature conditions.

The ADM1025/ADM1025A's 3.0 V to 5.5 V supply voltage range, low supply current, and  $I^2C$  compatible interface make it ideal for a wide range of applications. These include hardware monitoring and protection applications in personal computers, electronic test equipment, and office electronics.

#### Features

- Up to 8 Measurement Channels

- 5 Inputs to Measure Supply Voltages

- V<sub>CC</sub> Monitored Internally

- External Temperature Measurement with Remote Diode

- On-chip Temperature Sensor

- 5 Digital Inputs for VID Bits

- Integrated 100 kΩ Pull-ups on VID Pins (ADM1025 Only)

- LDCM Support

- I<sup>2</sup>C Compatible System Management Bus (SMBus)

- Programmable RST Output Pin

- Programmable INT Output Pin

- Configurable Offset for Internal/External Channel

- Shutdown Mode to Minimize Power Consumption

- Limit Comparison of All Monitored Values

#### Applications

- Network Servers and Personal Computers

- Microprocessor-based Office Equipment

- Test Equipment and Measuring Instruments

See detailed ordering and

A CONTRACTOR OF THE OWNER OF THE

http://onsemi.com

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

Figure 1. Functional Block Diagram

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Rating                                     | Value        | Unit |  |

|--------------------------------------------|--------------|------|--|

| Positive Supply Voltage (V <sub>CC</sub> ) | 6.5          | V    |  |

| Voltage on 12 V V <sub>IN</sub> Pin        | 20           | V    |  |

| Voltage on Any Input or Output Pin         | -0.3 to +6.5 | V    |  |

| Input Current at Any Pin                   | ±5           | mA   |  |

| Package Input Current                      | ±20          | mA   |  |

#### Table 3. PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic                | Description                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SDA                     | Digital I/O. Serial bus bidirectional data. Open-drain output.                                                                                                                                                                                                                                                                                                   |

| 2       | SCL                     | Digital Input. Serial bus clock.                                                                                                                                                                                                                                                                                                                                 |

| 3       | GND                     | System Ground                                                                                                                                                                                                                                                                                                                                                    |

| 4       | V <sub>CC</sub>         | Power. Can be powered by 3.3 V standby power if monitoring in low power states is required. This pin also serves as the analog input to monitor $V_{CC}$ .                                                                                                                                                                                                       |

| 5       | VID0                    | Digital Input. Core voltage ID readouts from the processor. This value is read into the VID0–VID3 Status Register. It has an on-chip 100 k $\Omega$ pull-up resistor (ADM1025 only).                                                                                                                                                                             |

| 6       | VID1                    | Digital Input. Core voltage ID readouts from the processor. This value is read into the VID0–VID3 Status Register. It has an on-chip 100 k $\Omega$ pull-up resistor (ADM1025 only).                                                                                                                                                                             |

| 7       | VID2                    | Digital Input. Core voltage ID readouts from the processor. This value is read into the VID0–VID3 Status Register. It has an on-chip 100 k $\Omega$ pull-up resistor (ADM1025 only).                                                                                                                                                                             |

| 8       | VID3                    | Digital Input. Core voltage ID readouts from the processor. This value is read into the VID0–VID3 Status Register. It has an on-chip 100 k $\Omega$ pull-up resistor (ADM1025 only).                                                                                                                                                                             |

| 9       | D-/NTI                  | Analog/Digital Input. Connected to cathode of external temperature sensing diode. If held high at power-up, it initiates NAND tree test mode.                                                                                                                                                                                                                    |

| 10      | D+                      | Analog Input. Connected to anode of external temperature sensing diode.                                                                                                                                                                                                                                                                                          |

| 11      | 12V <sub>IN</sub> /VID4 | Programmable Analog/Digital Input. Defaults to 12 V <sub>IN</sub> analog input at power-up but may be programmed as VID4 Core Voltage ID readout from the processor. This value is read into the VID4 Status Register. In analog 12 V <sub>IN</sub> mode, it has an on-chip voltage attenuator. In VID4 mode, it has an on-chip 300 k $\Omega$ pull-up resistor. |

| 12      | 5V <sub>IN</sub>        | Analog Input. Monitors 5 V supply.                                                                                                                                                                                                                                                                                                                               |

| 13      | 3.3V <sub>IN</sub>      | Analog Input. Monitors 3.3 V supply.                                                                                                                                                                                                                                                                                                                             |

| 14      | 2.5V <sub>IN</sub>      | Analog Input. Monitors 2.5 V supply.                                                                                                                                                                                                                                                                                                                             |

| 15      | V <sub>CCPIN</sub>      | _                                                                                                                                                                                                                                                                                                                                                                |

#### Table 4. ELECTRICAL CHARACTERISTICS (continued)

(T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>CC</sub> = V<sub>MIN</sub> to V<sub>MAX</sub>, unless otherwise noted)

| Parameter                                       | Test Conditions/Comments | Min | Тур | Max | Unit |

|-------------------------------------------------|--------------------------|-----|-----|-----|------|

| OPEN-DRAIN DIGITAL OUTPUTS (ADD, RST, INT, NTO) |                          |     |     |     |      |

Output Low Voltage, V<sub>OL</sub>

$I_{OUT}$  = -6.0 mA,  $V_{CC}$

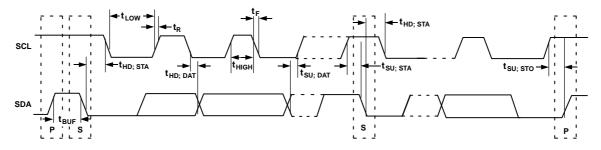

Figure 2. Serial Bus Timing Diagram

# TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)

### **General Description**

The ADM1025/ADM1025A is a complete system hardware monitor for microprocessor-based systems. The device communicates with the system via a serial System Management Bus. The serial bus controller has a hardwired address line for device selection (Pin 16), a serial data line for reading and writing addresses and data (Pin 1), and an input line for the serial clock (Pin 2). All control and programming functions of the ADM1025/ADM1025A are performed over the serial bus.

#### **Measurement Inputs**

The device has six measurement inputs, five for voltage and one for temperature. It can also measure its own supply voltage and can measure ambient temperature with its on-chip temperature sensor.

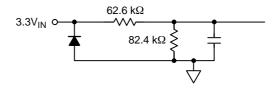

Pins 11 through 15 are analog inputs with on chip attenuators configured to monitor 12 V, 5 V, 3.3 V, 2.5 V, and the processor core voltage, respectively. Pin 11 may alternatively be programmed as a digital input for Bit 4 of the processor voltage ID code.

Power is supplied to the chip via Pin 4, and the system also monitors the voltage on this pin.

Remote temperature sensing is provided by the D+ and D inputs, to which a diode-connected, external temperature-sensing transistor may be connected.

An on-chip band gap temperature sensor monitors system ambient temperature.

#### Sequential Measurement

When the ADM 1025/ADM 1025A monitoring sequence is started, it cycles sequentially through the measurement of analog inputs and the temperature sensors. Measured values froge on thimonitori270002 Tw1/JTT6.47262se with onlog y beesj-2 Regay erserialse surebe8987 12.45542 TD-.0004 Tc-.632 Tw5on-chi

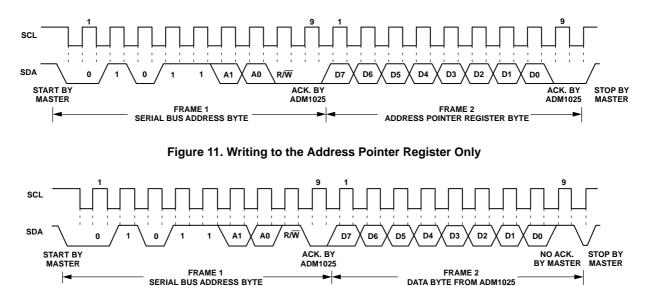

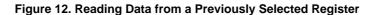

When reading data from a register there are two possibilities:

1. If the ADM1025/ADM1025A's Address Pointer Register value is unknown or not the desired value, it is first necessary to set it to the correct value before data can be read from the desired data register. This is done by performing a write to the ADM1025/ADM1025A as before, but only the data byte containing the register address is sent, since data should not be written to the register. This is shown in Figure 11.

A read operation is then performed consisting of the serial bus address, R/W bit set to 1, followed by the data byte read from the data register. This is shown in Figure 12.

2. If the Address Pointer Register is known to be already at the desired address, data can be read from the corresponding data register without first writing to the Address Pointer Register, so Figure 11 can be omitted.

NOTES:

- Although it is possible to read a data byte from a data register without first writing to the Address Pointer Register, if the Address Pointer Register is already at the correct value, it is not possible to write data to a register without writing to the Address Pointer Register because the first data byte of a write is always written to the Address Pointer Register.

- 2. In Figure 10 to Figure 12, the serial bus address is shown as the default value 01011(A1)(A0), where A1 and A0 are set by the three-state ADD pin.

- 3. In addition to supporting the Send Byte and Receive Byte protocols, the ADM1025/ADM1025A also supports the Read Byte protocol (see System Management Bus specifications Rev. 1.1 for more information).

- If Reset or interrupt functionality is required, the address pin cannot be strapped to GND, since this would keep the ADD/RST/INT/NTO pin permanently low.

Figure 13. Structure of Analog Inputs

allow for the tolerance of these supply voltages, the  $\ensuremath{\mathsf{A}}\xspace/\ensuremath{\mathsf{D}}\xspace$  converter

the absolute value of  $V_{BE}$ , varies from device to device, and individual calibration is required to null this out, so the technique is unsuitable for mass production.

The technique used in the ADM1025/ADM1025A is to measure the change in  $V_{BE}$  when the device is operated at two different currents.

This is given by:

$\Delta V_{BE} = KT/q \times ln(N)$

where:

*K* is Boltzmann's constant *q* is charge on the carrier *T* is absolute temperature in Kelvins *N* is ratio of the two currents

Figure 14 shows the input signal conditioning used to measure the output of an external temperature sensor. This figure shows the external sensor as a substrate transistor provided for temperature monitoring on some microprocessors, but it could equally well be a discrete transistor.

If a discrete transistor is used, the collector will not be grounded and should be linked to the base. If a PNP transistor is used, the base is connected to the D input and the emitter to the D+ input. If an NPN transistor is used, the emitter is connected to the D input and the base to the D+ input. Bit 6 of Status Register 2 (42h) is set if a remote diode fault is detected. The ADM1025/ADM1025A detects shorts from D+ to GND or supply, as well as shorts/opens between D+/D  $\cdot$ .

#### Table 7. TEMPERATURE DATA FORMAT

| Temperature | Digital Output |

|-------------|----------------|

| –128°C      | 1000 0000      |

| –125°C      | 1000 0011      |

| -100°C      | 1001 1100      |

| –75°C       |                |

### Layout Considerations

Digital boards can be electrically noisy environments and care must be taken to protect the analog inputs from noise, particularly when measuring the very small voltages from a remote diode sensor. The following precautions should be taken:

- 1. Place the ADM1025/ADM1025A as close as possible to the remote sensing diode. Provided that the worst noise sources, such as clock generators, data/address buses, and CRTs, are avoided, this distance can be four to eight inches.

- 2. Route the D+ and D tracks close together, in parallel, with grounded guard tracks on each side. Provide a ground plane under the tracks if possible.

- 3. Use wide tracks to minimize inductance and reduce noise pickup. 10 mil track minimum width and spacing is recommended.

#### Figure 15. Arrangement of Signal Tracks

4. Try to minimize the number of copper/solder joints, which can cause thermocouple effects. Where copper/solder joints are used, make sure that they are in both the D+ and D path and at the same temperature.

Thermocouple effects should not be a major problem as 1°C corresponds to about 240  $\mu$ V, and thermocouple voltages are about 3  $\mu$ V/°C of temperature difference. Unless there are two thermocouples with a big temperature differential between them, thermocouple voltages should be much less than 200  $\mu$ V.

- 5. Place 0.1 µF bypass and 1 nF input filter capacitors close to the ADM1025/ADM1025A.

- 6. If the distance to the remote sensor is more than eight inches, the use of twisted pair cable is recommended. This will work up to about 6 to 12 feet.

- 7. For really long distances (up to 100 feet) use

#### Generating an SMBALERT

The INT output can be used as an interrupt output or can be used as an SMBALERT. One or more INT outputs can be connected to a common SMBALERT line connected to the master. If a device's INT line goes low, the following procedure occurs:

- 1. SMBALERT is pulled low.

- 2. Master initiates a read operation and sends the Alert Response Address (ARA = 0001 100). This is a general call address that must not be used as a specific device address.

- 3. The device whose INT output is low responds to the Alert Response Address, and the master reads its device address. The address of the device is now known and it can be interrogated in the usual way.

- 4. If more than one device's INT output is low, the one with the lowest device address will have priority, in accordance with normal SMBus arbitration.

- 5. Once the ADM1025/ADM1025A has responded to the Alert Response Address, it will reset its INT output; however, if the error condition that caused the interrupt persists, INT will be reasserted on the next monitoring cycle.

#### **NAND Tree Tests**

A NAND tree is provided in the ADM1025/ADM1025A for Automated Test Equipment (ATE) board level connectivity testing. The device is placed into NAND Test Mode by powering up with Pin 9 (D /NTI) held high. This pin is automatically sampled after power-up, and if it is connected high, the NAND test mode is invoked.

In NAND test mode, all digital inputs may be tested as illustrated below. ADD/RST/INT/NTO will become the NAND test output pin.

To perform a NAND tree test, all pins are initially driven low. The test vectors set all inputs low, then one-by-one toggle them high (keeping them high). Exercising the test circuit with this "walking one" pattern, starting with the input closest to the output of the tree, cycling toward the farthest, causes the output of the tree to toggle with each input change. Allow for a typical propagation delay of 500 ns. The structure of the NAND tree is shown in Figure 17.

)<u>-D-D-</u>D1

Figure 17. NAND Tree

the Test Register to 1, setting Bit 6 of the VID Register to 1, and clearing Bit 7 of the VID Register.

### **Starting Conversion**

Table 12. REGISTER 41h -

### IMIT REGISTERS (Note 1)

| Description                      |  |  |  |  |  |

|----------------------------------|--|--|--|--|--|

| Manufacturers Test Register      |  |  |  |  |  |

| Offset Register                  |  |  |  |  |  |

| 2.5 V Reading                    |  |  |  |  |  |

| V <sub>CCP</sub> Reading         |  |  |  |  |  |

| 3.3 V Reading                    |  |  |  |  |  |

| 5 V Reading                      |  |  |  |  |  |

| 12 V Reading                     |  |  |  |  |  |

| V <sub>CC</sub> Reading          |  |  |  |  |  |

| Remote Diode Temperature Reading |  |  |  |  |  |

| Local Temperature Reading        |  |  |  |  |  |

| 2.5 V High Limit                 |  |  |  |  |  |

| 2.5 V Low Limit                  |  |  |  |  |  |

| V <sub>CCP</sub> High Limit      |  |  |  |  |  |

| V <sub>CCP</sub> Low Limit       |  |  |  |  |  |

| 3.3 V High Limit                 |  |  |  |  |  |

| 3.3 V Low Limit                  |  |  |  |  |  |

| 5 V High Limit                   |  |  |  |  |  |

| 5 V Low Limit                    |  |  |  |  |  |

| 12 V High Limit                  |  |  |  |  |  |

Table 20. NAND TREE TEST VECTORS

|            |     |     |      |      |      |      | _           |

|------------|-----|-----|------|------|------|------|-------------|

| Vector No. | SDA | SCL | VID0 | VID1 | VID2 | VID3 | ADD/RST/INT |

|            |     |     |      |      |      |      |             |

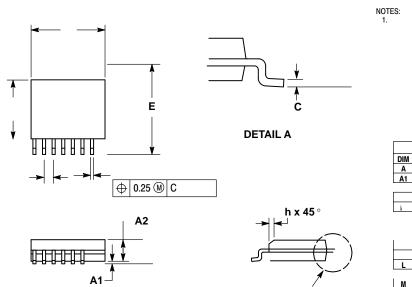

### QSOP16 CASE 492-01 ISSUE A

DATE 23 MAR 2011

DETÁIL A

|     | INC   | HĔ    |  |

|-----|-------|-------|--|

| DIM | MIN   | MA    |  |

| Α   | 0.053 | 0.069 |  |

| A1  | 0.004 | 0.010 |  |

|     |       |       |  |

|     | 0.008 | 0.012 |  |

| 1   | 0.007 | 0.010 |  |

|     |       |       |  |

|     |       |       |  |

|   |   | 0.025 BSC   |  |       |  |

|---|---|-------------|--|-------|--|

|   |   | 0.009 0.020 |  | 0.020 |  |

|   | L | 0.016       |  | 0.050 |  |

| L | М | 0           |  | 8     |  |

SCALE 2:1

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi