# 8-Bit Programmable 2- to 4-Phase Synchronous Buck Controller

# ADP3198

#### **FEATURES**

Se ec ab e 2-, 3-, 4-ae еа а. 1MH e ае \_-caedffee\_ae, -11 V е . e e ea e c-e.e.PWM ...... f , e.face.e.e.a ι. e d .e E, a ced PWM fe def e ce, e, ad a e. e f a ce Acecebaac be ee a ае е-B. . -. d/c ba ba ι, VID c de c a е ab e 0.5 V 1.6 V D \_ a \_ а b. VR10. a dVR11 ecfca -сс. ес, а ab e а ab e ac-ffdea

#### **APPLICATIONS**

De. PC e., ef, e.e, ea, l.e, ce VRM d.e

#### **GENERAL DESCRIPTION**

The ADP3198<sup>1</sup> is a highly efficient, multiphase, synchronous buck switching regulator controller optimized for converting a 12 V main supply into the core supply voltage required by high performance Intel processors. It uses an internal 8-bit DAC to read a voltage identification (VID) code directly from the processor, which is used to set the output voltage between 0.5 V and 1.6 V.

This device uses a multimode PWM architecture to drive the logic-level outputs at a programmable switching frequency that can be optimized for VR size and efficiency. The phase relationship of the output signals can be programmed to provide 2-, 3-, or 4-phase operation, allowing for the construction of up to four complementary buck switching stages.

The ADP3198 also includes programmable no load offset and slope functions to adjust the output voltage as a function of the load current, optimally positioning it for a system transient. The ADP3198 also provides accurate and reliable short-circuit protection, adjustable current limiting, and a delayed powergood output that accommodates on-the-fly output voltage changes requested by the CPU.

<sup>1</sup>P b U.S.P N b 6,683,441;

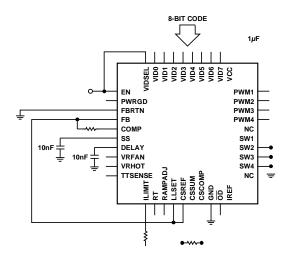

#### FUNCTIONAL BLOCK DIAGRAM

| SHUNT<br>REGULATOR                        |                             |

|-------------------------------------------|-----------------------------|

| 850mV                                     |                             |

| DAC<br>+ 150mV<br>CSREF<br>DAC<br>- 500mV | 2/3/4-PHASE<br>DRIVER LOGIC |

|                                           |                             |

|                                           |                             |

|                                           |                             |

|                                           |                             |

|                                           |                             |

|                                           |                             |

| VID DAC                                   | $\supset$                   |

2008 SCILLC. A, \_ e e . ed. Ja, .a. 2008 Re. . 2 Pb.\_ / N\_b : ADP3198/D

### TABLE OF CONTENTS

| Features1                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                                                                  |

| General Description1                                                                                                                                                                                                                                                                                           |

| Functional Block Diagram1                                                                                                                                                                                                                                                                                      |

| Revision History2                                                                                                                                                                                                                                                                                              |

| Specifications                                                                                                                                                                                                                                                                                                 |

| Test Circuits                                                                                                                                                                                                                                                                                                  |

| Absolute Maximum Ratings6                                                                                                                                                                                                                                                                                      |

| ESD Caution6                                                                                                                                                                                                                                                                                                   |

| Pin Configuration and Function Descriptions7                                                                                                                                                                                                                                                                   |

| Typical Performance Characteristics9                                                                                                                                                                                                                                                                           |

| Theory of Operation                                                                                                                                                                                                                                                                                            |

| Start-Up Sequence10                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                |

| Phase Detection Sequence                                                                                                                                                                                                                                                                                       |

| Phase Detection Sequence                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                |

| Master Clock Frequency11                                                                                                                                                                                                                                                                                       |

| Master Clock Frequency11<br>Output Voltage Differential Sensing11                                                                                                                                                                                                                                              |

| Master Clock Frequency                                                                                                                                                                                                                                                                                         |

| Master Clock Frequency                                                                                                                                                                                                                                                                                         |

| Master Clock Frequency       11         Output Voltage Differential Sensing       11         Output Current Sensing       11         Active Impedance Control Mode       11         Current Control Mode and Thermal Balance       11                                                                          |

| Master Clock Frequency       11         Output Voltage Differential Sensing       11         Output Current Sensing       11         Active Impedance Control Mode       11         Current Control Mode and Thermal Balance       11         Voltage Control Mode       12                                    |

| Master Clock Frequency       11         Output Voltage Differential Sensing       11         Output Current Sensing       11         Active Impedance Control Mode       11         Current Control Mode and Thermal Balance       11         Voltage Control Mode       12         Current Reference       12 |

| Master Clock Frequency11Output Voltage Differential Sensing11Output Current Sensing11Active Impedance Control Mode11Current Control Mode and Thermal Balance11Voltage Control Mode12Current Reference12Enhanced PWM Mode12                                                                                     |

| Master Clock Frequency11Output Voltage Differential Sensing11Output Current Sensing11Active Impedance Control Mode11Current Control Mode and Thermal Balance11Voltage Control Mode12Current Reference12Enhanced PWM Mode12Delay Timer12                                                                        |

| Power-Good Monitoring                                       | 13 |

|-------------------------------------------------------------|----|

| Output Crowbar                                              | 14 |

| Output Enable and UVLO                                      | 14 |

| Thermal Monitoring                                          | 14 |

| Application Information                                     | 19 |

| Setting the Clock Frequency                                 | 19 |

| Soft Start Delay Time                                       | 19 |

| Current-Limit Latch-Off Delay Times                         | 19 |

| Inductor Selection                                          | 19 |

| Current Sense Amplifier                                     | 20 |

| Inductor DCR Temperature Correction                         | 21 |

| Output Offset                                               | 22 |

| C <sub>OUT</sub> Selection                                  | 22 |

| Power MOSFETs                                               | 24 |

| Ramp Resistor Selection                                     | 25 |

| COMP Pin Ramp                                               | 25 |

| Current-Limit Setpoint                                      | 25 |

| Feedback Loop Compensation Design                           | 25 |

| C <sub>IN</sub> Selection and Input Current di/dt Reduction | 27 |

| Thermal Monitor Design                                      | 27 |

| Shunt Resistor Design                                       | 28 |

# **SPECIFICATIONS**

VCC = 5 V, FBRTN = GND,  $T_A = 0^{\circ}$ C to 85°C, unless otherwise noted.<sup>1</sup>

#### Table 1.

| Paa ee                | Sb,   | C , d _ ,               | Μ,    | τ   | Ма    | U, |

|-----------------------|-------|-------------------------|-------|-----|-------|----|

| RF*R*NCC*URRN*        |       |                         |       |     |       |    |

| R . 🕰                 | R P'  |                         |       | 1.5 |       |    |

| R . <u>A</u> C        | RP    | R <sub>R P</sub> =100 , | 14.25 | 15  | 15.75 |    |

| RR <sup>7</sup> R PFR |       |                         |       |     |       |    |

| R <sup>2</sup>        | с / Р |                         | 0     |     | 4.4   |    |

.. .

### **TEST CIRCUITS**

#### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Ρ, Ν. | M,e,c          | De c _ ,                 |

|-------|----------------|--------------------------|

| 20    | R F            | CR FA; D'Y, SS,          |

|       |                | , S NS +                 |

| 21    | <sup>₹</sup> N | * .R • .                 |

| 22 25 | S 4 S 1        | C 🖍                      |

|       |                | b .                      |

| 26    | N              | NC                       |

| 27 30 | P 4            | SF SF                    |

|       | P 1            | DP3110 C P 4, P 3 CC , _ |

|       |                | DP3198 2-, 3-, 4         |

| 31    | CC             | S D                      |

|       |                |                          |

| 32 39 | D7 D0          | DC GND,                  |

|       |                | , DCF                    |

| 40    | DS 4           | DDCS.P. DDC.D0 D7        |

|       |                | R10 R11 .                |

#### MASTER CLOCK FREQUENCY

The clock frequency of the ADP3198 is set with an external

# CURRENT-LIMIT, SHORT-CIRCUIT, AND LATCH-OFF PROTECTION

The ADP3198 compares a programmable current-limit set point to the voltage from the output of the current-sense

#### **OUTPUT CROWBAR**

To protect the load and output components of the supply, the PWM outputs are driven low, which turns on the low-side MOSFETs when the output voltage exceeds the upper crowbar threshold. This crowbar action stops once the output voltage falls below the release threshold of approximately 375 mV.

Turning on the low-side MOSFETs pulls down the output as the reverse current builds up in the inductors. If the output overvoltage is due to a short in the high-side MOSFET, this action current limits the input supply or blows its fuse, protecting the microprocessor from being destroyed.

#### **OUTPUT ENABLE AND UVLO**

For the ADP3198 to begin switching, the input supply (VCC) to the controller must be higher than the UVLO threshold and the EN pin must be higher than its 0.85 V threshold. This initiates a system start-up sequence. If either UVLO or EN is less than their respective thresholds, the ADP3198 is disabled. This holds the PWM outputs at ground, shorts the DELAY capacitor to ground, and forces PWRGD and OD signals low.

In the application circuit (see Figure 10), the  $\overline{OD}$  pin should be connected to the  $\overline{OD}$  inputs of the ADP3110A drivers.

Table 4.VR11 and VR10.x VID Codes for the ADP3198

Grounding  $\overline{OD}$  disables the drivers such that both DRVH and DRVL are grounded. This feature is important in preventing the discharge of the output capacitors when the controller is shut off. If the driver outputs are not disabled, a negative voltage can be generated during output due to the high current discharge of the output capacitors through the inductors.

#### THERMAL MONITORING

The ADP3198 includes a thermal-monitoring circuit to detect when a point on the VR has exceeded two different userdefined temperatures. The thermal-monitoring circuit requires an NTC thermistor to be placed between TTSENSE and GND.

A fixed current of  $8 \times IREF$  (normally giving 123 µA) is sourced out of the TTSENSE pin and into the thermistor. The current source is internally limited to 5 V. An internal circuit compares the TTSENSE voltage to a 1.105 V and a 0.81 V threshold, and outputs an open-drain signal at the VRFAN and VRHOT outputs, respectively. Once the voltage on the TTSENSE pin drops below its respective threshold, the open-drain outputs assert high to signal the system that an overtemperature event has occurred. Because the TTSENSE voltage changes slowly with respect to time, 50 mV of hysteresis is built into these comparators. The thermal monitoring circuitry does not depend on EN and is active when UVLO is above its threshold. When UVLO is below its threshold, VRFAN and VRHOT are forced low.

The user has the flexibility to choose either  $R_{CS}$  or  $R_{PH(X)}$ . However, it is best to select  $R_{CS}$  equal to 100 k  $\,$ , and then solve for  $R_{PH(X)}$  by rearranging Equation 6. Here,  $R_{CSA}$  =  $R_{O}$  = 1 m because this is equal to the design load line.

$$R_{PH(-)} = \frac{R_L}{R_{C_{\bullet}A}} \times R_{C_{\bullet}}$$

$$R_{PH()} = \frac{1.4 \text{ m}}{1.0 \text{ m}} \times 100 \text{ k} = 140 \text{ k}$$

Next, use Equation 7 to solve for  $C_{\text{CS}}$ .

$$C_{C_{\bullet}} = \frac{320 \text{ nH}}{1.4 \text{ m} \times 100 \text{ k}} = 2.28 \text{ nF}$$

It is best to have a dual location for  $C_{\rm CS}$  in the layout so that standard values can be used in parallel to get as close to the desired value. For best accuracy,  $C_{\rm CS}$  should be a 5% or 10% NPO capacitor. This example uses a 5% combination for  $C_{\rm CS}$  of two 1 nF capacitors in parallel. Recalculating  $R_{\rm CS}$  and  $R_{\rm PH(X)}$  using this capacitor combination yields 114 k and 160 k . The closest standard 1% value for  $R_{\rm PH(X)}$  is 158 k .

#### INDUCTOR DCR TEMPERATURE CORRECTION

When the inductor DCR is used as the sense element and

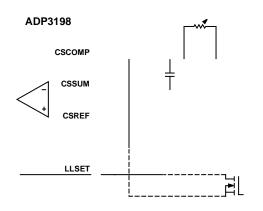

#### Load Line Setting

For load line values greater than 1 m  $_{\rm o}$ , R<sub>CSA</sub> can be set equal to R<sub>o</sub>, and the LLSET pin can be directly connected to the CSCOMP pin. When the load line value needs to be less than 1 m  $_{\rm o}$ , two additional resistors are required. Figure 12 shows the placement of these resistors.

#### **POWER MOSFETS**

For this example, the N-channel power MOSFETs have been selected for one high-side switch and two low-side switches per phase. The main selection parameters for the power MOSFETs are V<sub>GS(TH)</sub>, Q<sub>G</sub>, C<sub>ISS</sub>, C<sub>RSS</sub>, and R<sub>DS(ON)</sub>. The minimum gate drive voltage (the supply voltage to the ADP3110A) dictates whether standard threshold or logic-level threshold MOSFETs must be used. With V<sub>GATE</sub> ~10 V, logic-level threshold MOSFETs (V<sub>GS(TH)</sub> < 2.5 V) are recommended.

The maximum output current (I<sub>o</sub>) determines the  $R_{DS(ON)}$ requirement for the low-side (synchronous) MOSFETs. With the ADP3198, currents are balanced between phases, thus, the current in each low-side MOSFET is the output current divided by the total number of MOSFETs (n<sub>SF</sub>). With conduction losses being dominant, Equation 24 shows the total power that is dissipated in each synchronous MOSFET in terms of the ripple current per phase ( $I_R$ ) and average total output current ( $I_O$ ):

$$P_{\mathbf{g}F} = (1-D) \times \frac{I_O}{\mathbf{g}F}^2 + \frac{1}{12} \times \frac{I_R}{\mathbf{g}F}^2 \times R_{D\mathbf{g}(\mathbf{g}F)}$$

(24)

Knowing the maximum output current being designed for and the maximum allowed power dissipation, the user can find the required  $R_{DS(ON)}$  for the MOSFET. For D-PAK MOSFETs up to an ambient temperature of 50°C, a safe limit for  $P_{SF}$  is 1 W to

#### **RAMP RESISTOR SELECTION**

The ramp resistor ( $R_R$ ) is used for setting the size of the internal PWM ramp. The value of this resistor is chosen to provide the best combination of thermal balance, stability, and transient response. Equation 28 is used for determining the optimum value.

$$R_{R} = \frac{A_{R} \times L}{3 \times A_{D} \times R_{D_{9}} \times C_{R}}$$

$$R_{R} = \frac{0.2 \times 320 \text{ nH}}{3 \times 5 \times 2.4 \text{ m} \times 5 \text{ pF}} = 356 \text{ k}$$

(28)

where:

$A_R$  is the internal ramp amplifier gain.  $A_D$  is the current balancing amplifier gain.  $R_{D_{\mathbf{g}}}$  is the total low-side MOSFET on resistance.  $C_R$  is the internal ramp capacitor value.

The internal ramp voltage magnitude can be calculated by using

$$_{R} = \frac{A_{R} \times (1-D) \times {}_{ID}}{R_{R} \times C_{R} \times {}_{g}}$$

$$_{R} = \frac{0.2 \times (1-0.108) \times 1.3 \text{ V}}{357 \text{ k} \times 5 \text{ pF} \times 330 \text{ kHz}} = 394 \text{ mV}$$

(29)

The size of the internal ramp can be made larger or smaller.

Because of the multimode feedback structure of the ADP3198, the feedback compensation must be set to make the converter output impedance work in parallel with the output decoupling to make the load look entirely resistive. Compensation is needed for several poles and zeros created by the output inductor and the decoupling capacitors (output filter).

A type-three compensator on the voltage feedback is adequate for proper compensation of the output filter. Equation 35 to Equation 39 are intended to yield an optimal starting point for the design; some adjustments may be necessary to account for PCB and component parasitic effects (see the

First, compute the time constants for all the poles and zeros in the system using Equation 35 to Equation 39.

$$R_{E} = \times R_{O} + A_{D} \times R_{Dg} + \frac{R_{L} \times R_{R}}{ID} + \frac{2 \times L \times (1 - X) \times R_{R}}{X C \times R_{O} \times R_{D}}$$

$$R_E = 4 \times 1 \,\mathrm{m} + 5 \times 2.4 \,\mathrm{m} + \frac{1.4 \,\mathrm{m} \times 0.51 \,\mathrm{V}}{1.3 \,\mathrm{V}} + \frac{2 \times 320 \,\mathrm{nH} \times (1 - 0.432) \times 0.51 \,\mathrm{V}}{4 \times 5.6 \,\mathrm{mF} \times 1 \,\mathrm{m} \times 1.3 \,\mathrm{V}} = 22.9 \,\mathrm{m}$$

(35)

$${}_{A} = C \times \left(R_{O} - R'\right) + \frac{L}{R_{O}} \times \frac{R_{O} - R'}{R} = 5.6 \text{ mF} \times \left(1 \text{ m} - 0.5 \text{ m}\right) + \frac{240 \text{ pH}}{1 \text{ m}} \times \frac{1 \text{ m} - 0.5 \text{ m}}{0.6 \text{ m}} = 3.00 \text{ s}$$

(36)

$$_{B} = (R + R' - R_{O}) \times C = (0.6 \text{ m} + 0.5 \text{ m} - 1 \text{ m}) \times 5.6 \text{ mF} = 560 \text{ ns}$$

(37)

$$_{C} = \frac{\frac{A_{D} \times R_{D_{\bullet}}}{2 \times \bullet}}{\frac{1}{10} \times R_{E}} = \frac{0.51 \text{ V} \times 320 \text{ nH} - \frac{5 \times 2.4 \text{ m}}{2 \times 330 \text{ kHz}}}{1.3 \text{ V} \times 22.9 \text{ m}} = 5.17 \text{ s}$$

(38)

$${}_{D} = \frac{C \times C \times R_{O}^{2}}{C \times (R_{O} - R') + C \times R_{O}} = \frac{5.6 \text{ mF} \times 180 \text{ F} \times (1 \text{ m})^{2}}{5.6 \text{ mF} \times (1 \text{ m} - 0.5 \text{ m}) + 180 \text{ F} \times 1 \text{ m}} = 338 \text{ ns}$$

(39)

where:

R' is the PCB resistance from the bulk capacitors to the ceramics.  $R_{D_{2}}$  is the total low-side MOSFET on resistance per phase. In this example,  $A_{D}$

Tuning the ADP3198 section).

Figure 13 and Figure 14 show the typical transient response using these compensation values.

#### SHUNT RESISTOR DESIGN

The ADP3198 uses a shunt to generate 5 V from the 12 V supply range. A trade-off can be made between the power dissipated in the shunt resistor and the UVLO threshold. Figure 16 shows the typical resistor value needed to realize certain UVLO voltages. It also gives the maximum power dissipated in the shunt resistor for these UVLO voltages.

V<sub>IN</sub> (UVLO)

11.0

|   | <br> | <br> | <br> | <br> |  |

|---|------|------|------|------|--|

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   | <br> |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

|   | <br> |      | <br> | <br> |  |

|   |      |      |      |      |  |

|   |      |      |      |      |  |

| 1 |      |      |      |      |  |

| 1 |      |      |      |      |  |

|   |      |      |      |      |  |

#### General Recommendations

For good results, a PCB with at least four layers is recommended. This provides the needed versatility for control circuitry interconnections with optimal placement, power planes for ground, input and output power, and wide interconnection traces in the remainder of the power delivery current paths. Keep in mind that each square unit of 1 ounce copper trace has a resistance of ~0.53 m at room temperature.

Whenever high currents must be routed between PCB layers, use vias liberally to create several parallel current paths, so the resistance and inductance introduced by these current paths is minimized and the via current rating is not exceeded.

If critical signal lines (including the output voltage sense lines of the ADP3198) must cross through power circuitry, it is best to interpose a signal ground plane between those signal lines and the traces of the power circuitry. This serves as a shield to minimize noise injection into the signals at the expense of making signal ground a bit noisier.

An analog ground plane should be used around and under the ADP3198 as a reference for the components associated with the controller. This plane should be tied to the nearest output decoupling capacitor ground and should not be tied to any other power circuitry to prevent power currents from flowing into it.

The components around the ADP3198 should be located close to the controller with short traces. The most important traces to keep short and away from other traces are the FB pin and CSSUM pin. The output capacitors should be connected as close as possible to the load (or connector), for example, a microprocessor core, that receives the power. If the load is distributed, the