# AD>3611

## Wh Semirconductor

http://onsemi.com

DFN8 CP SUFFIX CASE 506AA

#### **Features**

- All in one Synchronous Buck Driver

- One PWM Signal Generates Both Drives

- Anticross conduction Protection Circuitry

- Output Disable Function

- Crowbar Control

- Synchronous Override Control

- This is a Pb Free Device

## **Applications**

- Mobile Computing CPU Core Power Converters

- Multiphase Desk note CPU Supplies

- Single supply Synchronous Buck Converters

- Nonsynchronous to Synchronous Drive Conversion

# MARKING DIAGRAMS

X = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

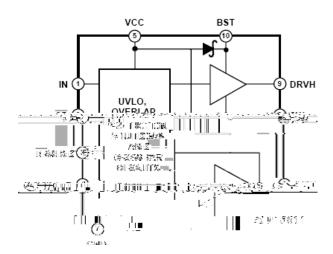

## SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

Figure 1. MSOP-10 Package Block Diagram

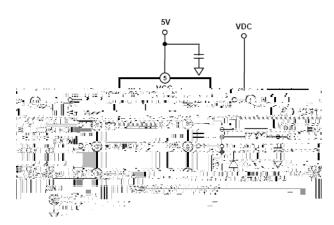

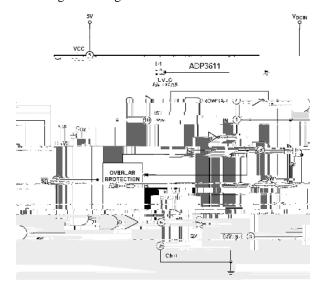

## **GENERAL APPLICATION CIRCUIT**

Figure 2. MSOP-10 Package Application Circuit

**Table 1. ORDERING INFORMATION**

| Model             | Temperature<br>Range | Package Description                       | Package<br>Option | Quantity<br>per Reel <sup>†</sup> | Branding |

|-------------------|----------------------|-------------------------------------------|-------------------|-----------------------------------|----------|

| ADP3611JRMZ-REEL* | −10°C to 100°C       | 10-Lead Mini Small Outline Package (MSOP) | RM-ïl0            |                                   |          |

$\textbf{Table 2. ELECTRICAL CHARACTERISTICS} \ (V_{CC} = \overline{SD} = 5 \ V, \ BST - SW = 5 \ V, \ T_A = -10^{\circ}C \ to \ 100^{\circ}C, \ unless \ otherwise \ noted)$

|  | Parameter | Symbol | Conditions | Min | Тур | Max | Unit |

|--|-----------|--------|------------|-----|-----|-----|------|

|--|-----------|--------|------------|-----|-----|-----|------|

LOGIC INPUTS (IN, SD, DRVLSD, CROWBAR)

Table 3. ABSOLUTE MAXIMUM RATINGS (Unless otherwise specified, all voltages are referenced to GND.)

|                                     | Parameter                      | Rating                     | Unit |

|-------------------------------------|--------------------------------|----------------------------|------|

| VCC                                 |                                | -0.3 to +6                 | V    |

| BST, DRVH                           | DC<br>t < 200 ns               | -0.3 to +26<br>-0.3 to +31 | V    |

| BST to SW                           |                                | -0.3 to +6                 | V    |

| BST to VCC                          | DC<br>t < 200 ns               | -0.3 to +21<br>-0.3 to +26 | V    |

| SW                                  | DC<br>t < 200 ns               | -1 to +21<br>-6 to +26     | V    |

| DRVH to SW                          |                                | -0.3 to +6                 | V    |

| DRVH                                |                                | SW - 0.3 to BST + 0.3      | V    |

| DRVL                                | DC<br>t < 200 ns               | -0.3 to +6<br>-5 to +6     | V    |

| All Other Inputs and Outputs        |                                | -0.3 to +6                 | V    |

| JA MSOP-10 Package                  | 2-Layer Board<br>4-Layer Board | 340<br>220                 | °C/W |

| JA QFN-8 2 mm x 2 mm Package        |                                | 143                        | °C/W |

| Operating Ambient Temperature Range |                                | -10 to +100                | °C   |

| Junction Temperature Range          |                                |                            |      |

| Table 4. F | PIN FUNCTION | DESCRIPTION | S |

|------------|--------------|-------------|---|

| Pin No.    |              |             |   |

| QFN        |              |             |   |

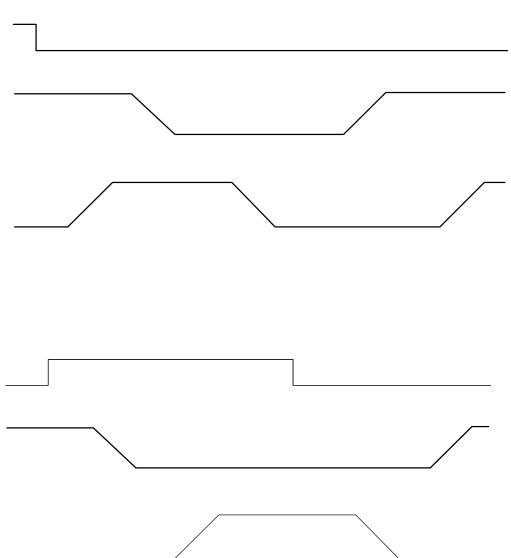

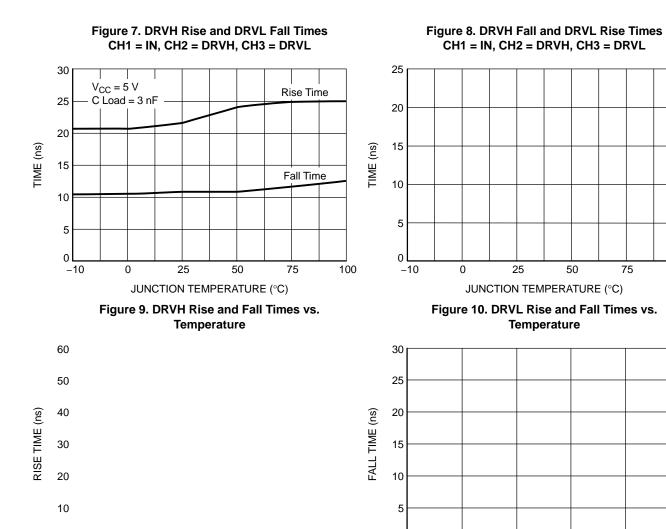

#### TYPICAL PERFORMANCE CHARACTERISTICS

. ...l.Triold.....

0

3

LOAD CAPACITANCE (nF)

Figure 11. DRVH and DRVL Rise Times vs.

**Load Capacitance**

Figure 12. DRVH and DRVL Fall Times vs. **Load Capacitance**

LOAD CAPACITANCE (nF)

2

75

100

10

10

## TYPICAL PERFORMANCE CHARACTERISTICS

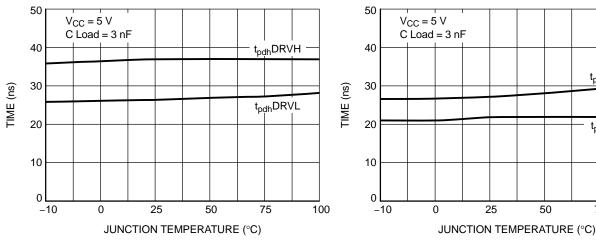

Figure 13. DRVH and DRVL  $t_{pdh}$  vs. Temperature

Figure 14. DRVH and DRVL  $t_{pdl}$  vs. Temperature

$t_{pdl}DRVH$

$t_{pdl}\overline{DRVL}$

75

100

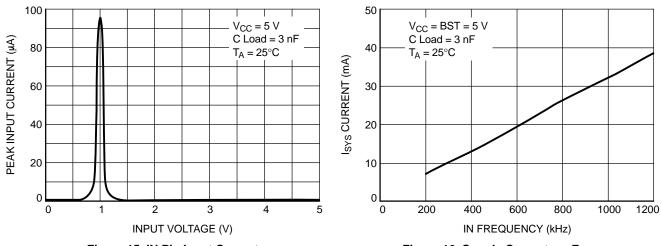

Figure 15. IN Pin Input Current vs. Input Voltage

Figure 16. Supply Current vs. Frequency

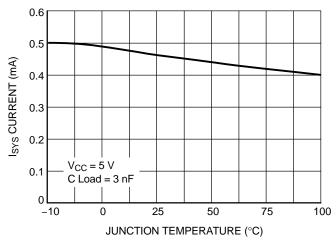

Figure 17. Supply Current vs. Temperature

## THEORY OF OPERATION

The ADP3611 is a dual MOSFET driver optimized for driving two N-channel MOSFETs in a synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each driver is capable of driving a 3 nF load at speeds up to 1 MHz. A more detailed description of the ADP3611 and its features follows. Refer to the detailed block diagram in Figure 18.

Figure 18. Detailed Block Diagram of the ADP3611

#### **Undervoltage Lockout**

The undervoltage lockout (UVLO) circuit hold4-twboth for

polarity reversal of the inductor current to maximize light load conversion efficiency. DRVLSD can also be pulled low for reverse voltage protection purposes.

When  $\overline{DRVLSD}$  is low, the low-side driver stays low. When  $\overline{DRVLSD}$  is high, the low-side driver is enabled and controlled by the driver signals, as previously described.

#### **Low-Side Driver Timeout**

In normal operation, the DRVH signal tracks the IN signal and turns off the Q1 high-side switch with a few 10 ns delay (t<sub>pdlDRVH</sub>) following the falling edge of the input signal. When Q1 is turned off, DRVL is allowed to go high, Q2 turns on, and the SW node voltage collapses to zero. But in a fault condition such as a high-side Q1 switch drain-source short circuit, the SW node cannot fall to zero, even when DRVH goes low. The ADP3611 has a timer circuit to address this scenario. Every time the IN goes low, a DRVL on-time delay timer is triggered. If the SW node voltage does not trigger a low-side turn-on, the DRVL on-time delay circuit does it instead, when it times out with t<sub>SW(TO)</sub> delay. If Q1 is still turned on, that is, its drain is shorted to the source, Q2 turns on and creates a direct short circuit across the  $V_{\mbox{\scriptsize DCIN}}$  voltage rail. The crowbar action causes the fuse in the V<sub>DCIN</sub> current path to open. The opening of the fuse saves the load (CPU) from potential damage that the high-side switch short circuit could have caused.

#### **Crowbar Function**

In addition to the internal low-side drive time-out circuit, the ADP3611 includes a CROWBAR input pin to provide a means for additional overvoltage protection. When CROWBAR goes high, the ADP3611 turns off DRVH and turns on DRVL. The crowbar logic overrides the overlap protection circuit, the shutdown logic, the DRVLSD logic,

## **Power and Thermal Considerations**

The major power consumption of the ADP3611-based driver circuit is from the dissipation of MOSFET gate charge. It can be estimated as

$$\label{eq:pmax} \textbf{P}_{\text{MAX}} \approx \text{VCC} \times (\textbf{Q}_{\text{HSGATE}} + \textbf{Q}_{\text{LSGATE}}) \times \textbf{f}_{\text{MAX}} \quad \text{(eq. 3)}$$

where:

$V_{CC}$  is the supply voltage 5 V.

$f_{MAX} \\$

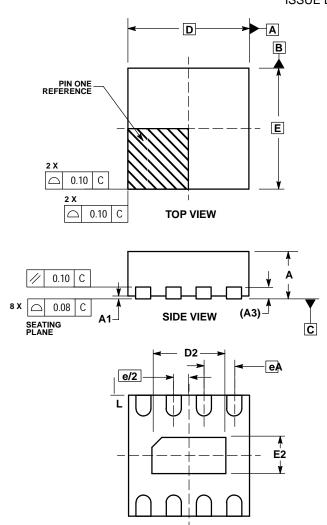

## **PACKAGE DIMENSIONS**

#### DFN8 CASE 506AA-01 ISSUE D

**BOTTOM VIEW**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

# PACKAGE DIMENSIONS

MSOP10 CASE 846AC-01 ISSUE O

\_\_\_\_