# 6 and 8-Channel Low Capacitance ESD Arrays

**Product Description**

The CM1216 family of diode arrays provide sESD protection for electronic components or sub-systems requiring minimal capacitive

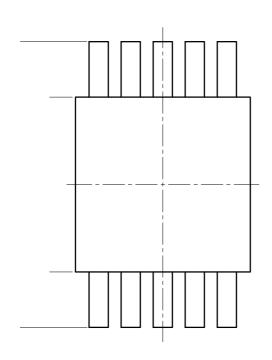

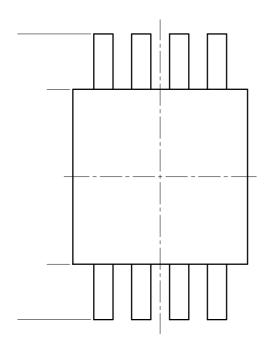

#### PACKAGE / PINOUT DIAGRAMS

#### Table 1. PIN DESCRIPTIONS

| Pin Name       | MSOP-8  | SOIC-8  | MSOP-10 | Туре | Description                  |

|----------------|---------|---------|---------|------|------------------------------|

|                | Pin No. | Pin No. | Pin No. |      |                              |

| CH1            | 1       | 1       | 1       | I/O  | ESD Channel                  |

| CH2            | 2       | 2       | 2       | I/O  | ESD Channel                  |

| CH3            | 4       | 4       | 3       | I/O  | ESD Channel                  |

| CH4            | 5       | 5       | 4       | I/O  | ESD Channel                  |

| V <sub>N</sub> | 3       | 3       | 5       | GND  | Negative voltage supply rail |

| CH5            | 6       | 6       | 6       | I/O  | ESD Channel                  |

| CH6            | 8       | 8       | 7       | I/O  | ESD Channel                  |

| VP             | 7       | 7       | 8       | PWR  | Positive voltage supply rail |

| CH7            | -       | _       | 9       | I/O  | ESD Channel                  |

| CH8            | _       | _       | 10      | I/O  | ESD Channel                  |

#### SPECIFICATIONS

emperature Rang. 2 580378.2614e2 r9T8 0 0 8 172.7433 447.533824(N)1029S 1 D Ch277433 447.533822 r9T29S 1 D Cha4nel

Table 4. ELECTRICAL OPERATING CHARACTERISTICS

#### APPLICATION INFORMATION

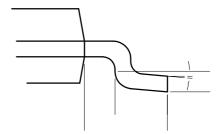

**Design Considerations**

In order to realize the maximum protection against ESD pulses, care must be taken in the PCB layout to minimize parasitic series inductances on the Supply/Ground rails as well as the signal trace segment between the signal input (typically a connector) and the ESD protection device. Refer to Application of Positive ESD Pulse between Input Channel and Ground, which illustrates an example of a positive ESD pulse striking an input channel. The parasitic series inductance back to the power supply is represented by  $L_1$  and  $L_2$ . The voltage  $V_{CL}$  on the line being protected is:

#### $V_{CL} = Fwd \text{ voltage drop of } D_1 + V_{SUPPLY} + L_1 \text{ x } d(I_{ESD}) / dt + L_2 \text{ x } d(I_{ESD}) / dt$

where  $I_{ESD}$  is the ESD current pulse, and  $V_{SUPPLY}$  is the positive supply voltage.

An ESD current pulse can rise from zero to its peak value in a very short time. As an example, a level 4 contact discharge per the IEC61000–4–2 standard results in a current pulse that rises from zero to 30 Amps in 1 ns. Here  $d(I_{ESD})/dt$  can be approximated by  $\Delta I_{ESD}/\Delta t$ , or 30/(1x10

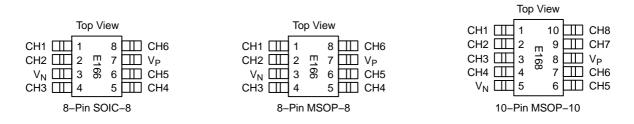

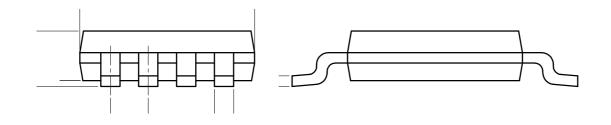

# PACKAGE DIMENSIONS

SOIC-8 EP CASE 751AC-01 ISSUE B

0.10 C

Y

>

Η

http://onsemi.com 5

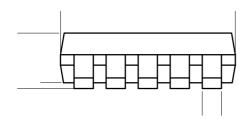

# PACKAGE DIMENSIONS

MSOP 8, 3x3 CASE 846AD-01 ISSUE O

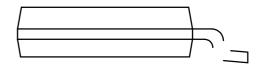

# PACKAGE DIMENSIONS

MSOP 10, 3x3 CASE 846AE-01 ISSUE O