# 4-Channel Low Capacitance ESD Protection Arrays

#### **Product Description**

The CM1225 diode array has been designed to provide ESD protection for electronic components or subsystems requiring minimal capacitive loading. This device is ideal for protecting systems with high data and clock rates or for circuits requiring low capacitive loading. Each ESD channel consists of a pair of diodes in series which steer the positive or negative ESD current pulse to the ground pins  $(V_N)$ . A Zener diode is embedded between the positive terminal of the diode pair to the ground. This eliminates the need for an external

**Table 1. PIN DESCRIPTIONS**

| 4–Channel, 10–Lead uUDFN–10 Package |                |      |             |  |  |  |  |

|-------------------------------------|----------------|------|-------------|--|--|--|--|

| Pin                                 | Name           | Туре | Description |  |  |  |  |

| 1                                   | CH1            | I/O  | ESD Channel |  |  |  |  |

| 2                                   | CH2            | I/O  | ESD Channel |  |  |  |  |

| 3                                   | V <sub>N</sub> | GND  | Ground      |  |  |  |  |

| 4                                   | СНЗ            | I/O  | ESD Channel |  |  |  |  |

| 5                                   | CH4            | I/O  | ESD Channel |  |  |  |  |

| 6                                   | NC             |      | No Connect  |  |  |  |  |

| 7                                   | NC             |      | No Connect  |  |  |  |  |

| 8                                   | V <sub>N</sub> | GND  | Ground      |  |  |  |  |

| 9                                   | NC             |      | No Connect  |  |  |  |  |

| 10                                  | NC             |      | No Connect  |  |  |  |  |

#### **PACKAGE / PINOUT DIAGRAMS**

10 Lead uUDFN

#### PERFORMANCE INFORMATION

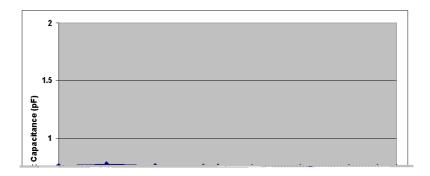

## Input Channel Capacitance Performance Curves

Figure 1. Typical Variation of  $C_{IN}$  vs.  $V_{IN}$  (f = 1 Mhz,  $V_{N}$  = 0 V, T = 25°C)

## PERFORMANCE INFORMATION (Cont'd)

Typical Filter Performance (nominal conditions unless specified otherwise, 50 Ohm Environment)

Sa. 1 100 MAG 5\_dB/\_ BFE\_0\_dB ... 11 - 0043 dB

Figure 2. Insertion Loss (S21) vs. Frequency (0 V DC Bias)

Figure 3. Insertion Loss (S21) vs. Frequency (2.5 V DC Bias)

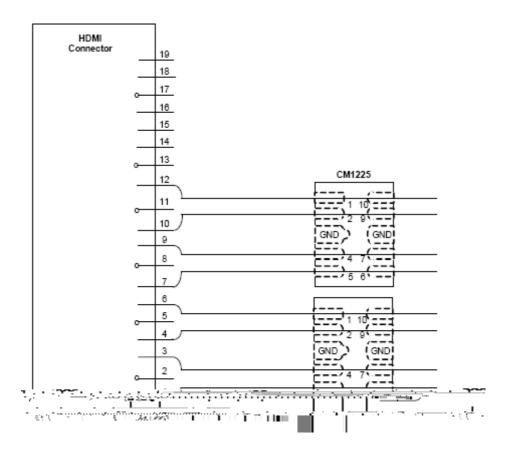

#### **APPLICATION INFORMATION**

#### **Design Considerations**

As a general rule, the CM1225 ESD protection array should be located as close as possible to the point of entry of expected electrostatic discharges. Use minimum PCB trace lengths to ground planes and between the signal input and the ESD devices.

#### **Additional Information**

See also ON Semiconductor Application Note "Design Considerations for ESD Protection".

Figure 4. Typical HDMI ESD Protection with CM1225 Connection

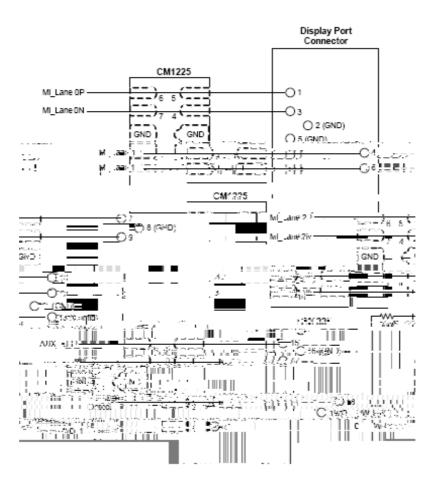

## **APPLICATION INFORMATION (Cont'd)**

Figure 5. Display Port ESD Protection with CM1225 Connection

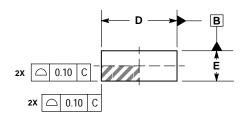

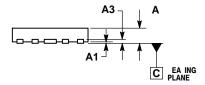

**PACKAGE DIMENSIONS**

UDFN10 2.5x1, 0.5P CASE 517BB **ISSUE O**

**DATE 17 NOV 2009**

#### SCALE 4:1

#### NOTES:

- DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- 3. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL.

| DIM |   |

|-----|---|

|     |   |

|     |   |

|     |   |

|     |   |

|     |   |

|     | • |

|     |   |

| DOCUMENT NUMBER: | 98AON47059E        | Electronic versions are uncontrolled except when accessed directly from the Document Repositol<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | UDFN10 2.5X1, 0.5P |                                                                                                                                                                                   | PAGE 1 OF 1 |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.