# Audio Processor for Digital Hearing Aids

# EZAIRO 8310 Hybrid

#### Introduction

Ezairo 8310 is an opeïprogrammable DSPbased hybrid specifically designed for use in higherformance hearing aids and hearables. The Ezairo 8310 hybrid includes the Ezairo 8300 Systemïon ïChip (SoC) onsemis high ïend DSP processor, as well as the LE25S16 onsemis ultra ïlow power flash memory.

Ezairo 8300 includes six programmable or seproigrammable processing cores, providing a high degree of parallelism and flexibility:

- € The CFX is an operprogrammable duaHarvard 24 bits digital signal processor (DSP) providing support for any type of audio signal processing

- € The ArmR CortexRiM3 processor is a 32bit RISC processor providing support for general processing and interfacing to external components

- € The HEAR configurable accelerator core is optimized for pre "programmed functions that are frequently needed in audio signal processing

- € The Filter Engine allows time domain filtering and supports an ultra ïlow ïdelay audio path

- € The LPDSP32 is an opeprogrammable dual

### **KEY FEATURES**

€ High Performance: Best in class MIPS/mW.

$\in$  Programmable Flexibility: the open programmable

DSPïbased

Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter | Min | Тур | Max  | Unit | Notes                              |

|-----------|-----|-----|------|------|------------------------------------|

| VBAT      | ï   | Ï   | 1.98 | V    | Power supply voltage               |

| VBATOD    | ï   | Ï   | 1.98 | V    | Output driver power supply voltage |

| VDDO2/3   | ï   | Ï   | 1.98 | V    | I/O supply voltage                 |

| VSSA      | 0   | Ï   | Ï    | V    | Analog ground                      |

| VSSOD     | 0   | Ï   | Ï    | V    | Output driver ground               |

| VSSC      |     | •   | •    |      | •                                  |

Table 3. ELECTRICAL PERFORMANCE SPECIFICATIONS

Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C at VBAT = 1.25 V. The system clock (SYS\_CLK) was set to 15.36 MHz. Parameters marked as screened are tested on each chip. Parameters marked as screened with one check are tested on each Ezairo 8300 chip and with two checks are tested on each Ezairo 8310 hybrid module.

### VDDA

| Parameter      | Symbol | Conditions                                                          | Min | Тур | Max | Unit | Screened |

|----------------|--------|---------------------------------------------------------------------|-----|-----|-----|------|----------|

| Output voltage | VDDA   | Standby Mode (STBY),<br>I <sub>LOAD</sub> < 100 μA, VBAT > 0.90 V   | 1.7 | 1.8 | 1.9 | V    | ~        |

|                |        | Low ïPower Mode (LPM),<br>I <sub>LOAD</sub> = 100 μA, VBAT > 0.92 V | 1.7 | 1.8 | 1.9 | V    |          |

|                |        |                                                                     |     |     |     |      | ~        |

#### BANDGAP REFERENCED REGULATOR TEMPERATURE STABILITY

| Parameter           | Symbol | Conditions                      | Min  | Тур | Max | Unit | Screened |

|---------------------|--------|---------------------------------|------|-----|-----|------|----------|

| Temperature Stabili | у      | Temperature range of ï5 to 50°C | ï0.5 | ï   | 0.5 | %    |          |

NOTE: Temperature stability for VREG, VDDA (LPM and HPM), VMIC, VDDOD, VDDC (using the band gap as reference) and VDDM (using the band gap as reference):

#### PMU REFERENCED REGULATOR TEMPERATURE STABILITY

| Parameter             | Symbol | Conditions                      | Min | Тур | Max | Unit | Screened |

|-----------------------|--------|---------------------------------|-----|-----|-----|------|----------|

| Temperature Stability |        | Temperature range of ï5 to 50°C | ï2  | ï   | 2   | %    |          |

NOTE: Temperature stability for VDDA (STBY), VDDC (using the PMU as reference) and VDDM (using the PMU as reference):

#### POWER ION IRESET

| Description                                  | Symbol              | Conditions | Min  | Тур  | Max  | Unit | Screened |

|----------------------------------------------|---------------------|------------|------|------|------|------|----------|

| VBAT startup voltage: High threshold voltage | Vth <sub>High</sub> |            | 0.68 | 0.77 | 0.86 | V    | >        |

| VBAT shutdown voltage: Low threshold voltage | Vth <sub>Low</sub>  |            | 0.63 | 0.72 | 0.81 | V    | *        |

NOTE: Typical time duration between application of VBAT and first NVM access: 77 ms

#### **INPUT STAGE**

| Parameter                                   | Symbol              | Conditions                                                       | Min | Тур | Max             | Unit  | Screened |

|---------------------------------------------|---------------------|------------------------------------------------------------------|-----|-----|-----------------|-------|----------|

| Nominal input referred noise 16 kHz SF, RMS | IN <sub>IRN</sub>   | A ïweighted 100 Hz ï8 kHz, 16 kHz SF, nominal current setting    | ï   | 2   | 4               | μVrms |          |

| Nominal input referred noise 32 kHz SF, RMS |                     | A ïweighted 100 Hz ï16 kHz, 32 kHz SF, maximum current setting   | ï   | 3   | 10<br>(Note 11) | μVrms | ~        |

| HiQ input referred noise<br>16 kHz SF, RMS  |                     | A ïweighted 100 Hz ï8 kHz, 16 kHz SF, maximum current setting    | ï   | 1.5 | 3               | μVrms |          |

| HiQ input referred noise<br>48 kHz SF, RMS  |                     | A ïweighted 20 Hz ï20 kHz, 48 kHz<br>SF, maximum current setting | ï   | 3   | 10<br>(Note 12) | μVrms | ~        |

| Nominal dynamic range                       | IN <sub>DR</sub>    | A ïweighted 100 Hz ï8 kHz, nominal current setting               | ï   | 109 | ï               | dB    |          |

| HiQ dynamic range                           |                     | A ïweighted 100 Hz ï8 kHz, maximum current setting               | ï   | 112 | ï               | dB    |          |

| Input range                                 | IN <sub>RANGE</sub> | At VDDA 1.8 V                                                    | 0   | ï   | 1.6             | V     |          |

#### IOs

| Parameter                             | Symbol                 | Conditions                                                                                                                                | Min                | Тур | Max  | Unit                                               | Screened |

|---------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|------|----------------------------------------------------|----------|

| Strong pull ïup<br>Impedance          | IMP <sub>SUP</sub>     |                                                                                                                                           | 0.8                | 1   | 1.2  | kΩ                                                 | ~        |

| Pad Input Delay                       | IN <sub>DELAY</sub>    | VDDO=1.8V                                                                                                                                 | ï                  | ï   | 0.76 | ns                                                 |          |

|                                       |                        | VDDO=1.2V                                                                                                                                 | ï                  | ï   | 1.23 | ns                                                 |          |

| Pad Output Delay                      | OUT <sub>DELAY</sub>   | VDDO=1.8V<br>1x drive strength, 1 pF load<br>2x drive strength, 2 pF load<br>4x drive strength, 4 pF load<br>8x drive strength, 8 pF load | ï                  | ï   | 1.24 | ns                                                 |          |

|                                       |                        | VDDO=1.2V<br>1x drive strength, 1pF load<br>2x drive strength, 2 pF load<br>4x drive strength, 4 pF load<br>8x drive strength, 8 pF load  | ï                  | Ï   | 1.74 | ns                                                 |          |

| Drive Strength                        | DRIVE                  | Configurable with 1x, 2x, 4x, 8x<br>Nominal drive strength: 1 mA                                                                          | 1                  | Ï   | 8    | Multiple<br>of the<br>nominal<br>drive<br>strength |          |

| Max Switching<br>Frequency            | IOFR <sub>Max</sub>    |                                                                                                                                           | Maximum<br>SYS_CLK | ï   | ï    |                                                    |          |

| Glitch filter : additional rise delay | DELAY <sub>RAISE</sub> |                                                                                                                                           | ï                  | Ï   | 169  | ns                                                 |          |

| Glitch filter : additional fall delay | DELAY <sub>FALL</sub>  |                                                                                                                                           | Ϊ                  | ï   | 245  | ns                                                 |          |

NOTE: DC Characteristics of the digital pad at VDDO 1.08/1.8/1.98V NOTE: The glitch filter cuts glitches with duration shorter than 50 ns

#### CURRENT CONTROLLED OSCILLATOR (CCO)

| Parameter                               | Symbol  | Conditions                                                                   | Min  | Тур  | Max   | Unit | Screened |

|-----------------------------------------|---------|------------------------------------------------------------------------------|------|------|-------|------|----------|

| Recommended Working Frequency           | SYS_CLK | For recommended VDDC and VDDM                                                | 2.56 | ï    | 61.44 | MHz  |          |

| Boot frequency                          | SYS_CLK |                                                                              | 5    | 7.68 | 10    | MHz  | ~        |

| Oscillator frequency trimming precision |         |                                                                              | ï    | 0.10 | 0.20  | %    |          |

| Frequency stability in temperature      |         | Temp: 0°C and 50°C.<br>After calibration at room<br>temperature (25°C)       | ï1.5 | Ϊ    | 1.5   | %    |          |

|                                         |         | Temp: ï40°C and 85°C.<br>After calibration at room<br>temperature (25°C)     | ï4   | Ϊ    | 4     | %    |          |

| Period jitter (rms)                     |         | RMS, at 5.12 MHz, before multiplication                                      | ï    | ï    | 200   | ps   |          |

|                                         |         | RMS, at 5.12 MHz,<br>after multiplied by 2 and divided<br>by a multiple of 2 | Ï    | Ϊ    | 200   | ps   |          |

|                                         |         | RMS, at 5.12 MHz,<br>after multiplied by 4 and divided<br>by a multiple of 4 | Ϊ    | Ϊ    | 200   | ps   |          |

| Output duty cycle                       |         | With multiplier setting 1x or 2x                                             | 45   | ï    | 55    | %    |          |

|                                         |         | With multiplier setting 4x                                                   | 40   | Ϊ    | 60    | %    |          |

| Max frequency                           |         | Un ïmultiplied                                                               | ï    | 30   | ï     | MHz  |          |

#### LOW DELAY PATH (using the low delay path of the Filter Engine)

| Parameter              | Symbol | Conditions                            | Min | Тур  | Max | Unit | Screened |

|------------------------|--------|---------------------------------------|-----|------|-----|------|----------|

| Analog to analog delay |        | Fs = 48 kHz<br>FENG delay: one sample | Ϊ   | 10.4 | Ϊ   | S    |          |

#### NVM (LE25S161)

| Description                       | Symbol             | Conditions            | Min     | Тур | Max | Unit              | Sceened |

|-----------------------------------|--------------------|-----------------------|---------|-----|-----|-------------------|---------|

| Rewrite cylces, per Sector        | cyc <sub>RW</sub>  | Per LE25161 datasheet | 100'000 |     |     | Cycles/<br>Sector |         |

| Data Retention                    | t <sub>DRET</sub>  | Per LE25161 datasheet | 20      |     |     | year              |         |

| Program Mode<br>Operating Current | I <sub>CCPPL</sub> | Per LE25161 datasheet |         | 5   |     | mA                |         |

| Read Mode<br>Operating Current    | I <sub>CCR</sub>   | Per LE25161 datasheet |         | 3.5 |     | mA                |         |

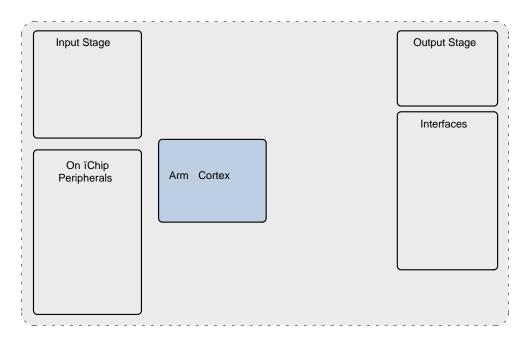

#### Ezairo 8310 System Diagram

Figure 1 is simplified diagram of the hybrid system that shows the major internal functional blocks and possible external

#### ARCHITECTURE OVERVIEW

The Ezairo 8300 system is an asymmetriccobe architecture, mixeosignal systemion ichip designed specifically for the audio processing needs uiltower power portable devices. It centers around 6 processing cores: the CFX Digital Signal Processor (DSP), the Arm Cortexima Processor, the LPDSP32 Digital Signal Processor (DSP), the HEAR Configurable Accelerator, the Filter Engine and the Neural Network Accelerator.

#### **CFX DSP Core**

The CFX DSP is a useprogrammable generapurpose DSP core that uses a 254t fixed i

- € Feedback cancellation

- € Noise reduction

To execute these and other algorithm is in the HEAR excels at the following:

- € Processing using a weighted overlap add (WOLA) filterbank

- € Time domain filtering

- € Subband filtering

- € Attack/release filtering

- € Vector addition/subtraction/multiplication

- € Signal statistics (such as average, variance and correlation)

#### Filter Engine

The Filter Engine is a core that provides lidelay path and basic filtering capabilities for the Ezairo 8300 system.

The Filter Engine can implement filters (either FIR or IIR) with a total of up to 320 coefficients. FIR filters are implemented using a direitorm structure. IIR filters are implemented with a cascade of sections (biquads), each implemented as a director I filter.

The Filter Engine is programmable, but does not include direct debugging access. TIQFX and the Arm CorteXM3 controland configuration registers on the program memory multiplexing options available in the Ezairo 8300 system. bus.

#### LPDSP32 DSP

LPDSP32 is a Oprogrammable, 32bit DSP developed by onsemi LPDSP32 is a high fediency, dual Harvard DSP that supports both single (3/2it) and double precision (64 ïbit) arithmetic.

LPDSP32's dual MAC unit, load store architecture is specifically optimized to support audio processing tasks configurable channels. such as audio codecs that might be required for wireless Input Stage: The input stage of an Ezairo 8300 provides audio communication tasks, Artificial Intelligence (AI) functions, and other advanced developments requiring theof the Ezairo 8300 system. additional processing power that this core provides. The Output Stage: The output stage of Ezairo 8300 provides advanced architecture also provides:

- € Two 72ïbit ALUs capable of doing single and double precision arithmetic and logical operations

- € Two 32 ibit integer/fractional multipliers

- € Four 64ïbit accumulators with 8bit overflow (extension bits)

The LPDSP32 relies on the CFX DSP or the Arm CortexïM3 processor to initialize its memories and peripherals. Oncientialized, the CFX DSP and/or the Arm CortexïM3 processor control the LPDSP32 DSP's execution state.

Software development on the LPDSP32 is done in C.

#### Neural Network Accelerator (NNA)

The Neural Network Accelerator (NNA) is a hardware accelerator block that allows complex neural networks to run in an energy efficient manner. The accelerator can

execute a single layer of a fully populated or sparsely populated neural network in a single task without any processor intervention. Layers with up to 1023 inputs and 1023 outputs are supported.

The NNA contains 16 multipliers, 16 accumulators, 16 input registers and 16 coefficient registers. It includes input and coefficient "fetchers" that, once configured, manage the data and coefficients memory access automatically. Support for coefficient compression/ decompression and pruning is included and help minimize the amount of coefficient needed.

Other key components of the Ezairo 8300 are:

Memory systems: The memory systems provided by the Ezairo 8300 system are constructed using a number of memories (memory instances), memory buses, memory controllers and memory arbiters. The seemories and other memoryïmappedelements are addressable from the CFX DSP and the Arm CortexM3 processor through a set of memory spaces (also known as address spaces).

FIFO Controller: The Ezairo 8300 system's FIFO controller provides the ability to define up to 32 FIFO buffers.

Input/Output Controllers (IOC): The IOCs are responsible for handling input/output audio data. Samples Processor can monitor the Filter Engine state throughcan be routed along a number of different paths using the

> Direct Memory Access (DMA) Controller: The direct memory access controller (DMA) module allows backgroundransfers between components the peripheral bus (referred to in this section as peripherals) and memories without any processor intervention. This allows the processors to be used for other computational needs while enabling high speed sustained transfers to and from the peripherals/memories. The DMA has 8 independent

> four audio input channels that supply signal data to the rest

two audio output channels that pigstocess signal data from the rest of the Ezairo 8300 system, and provide it to external receivers or speakers.

General Purpose Input/Output (GPIO) Pads: The Ezairo 8310 system offers 20 general purpose input/output (GPIO) pads that can be configured:

- € To support the external interfaces, output clocks, and other I/Os

- € As generalipurpose I/Os (GPIO)

- € Analog input/output function

The 20 GPIOs are split into four power domains. The voltages for these 4 power domains are given by:

€ VDDO1 (GPIO5, GPIO7 to GPIO11) is supplied by VDDIF

#### Ezairo 8310 HYBRID INTERFACE SPECIFICATIONS

| EZAIIO 0310 FT BRID INTERFACE SPECIFICATIONS                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A total of 49 pads are present on the Ezairo 8310 hybrid. These pads are the interfaces between the hybrid and the other components in the hearing aid. They are listed in the table below. |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

|                                                                                                                                                                                             |

| Ball Number | Hybrid Pad Name | Hybrid Pad Description                    |

|-------------|-----------------|-------------------------------------------|

| D10         | VBATOD          | Output driver power supply                |

| E1          | Al2             | ADC analog input 2                        |

| E2          | Al1             | ADC analog input 1                        |

| E3          | AI0             | ADC analog input 0                        |

| E5          | RCVR0P          | Output Driver: Receiver Output 0 Positive |

| E6          | RCVR0N          | Output Driver: Receiver Output 0 Negative |

| E7          | RCVR1P          | Output Driver: Receiver Output 1 Positive |

| E8          | RCVR1N          | Output Driver: Receiver Output 1 Negative |

| E9          | SCL             | Debug port clock                          |

| E10         | VSSOD           | Output driver ground                      |

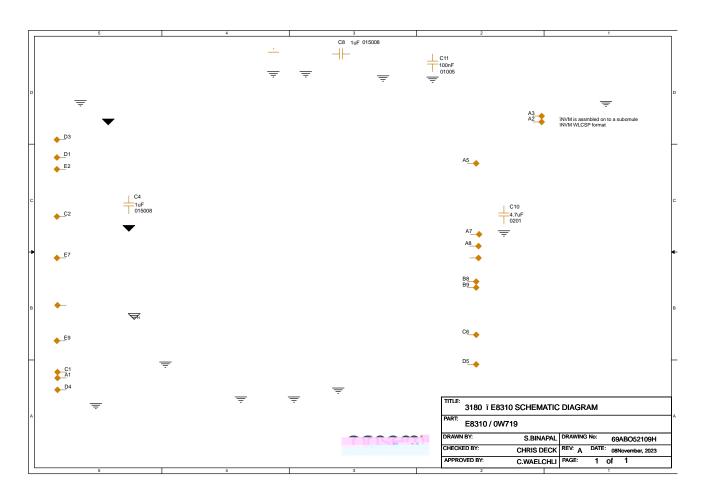

Figure 2. Ezairo 8310 Hybrid Schematics

Packaging and Manufacturing

- € Ultra iminiature formfactor: suitable for all hearing aid styles including CIC, ITE, RITE, BTE, and mirBTE.

- € Reïflowable: the Ezair&310 hybrid is reflowable onto FR4 and other substrates.

- € RoHS compliant: the Ezairo 8310 hybrid complies with the RoHS directive.

#### System Identification

System identification is used to identify different system componentsThis information can be retrieved using any of the supported communication box and protocol software provided byonsemi

For the Ezairo 8300 chip, the key identifier components and values are as follows:

€ Chip Family: 0x0A € Chip Version: 0x01 € Chip Revision: 0x0101

NVM at addres@x00F1to 0x00F2(2 bytes => 16 bits).

€ Hybrid ID: 0x00A0

#### Solder Information

The Ezairo 8310 hybrid is constructed with all RoHS compliant material with bump metallization of SAC305

(Sn96.5/Ag3.0/Cu0.5) solder and should therefore be reflowed accordingly. This hybrid device is Moisture Sensitive Class MSL3, 260 and must be stored and handled accordingly. For soldering guidelines, please refer to the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D). Hand soldering is not recommended for this part.

#### Electrostatic Discharge (ESD) Device

CAUTION: ESD sensitive device. Permanent damage may occur on devices subjected to highergy electrostatic dischargesProper ESD precautions in handling, packaging and testing are recommended to avoid performance degradation or loss of functionality.

#### **Development Tools**

A full suite of comprehensive tools is available to assist softwaredevelopers from the initial concept and technology assessment through to prototyping and product launch.

Application development and communication tools, as The hybrid ID can be found in the manufacturing area of the well as ar Evaluation and Developme Kitt (EDK) facilitate the development of advanced algorithms on the Ezairo 8310 hybrid.

EZAIRO is a registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/ or other countries

Arm, Cortex, and the Arm logo are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere.

# PACKAGE DIMENSIONS

SIP49 3.00x5.25 CASE 127FH ISSUE A

RE