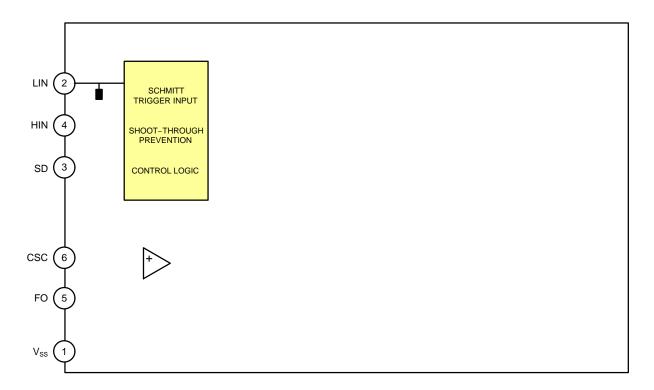

## **BLOCK DIAGRAM**

## **SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25 C, unless dtherwise specified.)

| Symbol              | Rating                                           |         | Value                              | Unit |

|---------------------|--------------------------------------------------|---------|------------------------------------|------|

| VS                  | High-side Offset Voltage V <sub>S</sub>          |         | $(V_{B} - 25)$ to $(V_{B} + 0.3)$  | V    |

| VB                  | High-side Floating Supply Voltage V <sub>B</sub> |         | -0.3 to 1225                       | V    |

| V <sub>HO</sub>     | High-side Floating Output Voltage                |         | $(V_{S} - 0.3)$ to $(V_{B} + 0.3)$ | V    |

| V <sub>DD</sub>     | Low-side and Logic-fixed Supply Voltage          |         | -0.3 to 25                         | V    |

| V <sub>IN</sub>     | Logic Input Voltage (HIN, LIN, SD)               |         | –0.3 to (V <sub>DD</sub> + 0.3)    | V    |

| V <sub>CSC</sub>    | Current Sense Input Voltage                      |         | –0.3 to (V <sub>DD</sub> + 0.3)    | V    |

| dV <sub>S</sub> /dt | Allowable Offset Voltage Slew Rate               |         | 50                                 | V/ns |

| PD                  | Power Dissipation (SO14NB) (Note 1)              |         | 0.8                                | W    |

| JA                  | Thermal Resistance, Junction-to-Ambient (S       | SO14NB) | 156                                | C/W  |

| T <sub>J(max)</sub> | Junction Temperature                             |         | +150                               | С    |

| TSTG                | Storage Temperature                              |         | -55 to +150                        | С    |

| ESDHBM              | ESD, Human Body Model (Note 3)                   |         | 2500                               | V    |

| ESDCDM              | ESD, Charged Device Model (Note 3)               |         | 750                                | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Do not exceed PD under any circumstances.

Do not exceed PD under any circumstances.

Mounted on 76.2 114.3 1.6 mm PCB (FR-4 glass epoxy material). Refer to the following standards:

JESD51-2: Integral circuits thermal test method environmental conditions – natural convection

JESD51-3: Low effective thermal conductivity test boars for leaded surface mount packages

This device series incorporates ESD protection and is test of by the following methods:

ESD Human Body Model tested per ANSI/ESDA/JEDE0 JS-001-2012

ESD Charged Davies Model tested per LESD22 C101

- ESD Charged Device Model tested per JESD22-C101

#### RECOMMENDED OPERATING RANGES (Parameters are referenced to V<sub>SS</sub>)

|                 | II                                                   | 11          |                     |                |      |

|-----------------|------------------------------------------------------|-------------|---------------------|----------------|------|

| Symbol          | Rating                                               |             | Min                 | Max            | Unit |

| V <sub>DD</sub> | Supply Voltage Range                                 |             | 4.5                 | 18.0           | V    |

| VS              | High-Side V <sub>S</sub> Floating Supply Offset Volt | ge (Note 4) | 5 – V <sub>BS</sub> | 1200           | V    |

| V <sub>BS</sub> | High-side V <sub>BS</sub> Bootstrap Voltage          |             | V <sub>BSUV+</sub>  | 22             | V    |

| V <sub>HO</sub> | High-Side Output Voltage                             |             | V <sub>S</sub>      | V <sub>B</sub> | V    |

| V <sub>DD</sub> | Low-Side and Logic Supply Voltage                    |             | V <sub>DDUV+</sub>  | 22             | V    |

$V_{h}$

#### ELECTRICAL CHARACTERISTICS

$(V_{BIAS} (V_{DD}, V_{BS}) = 15 \text{ V}, T_A = -40 \text{ C}$  to 125 C unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to V

#### ELECTRICAL CHARACTERISTICS (continued)

$(V_{BIAS} (V_{DD}, V_{BS}) = 15 \text{ V}, \text{ T}_{A} = -40 \text{ C}$  to 125 C unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$ . The  $V_{O}$  and  $I_{O}$  parameters are referenced to  $V_{S}$  and COM and are applicable to the respective outputs HO and LO.)

| Symbol           | Parameter                       | Test Conditions                                 | Min | Тур | Max | Unit |

|------------------|---------------------------------|-------------------------------------------------|-----|-----|-----|------|

| FAULT DETE       | CTION SECTION                   |                                                 |     |     |     |      |

| V <sub>FOH</sub> | Fault Output High Level Voltage | $V_{CSC}$ = 0 V, $R_{PULL-UP}$ = 4.7 k $\Omega$ | 4.7 | -   | -   | V    |

| V <sub>FOL</sub> | Fault Output Low Level Voltage  | $V_{CSC} = 1 \text{ V}, I_{FO} = 2 \text{ mA}$  | -   | -   | 0.8 | V    |

#### DYNAMIC OUTPUT SECTION

$(V_{BIAS} (V_{DD}, V_{BS}) = 15.0 \text{ V}, T_A = -40 \text{ C}$  to 125

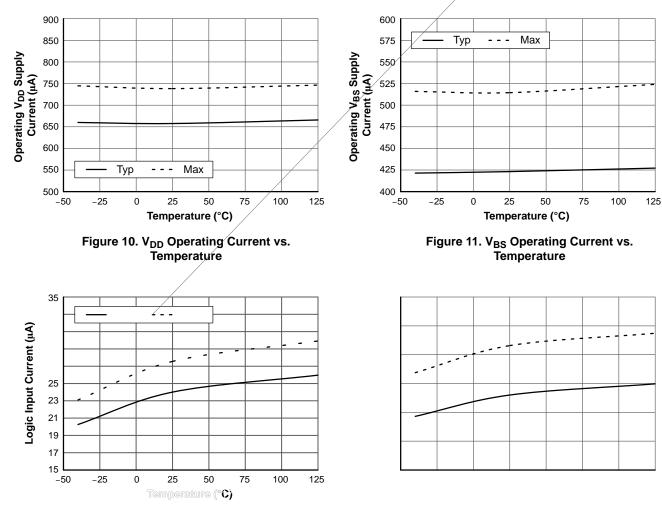

## TYPICAL CHARACTERISTICS (Continued)

Figure 12. Logic High Input Bias Current vs. Temperature

Figure 14. I<sub>SOFT</sub> vs. Temperature

Figure 13. I<sub>CSCIN</sub> vs. Temperature

Figure 15. Turn-on Rising Time vs. Temperature

# TYPICAL CHARACTERISTICS (Continued)

| <br> | <br> | <br> |  |

|------|------|------|--|

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

| <br> | <br> | <br> |  |

|------|------|------|--|

|      | <br> |      |  |

|      |      |      |  |

|      | <br> |      |  |

|      | <br> |      |  |

|      |      |      |  |

| <br> | <br> | <br> |  |

|------|------|------|--|

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

| <br> | <br> | <br> |  |

# TYPICAL CHARACTERISTICS (Continued)

| <br> | <br> | <br> |  |

|------|------|------|--|

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|  |      | <br> |  |

|--|------|------|--|

|  | <br> |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

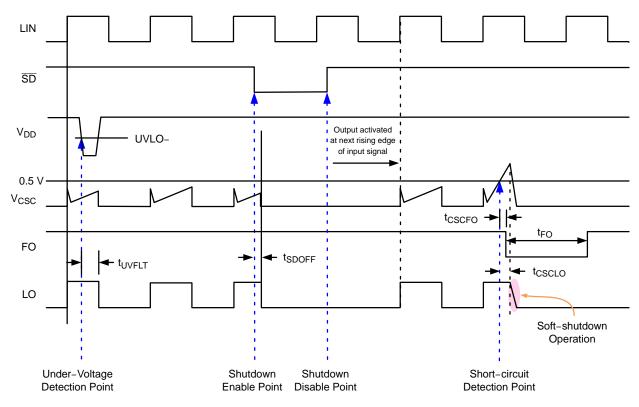

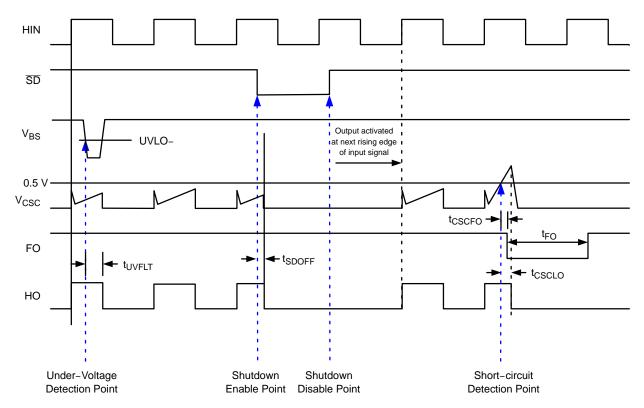

Figure 43. Switching Timing Waveforms Definition – High Side

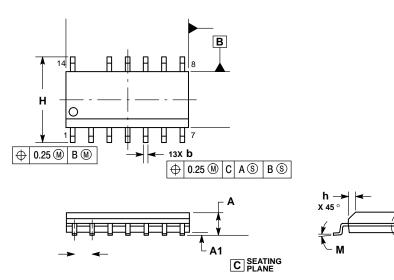

SOIC 14 NB CASE 751A-03 ISSUE L

DATE 03 FEB 2016

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

5. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

SIDE.

#### GENERIC **MARKING DIAGRAM\***

| 14 | A | Ħ  | Ħ  | Ħ   | A  | A  | <u> </u> |

|----|---|----|----|-----|----|----|----------|

|    |   | xx | хх | хх  | хх | XG |          |

|    | 0 | A  | ٩W | LY۱ | NΝ | /  |          |

| 1  | H | H  | H  | H   | H  | H  | Ъ        |

| XXXXX | = Specific Device Code |

|-------|------------------------|

| A     | = Assembly Location    |

| WL    | = Wafer Lot            |

| Y     | = Year                 |

| WW    | = Work Week            |

| G     | = Pb-Free Package      |

## **STYLES ON PAGE 2**

DATE 03 FEB 2016

STYLE 7: PIN 1. ANODE/CATHODE 2. COMMON ANODE 3. COMMON CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi