se

- ΧХ = Specific Device Number

- ZZ = Lot Code

А

- Μ = Date Code

- = Assembly Site Code = Pb Free. WLCSP are Pb–Free.

## Table 1. ORDERING INFORMATION

| Part Number    | V <sub>FLOAT</sub> (V) | Specific Device<br>Number Marking (XX) | Package               | Packing Method <sup>†</sup> |

|----------------|------------------------|----------------------------------------|-----------------------|-----------------------------|

| FAN54120MP420X | 4.20                   | 20                                     | DFN6, 2x2 mm          | 3000 / Tape & Reel          |

| FAN54120MP425X | 4.25                   | 25                                     | (Pb Free)             |                             |

| FAN54120MP435X | 4.35                   | 35                                     |                       |                             |

| FAN54120UC420X | 4.20                   | V4                                     | WLCSP-6, 1.36x0.76 mm | 3000 / Tape & Reel          |

| FAN54120UC425X | 4.25                   | V5                                     | (Pb Free)             |                             |

| FAN54120UC435X | 4.35                   | V6                                     |                       |                             |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

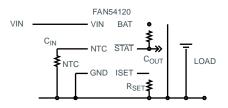

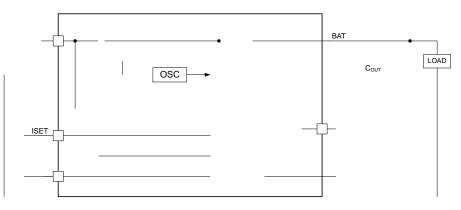

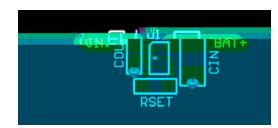

## **BLOCK DIAGRAM**

Figure 2. Simplified Block Diagram

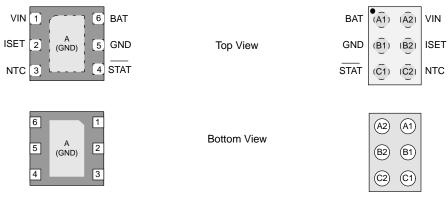

# **PIN CONNECTIONS**

## Table 3. PIN DEFINITIONS

| DFN Pin | WLCSP Pin | Pin Name | Description                                                                                                                                                                                        |

|---------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | A2        | VIN      | Input Voltage. Connect CIN bypass directly to VIN and GND pins on top layer.                                                                                                                       |

| 2       | B2        | ISET     | Set Charge Current. Connect $R_{SET}$ directly to GND to set the maximum input/charging current (I_{FAST}).                                                                                        |

| 3       | C2        | NTC      | NTC input. Connect to battery pack NTC to provide JEITA "safe-charging" functionality. See "NTC Pin" applications section for additional usage information.                                        |

| 4       | C1        | STAT     | Status. Open-drain output used to indicate charge and/or fault status. Internally, there is a weak pull-up ( $R_{\overline{STAT}}$ ) to BAT. This pin is also used to enable Power Back operation. |

| 5, A    | B1        | GND      | Ground. Connect to system GND plane. $C_{\rm IN}$ and $C_{\rm OUT}$ also connect directly to this pin on top layer.                                                                                |

| 6       | A1        | BAT      | Output. Connect to system load and positive terminal of battery. Bypass with $C_{\text{OUT}}, \ \text{connected directly to BAT}$ and GND pins on top layer.                                       |

#### Table 4. ABSOLUTE MAXIMUM RATINGS

| Symbol               | Parameter                                                     |      | Max      | Unit   |

|----------------------|---------------------------------------------------------------|------|----------|--------|

| V <sub>IN</sub>      | Voltage on VIN Pin                                            | -1.2 | 28.0     | V      |

| V <sub>IN_SLEW</sub> | VIN Rise Time, $V_{IN} > 6 V$                                 |      | 10       | V/µsec |

| V <sub>BAT</sub>     | Voltage on BAT Pin                                            | -0.3 | 6.3      | V      |

| V <sub>X</sub>       | Voltage on All Other Pins                                     | -0.3 | (Note 3) | V      |

| ESD                  | Electrostatic Discharge Protection Level, HBM per JESD22–A114 |      | 1500     | V      |

|                      | Electrostatic Discharge Protection Level, CDM per JESD22–C101 |      | 2000     | V      |

| LU                   | Latch Up per JESD78, Class I, 25 C                            |      | 100      | mA     |

| Т <sub>Ј</sub>       | Junction Temperature                                          | -40  | +150     | С      |

| T <sub>STG</sub>     | Storage Temperature                                           | -65  | +150     | С      |

| T <sub>LS</sub>      | Lead Soldering Temperature, 10 Seconds                        |      | +260     | С      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these

## Table 5. RECOMMENDED OPERATING CONDITIONS

| Symbol           | Parameter            | Min | Max  | Unit |

|------------------|----------------------|-----|------|------|

| V <sub>IN</sub>  | Voltage on VIN Pin   | 4   | 6    | V    |

| V <sub>BAT</sub> | Battery Voltage      | 2.5 | 4.5  | V    |

| T <sub>A</sub>   | Ambient Temperature  | -30 | +85  | С    |

| TJ               | Junction Temperature | -30 | +120 | С    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

NOTE: The Recommended Operating Conditions table defines the conditions for actual device operation using the circuit of Figure 1, with the Recommended External Components shown in Table 2. Recommended operating conditions are specified to ensure

| Table 7. ELECTRICAL CHARACTERISTICS (Unless otherwise specified, circuit of Figure 1 with VIN = 5.0 V, VFLOAT = 4.2 V,                       |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{BAT}$ = 3.9 V, $R_{SET}$ = 1.0 k $\Omega$ , over recommended $T_A$ operating temperature range. Typical values are at 25 C.) (continued) |

| Symbol                     | Parameter                            | Condition                                         | Min | Тур | Max | Unit |

|----------------------------|--------------------------------------|---------------------------------------------------|-----|-----|-----|------|

| CHARGER VOLTAGE REGULATION |                                      |                                                   |     |     |     |      |

| V <sub>BATMIN</sub>        | Pre-to-Fast Charge Threshold         | Rising V <sub>BAT</sub>                           | 2.9 | 3.1 | 3.3 | V    |

| V <sub>RCH</sub>           | Battery Recharge Indicator Threshold | V <sub>BAT</sub> Falling Below V <sub>FLOAT</sub> |     |     |     |      |

| Table 7. ELECTRICAL CHARACTERISTICS (Unless otherwise specified, circuit of Figure 1 with VIN = 5.0 V, VFLOAT = 4.2 V,                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>BAT</sub> = 3.9 V, R <sub>SET</sub> = 1.0 k $\Omega$ , over recommended T <sub>A</sub> operating temperature range. Typical values are at 25 C.) (continued) |

| Symbol                | Parameter                                       | Condition              | Min | Тур              | Max | Unit                   |

|-----------------------|-------------------------------------------------|------------------------|-----|------------------|-----|------------------------|

| THERMAL PR            | ROTECTION                                       | •                      |     |                  |     |                        |

| I <sub>TREG</sub>     | Adaptive Thermal Regulation Foldback (Note 7)   |                        | 40  |                  | 80  | %<br>I <sub>FAST</sub> |

| T <sub>SDOWN</sub>    | Thermal Shutdown Threshold<br>(Note 7) (Note 8) | $T_J$ Rising           | 130 | 145              | 160 | С                      |

|                       | Hysteresis(Note 7)                              | T <sub>J</sub> Falling |     | T <sub>REG</sub> |     | С                      |

| t <sub>TSD_QUAL</sub> | Thermal Shutdown Qualification Time (Note 7)    | $T_J$ Rising           |     | 1                |     | msec                   |

| t <sub>DIE_T</sub>    | Die Temperature Sampling Rate (Note 7)          |                        |     | 32               |     | msec                   |

| TIMERS                |                                                 |                        |     |                  |     |                        |

| toos oo               | Pre_Charge Fault Timer (Note 7)                 |                        |     | 32               |     | msac                   |

| tPRE_SC               | Pre-Charge Fault Timer (Note 7)          |                                |     | 32 |     | msec | l |

|-----------------------|------------------------------------------|--------------------------------|-----|----|-----|------|---|

| tosc                  | Internal Oscillator Accuracy             | Applies to All Timers/Counters | -15 |    | +15 | %    | 1 |

| t <sub>IN_REVAL</sub> | Input Re–Validation Attempt Period (Note |                                |     |    |     |      |   |

## TYPICAL CHARACTERISTIC

Unless otherwise specified, circuit of Figure 1 with V<sub>IN</sub> = 5.0 V, V<sub>FLOAT</sub> = 4.2 V, V<sub>BAT</sub> = 3.8 V, R<sub>SET</sub> = 1.0 k $\Omega$ , T<sub>A</sub> = 25 C.

Figure 5. Sleep Mode Discharge Current

Figure 6. Start–Up VIN Insertion,  $V_{BAT}$  = 3.8 V

Figure 7. Start–Up at VIN Insertion,  $V_{BAT}$  = 2.9 v

Figure 8. Power Back Mode Quiescent Current

## **OPERATION / APPLICATION INFORMATION**

$\begin{array}{l} \mbox{ISET Pin} \mbox{-} Setting the Charge Current (I_{FAST}) \\ R_{SET}, \mbox{ connected to the ISET pin, is used to establish the maximum charging current (I_{FAST}) \end{array}$

During the pre conditioning stage (Pre Charge), a constant current  $I_{PRE}$   $(I_{FAST}$

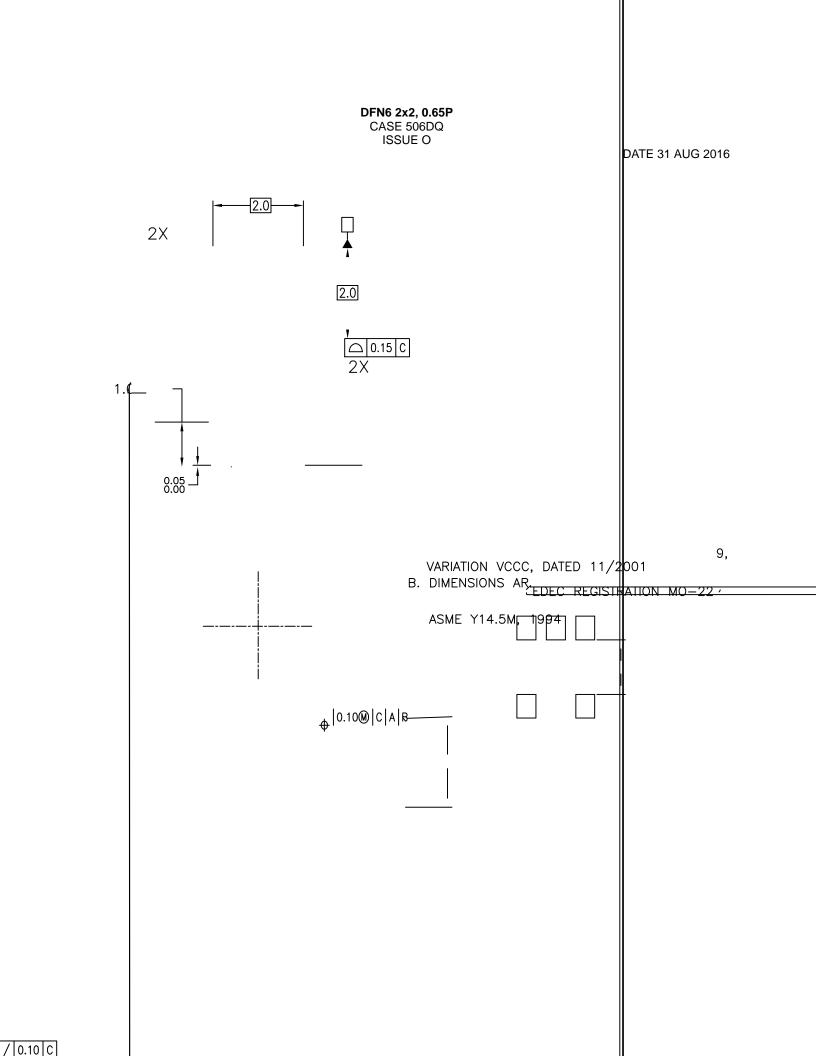

## PCB Layout Guideline

Figure 11. Example Layout, FAN54120MP (DFN)

Place  $C_{IN}$  and  $C_{OUT}$  as close possible to the IC. Connect the capacitors directly to the appropriate IC pins on the top layer. Reference the circuit to the system GND plane, typically on an inner layer, using a via in the IC DAP and/or at the GND side of  $C_{OUT}$ . The GND side of  $R_{SET}$  should be routed with a trace directly to IC GND, rather than using a via to the GND plane. This prevents transient currents in GND plane from influencing the IC's current regulation.

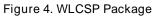

The same practices should be applied to the WLCSP version. Due to the lack of a DAP on the CSP, the GND side of  $C_{IN}$  should be connected by via to the system GND plane.

Figure 12. Example Layout, FAN54120UC (CSP)

# semi

| NT NUMBER:  | 98AON02370H            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| ESCRIPTION: | WLCSP6 1.36x0.76x0.581 |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

|             |                        |                                                                                                                                                                                     |             |  |  |

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi