Is Now Part of

## To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="mailto:www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild\_questions@onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number

April 2013

# FDMF6823A — Extra-Small, High-Performance, High-Frequency DrMOS Module

### **Benefits**

- Ultra-Compact 6x6 mm PQFN, 72% Space-Saving Compared to Conventional Discrete Solutions

- Fully Optimized System Efficiency

### **Absolute Maximum Ratings**

Stresses exceeding the Absolute Maximum Ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             | Parameter                       |                    | Min. | Max. | Unit |

|--------------------|---------------------------------|--------------------|------|------|------|

| V <sub>CIN</sub>   | Supply Voltage                  | Referenced to CGND | -0.3 | 6.0  | V    |

| $V_{DRV}$          | Drive Voltage                   | Referenced to CGND | -0.3 | 6.0  | V    |

| V <sub>DISB#</sub> | Output Disable                  | Referenced to CGND | -0.3 | 6.0  | V    |

| V <sub>PWM</sub>   | PWM Signal Input                | Referenced to CGND | -0.3 | 6.0  | V    |

| V <sub>SMOD#</sub> | Skip Mode Input                 | Referenced to CGND | -0.3 | 6.0  | V    |

| $V_{GL}$           | Low Gate Manufacturing Test Pin | Referenced to CGND | -0.3 | 6.0  | V    |

| V <sub>THWN#</sub> | Thermal Warning Flag            | Referenced to CGND | -0.3 | 6.0  | V    |

$\mathsf{V}_{\mathsf{IN}}$

| Symbol                        | Parameter                                       | Condition                                                                       | Min. | Тур. | Max. | Unit |

|-------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| Basic Oper                    | ation                                           |                                                                                 |      | •    |      |      |

| Ι <sub>Q</sub>                | Quiescent Current                               | I <sub>Q</sub> =I <sub>VCIN</sub> +I <sub>VDRV</sub> , PWM=LOW or HIGH or Float |      |      | 2    | mA   |

| V <sub>UVLO</sub>             | UVLO Threshold                                  | V <sub>CIN</sub> Rising                                                         | 2.9  | 3.1  | 3.3  | V    |

| $V_{\text{UVLO}\_\text{Hys}}$ | UVLO Hysteresis                                 |                                                                                 |      | 0.4  |      | V    |

| PWM Input                     | $(V_{CIN} = V_{DRV} = 5 V \pm 10\%)$            |                                                                                 |      |      |      |      |

| $R_{UP_{PWM}}$                | Pull-Up Impedance                               | V <sub>PWM</sub> =5 V                                                           |      | 10   |      | k    |

| $R_{DN_PWM}$                  | Pull-Down Impedance                             | V <sub>PWM</sub> =0 V                                                           |      | 10   |      | k    |

| $V_{\text{IH}_{\text{PWM}}}$  | PWM High Level Voltage                          |                                                                                 | 3.04 | 3.55 | 4.05 | V    |

| V <sub>TRI_HI</sub>           | 3-State Upper Threshold                         |                                                                                 | 2.95 | 3.45 | 3.94 | V    |

| $V_{TRI\_LO}$                 | 3-State Lower Threshold                         |                                                                                 | 0.98 | 1.25 | 1.52 | V    |

| VIL_PWM                       | PWM Low Level Voltage                           |                                                                                 | 0.84 | 1.15 | 1.42 | V    |

| t <sub>D_HOLD</sub> -OFF      | 3-State Shut-Off Time                           |                                                                                 |      | 160  | 200  | ns   |

| $V_{\text{HiZ}\_\text{PWM}}$  | 3-State Open Voltage                            |                                                                                 | 2.20 | 2.50 | 2.80 | V    |

| t <sub>PWM-OFF_MIN</sub>      | PWM Minimum Off Time                            |                                                                                 | 120  |      |      | ns   |

| PWM Input                     | (V <sub>CIN</sub> = V <sub>DRV</sub> = 5 V ±5%) |                                                                                 |      |      |      |      |

| $R_{UP_{PWM}}$                | Pull-Up Impedance                               | V <sub>PWM</sub> =5 V                                                           |      | 10   |      | k    |

| R <sub>DN_PWM</sub>           | Pull-Down Impedance                             | V <sub>PWM</sub> =0 V                                                           |      | 10   |      | k    |

| $V_{\text{IH}_{\text{PWM}}}$  | PWM High Level Voltage                          |                                                                                 | 3.22 | 3.55 | 3.87 | V    |

| V <sub>TRI_HI</sub>           | 3-State Upper Threshold                         |                                                                                 | 3.13 | 3.45 | 3.77 | V    |

| $V_{TRI\_LO}$                 | 3-State Lower Threshold                         |                                                                                 | 1.04 | 1.25 | 1.46 | V    |

| $V_{\text{IL}_{PWM}}$         | PWM Low Level Voltage                           |                                                                                 | 0.90 | 1.15 | 1.36 | V    |

| t <sub>D_HOLD-OFF</sub>       | 3-State Shut-Off Time                           |                                                                                 |      | 160  | 200  | ns   |

| Symbol                 | Parameter                                                | Condition                                                         | Min. | Тур. | Max. | Unit |

|------------------------|----------------------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| Thermal W              | arning Flag                                              |                                                                   | •    | •    |      | •    |

| T <sub>ACT</sub>       | Activation Temperature                                   |                                                                   |      | 150  |      | °C   |

| T <sub>RST</sub>       | Reset Temperature                                        |                                                                   |      | 135  |      | °C   |

| R <sub>THWN</sub>      | Pull-Down Resistance                                     | I <sub>PLD</sub> =5 mA                                            |      | 30   |      |      |

| 250 ns Tim             | eout Circuit                                             |                                                                   |      |      |      |      |

| t <sub>D_TIMEOUT</sub> | Timeout Delay                                            | SW=0 V, Delay Between GH from HIGH to LOW and GL from LOW to HIGH |      | 250  |      | ns   |

| High-Side I            | Driver (f <sub>sw</sub> = 1000 kHz, I <sub>out</sub> = 3 | 30 A, T <sub>A</sub> = +25°C)                                     |      |      |      | •    |

| RSOURCE GH             | Output Impedance, Sourcing                               | Source Current=100 mA                                             |      | 1    |      |      |

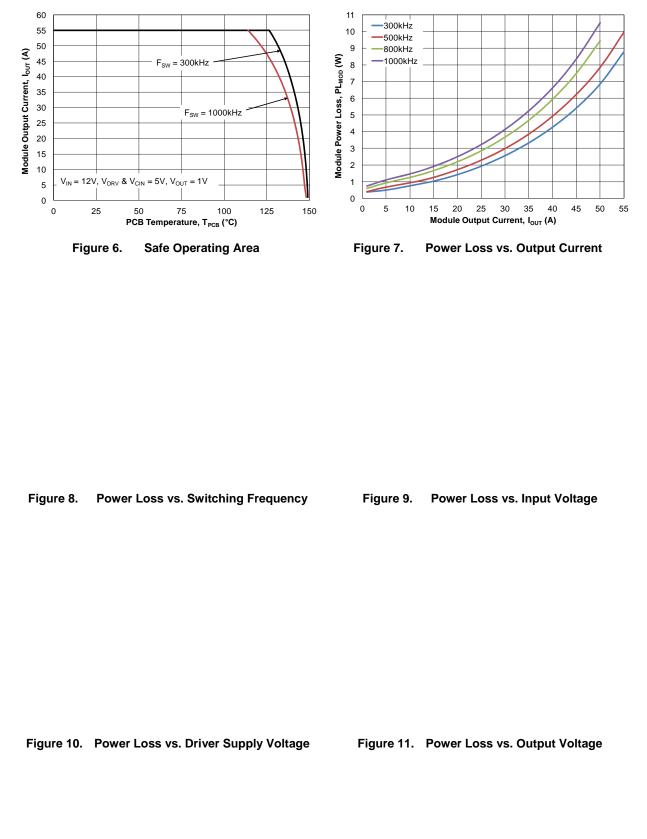

### **Typical Performance Characteristics**

Test Conditions:  $V_{IN}$ =12 V,  $V_{OUT}$ =1 V,  $V_{CIN}$ =5 V,  $V_{DRV}$ =5 V,  $L_{OUT}$ =250 nH,  $T_A$ =25°C, and natural convection cooling, unless otherwise specified.

© 2011 Fairchild Semiconductor Corporation FDMF6823A • Rev. 1.0.3

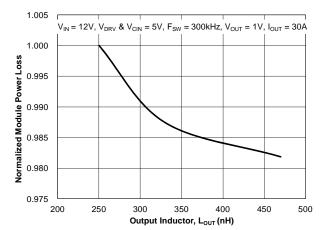

### **Typical Performance Characteristics**

Test Conditions:  $V_{IN}=12$  V,  $V_{OUT}=1$  V,  $V_{CIN}=5$  V,  $V_{DRV}=5$  V,  $L_{OUT}=250$  nH,  $T_A=25^{\circ}C$ , and natural convection cooling, unless otherwise specified.

Figure 12. Power Loss vs. Output Inductor

Figure 14. Driver Supply Current vs. Driver Supply Figure 15. Driver Supply Current vs. Output Current Voltage

Figure 16. UVLO Threshold vs. Temperature

Figure 17. PWM Threshold vs. Driver Supply Voltage

### **Typical Performance Characteristics**

Test Conditions: V<sub>CIN</sub>=5 V, V<sub>DRV</sub>=5 V, T

### **Functional Description**

The FDMF6823A is a driver-plus-FET module optimized for the synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each part is capable of driving speeds up to 1 MHz.

### VCIN and Disable (DISB#)

The VCIN pin is monitored by an Under-Voltage Lockout (UVLO) circuit. When V<sub>CIN</sub> rises above ~3.1 V, the driver is enabled. When V<sub>CIN</sub> falls below ~2.7 V, the driver is disabled (GH, GL=0). The driver can also be disabled by pulling the DISB# pin LOW (DISB# < V<sub>IL\_DISB</sub>), which holds both GL and GH LOW regardless of the PWM input state. The driver can be enabled by raising the DISB# pin voltage HIGH (DISB# > V<sub>IH\_DISB</sub>).

Table 1. UVLO and Disable Logic

| Driver State     |

|------------------|

| abled (GH, GL=0) |

|                  |

# HIGH, Q2 begins to turn off after a propagation delay

# FDMF6823A — Extra-Small, High-Performance, High-Frequency DrMOS Module

### Adaptive Gate Drive Circuit

The driver IC advanced design ensures minimum MOSFET dead-time, while eliminating potential shootthrough (cross-conduction) currents. It senses the state of the MOSFETs and adjusts the gate drive adaptively to ensure they do not conduct simultaneously. Figure 27 provides the relevant timing waveforms. To prevent overlap during the LOW-to-HIGH switching transition (Q2 off to Q1 on), the adaptive circuitry monitors the voltage at the GL pin. When the PWM signal goes (tpd phgll

### **Application Information**

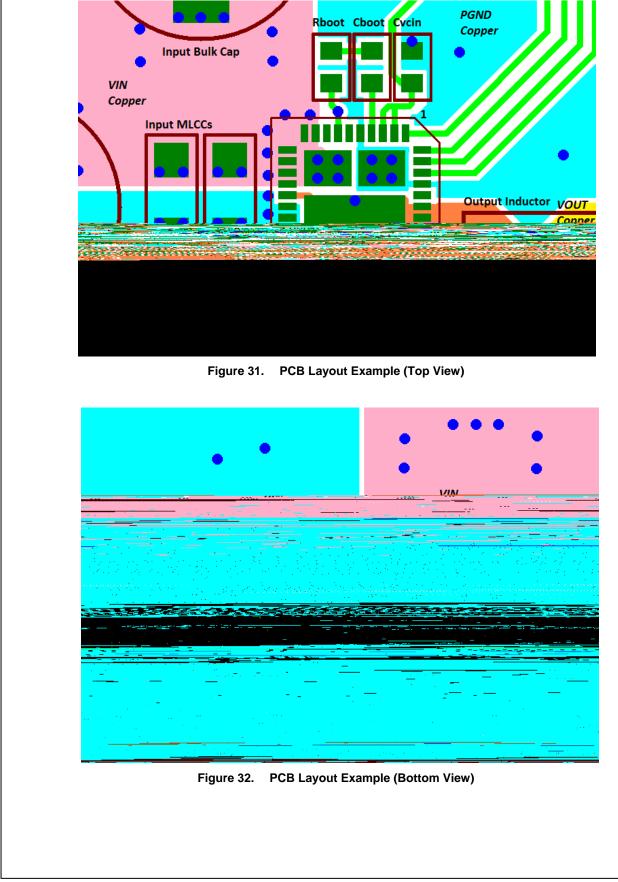

### Supply Capacitor Selection

For the supply inputs (V<sub>CIN</sub>), a local ceramic bypass capacitor is recommended to reduce noise and to supply the peak current. Use at least a 1  $\mu F$  X7R or X5R capacitor. Keep this capacitor close to the VCIN pin and connect it to the GND plane with vias.

**VCIN Filter**

### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor (C<sub>BOOT</sub>), as shown in Figure 30. A bootstrap capacitance of 100 nF X7R or X5R capacitor is usually adequate. A series bootstrap resistor may be needed for specific applications to improve switching noise immunity. The boot resistor may be required when operating above 15 V<sub>IN</sub> and is effective at controlling the high-side MOSFET turn-on slew rate and V<sub>SHW</sub> overshoot. R<sub>BOOT</sub> values from 0.5 to 3.0 are typically effective in reducing VSWH overshoot.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor roducts, "ripcical" parameters which may be provided in ON Semiconductor data sheets and/or dese sentor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or dese not convey any license under its patent rights or others. ON Semiconductor data sheets and/or is a specification s ustomer's technical experts. ON Semiconductor does not convey any license under its patent rights or others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor handles against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly any claim of personal injury or death associated with such unintended or unauthorized application. Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and

### PUBLICATION ORDERING INFORMATION