# Is Now Part of

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <u>www.onsemi.com</u>. Please email any questions regarding the system integration to <u>Fairchild questions@onsemi.com</u>.

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON

April 2017

## \_\_\_\_\_

# FNB51560TD1 Motion SPM<sup>®</sup> 55 Series

# Features

- UL Certified No. E209204 (UL1557)

- 600 V 15 A 3-Phase IGBT Inverter Including Control IC for Gate Drive and Protections

- Low-Loss, Short-Circuit Rated IGBTs

- Built-In Bootstrap Diodes in HVIC

- Separate Open-Emitter Pins from Low-Side IGBTs for Three-Phase Current Sensing

- Active-HIGH interface, works with 3.3 / 5 V Logic, Schmitt-trigger Input

- HVIC for Gate Driving, Under-Voltage and Short-Cir.55TJ14TIroncS.1.9(o)12-6.3(vnLroncS.p(o)1(l)34o)12(v)-1.w[•).3 / 5 V Logic

- Optimized for 15 kHz Switching Frequency

- Isolation Rating: 1500 V

# **General Description**

FNB51560TD1 is a Motion SPM 55 module providing a fully-featured, high-performance inverter output stage for AC Induction, BLDC, and PMSM motors. These modules integrate optimized gate drive of the built-in IGBTs to

<sub>rms</sub> / min.

# **Applications**

• Motion Control - Home Appliance / Industrial Motor

# **Related Resources**

- <u>AN-9096 Smart Power Module, Motion SPM® 55</u> <u>Series User's Guide</u>

- <u>AN-9097 SPM® 55 Packing Mounting Guidance</u>

# **Integrated Power Functions**

• 600 V - 15 A IGBT inverter for three phase DC / AC power conversion (Please refer to Figure 3)

# Integrated Drive, Protection and System Control Functions

- For inverter high-side IGBTs: gate drive circuit, high-voltage isolated high-speed level shifting

control circuit Under-Voltage Lock-Out (UVLO) protection

- For inverter low-side IGBTs: gate drive circuit, Short-Circuit Protection (SCP) control supply circuit Under-Voltage Lock-Out (UVLO) protection

- Fault signaling: corresponding to UVLO (low-side supply) and SC faults

- Input interface: High-active interface, works with 3.3 / 5 V logic, Schmitt trigger input

- Built in Bootstrap circuitry in HVIC

# **Pin Configuration**

| Pin Number | Pin Name              | Pin Description                                                       |

|------------|-----------------------|-----------------------------------------------------------------------|

| 1          | Р                     | Positive DC-Link Input                                                |

| 2          | U, V <sub>S</sub> (U) | Output for U Phase                                                    |

| 3          | V, V <sub>S</sub> (V) | Output for V Phase                                                    |

| 4          | W, V <sub>S</sub> (W) | Output for W Phase                                                    |

| 5          | NU                    | Negative DC-Link Input for U Phase                                    |

| 6          | N <sub>V</sub>        | Negative DC-Link Input for V Phase                                    |

| 7          | N <sub>W</sub>        | Negative DC-Link Input for W Phase                                    |

| 8          | IN <sub>(UL)</sub>    | Signal Input for Low-Side U Phase                                     |

| 9          | IN <sub>(UH)</sub>    | Signal Input for High- ide U Phase                                    |

| 10         | IN <sub>(VL)</sub>    | Signal Input for Low-Side V Phase                                     |

| 11         | IN <sub>(VH)</sub>    | Signal Input for High-Side V Phase                                    |

| 12         | IN <sub>(WL)</sub>    | Signal Input for Low-Side W Phase                                     |

| 13         | IN <sub>(WH)</sub>    | Signal Input for High-Side W Phase                                    |

| 14         | V <sub>DD</sub>       | Common Bias Voltage for IC and IGBTs Driving                          |

| 15         | СОМ                   | Common Supply Ground                                                  |

| 16         | C <sub>SC</sub>       | Capacitor (Low-Pass Filter) for Short-circuit Current Detection Input |

| 17         | V <sub>F</sub>        | Fault Output, Shut-Down Input, Temperature Output of Drive IC         |

| 18         | V <sub>B(W)</sub>     | High-Side Bias Voltage for W-Phase IGBT Driving                       |

| 19         | V <sub>B(V)</sub>     | High-Side Bias Voltage for V-Phase IGBT Driving                       |

| 20         | V <sub>B(U)</sub>     | High-Side Bias Voltage for U-Phase IGBT Driving                       |

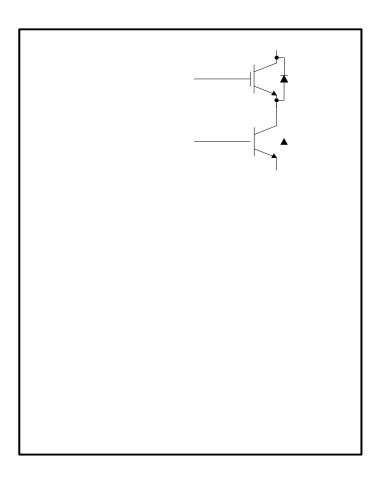

# Internal Equivalent Circuit and Input/Output Pins

# Figure 3. Internal Block Diagram

#### Note:

- 1. Inverter high-side is composed of three IGBTs, freewheeling diodes, and one control IC for each IGBT.

- 2. Inverter low-side is composed of three IGBTs, freewheeling diodes, and one control IC for each IGBT. It has gate drive and protection functions.

- 3. Single drive IC has gate driver for six IGBTs and protection functions.

- 4. Inverter power side is composed of four inverter DC-link input terminals and three inverter output terminals.

# Absolute Maximum Ratings (T<sub>J</sub> = 25°C, unless otherwise specified.)

# **Inverter Part**

| Symbol                 | Parameter                          | Conditions                                                 | Rating    | Unit |

|------------------------|------------------------------------|------------------------------------------------------------|-----------|------|

| V <sub>PN</sub>        | Supply Voltage                     | Applied between P - $N_U$ , $N_V$ , $N_W$                  | 450       | V    |

| V <sub>PN(Surge)</sub> | Supply Voltage (Surge)             | Applied between P - $N_U$ , $N_V$ , $N_W$                  | 500       | V    |

| V <sub>CES</sub>       | Collector - Emitter Voltage        |                                                            | 600       | V    |

| * ± I <sub>C</sub>     | Each IGBT Collector Current        | $T_{C} = 25^{\circ}C, T_{J} = 150^{\circ}C$                | 15        | А    |

| * $\pm I_{CP}$         | Each IGBT Collector Current (Peak) | $T_{C} = 25^{\circ}C, T_{J}$ 150°C, Under 1 ms Pulse Width | 30        | A    |

| * P <sub>C</sub>       | Collector Dissipation              | T <sub>C</sub> = 25°C per Chip                             | 22        | W    |

| Τ <sub>J</sub>         | Operating Junction Temperature     | (Note 5)                                                   | -40 ~ 150 | °C   |

#### Note:

5. The maximum junction temperature rating of the power chips integrated within the Motion SPM<sup>®</sup> 55 product is 150°C.

### **Control Part**

| Symbol           | Parameter                      | Conditions                                                        | Rating                      | Unit |

|------------------|--------------------------------|-------------------------------------------------------------------|-----------------------------|------|

| V <sub>DD</sub>  | Control Supply Voltage         | Applied between V <sub>DD</sub> - COM                             | 20                          | V    |

| V <sub>BS</sub>  | High-Side Control Bias Voltage | Applied between V_B(U) - V_S(U), V_B(V) - V_S(V), V_B(W) - V_S(W) | 20                          | V    |

| V <sub>IN</sub>  | Input Signal Voltage           | $\begin{array}{llllllllllllllllllllllllllllllllllll$              | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| V <sub>F</sub>   | Fault Supply Voltage           | Applied between V <sub>F</sub> - COM                              | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| * I <sub>F</sub> | Fault Current                  | Sink Current at V <sub>F</sub> pin                                | 5                           | mA   |

| V <sub>SC</sub>  | Current Sensing Input Voltage  | Applied between C <sub>SC</sub> - COM                             | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

## **Total System**

| Symbol                | Parameter                                                                     | Conditions                                                                                     | Rating    | Unit             |

|-----------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------|------------------|

| V <sub>PN(PROT)</sub> | Self Protection Supply Voltage Limit<br>(Short Circuit Protection Capability) | $V_{DD} = V_{BS} = 13.5 \sim 16.5 \text{ V}$<br>T <sub>J</sub> = 150°C, Non-Repetitive, < 2 µs | 400       | V                |

| T <sub>STG</sub>      | Storage Temperature                                                           |                                                                                                | -40 ~ 125 | °C               |

| V <sub>ISO</sub>      | Isolation Voltage<br>Connect Pins to Heat Sink Plate                          | AC 60 Hz, Sinusoidal, 1 Minute                                                                 | 1500      | V <sub>rms</sub> |

## **Thermal Resistance**

| Symbol                | Parameter                                    | Conditions | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------|------------|------|------|------|------|

| R <sub>th(j-c)Q</sub> | Junction to Case Thermal Resistance (Note 7) |            |      |      |      |      |

#### Note:

6. For Marking "\*", These Value had been made an acquisition by the calculation considered to design factor.

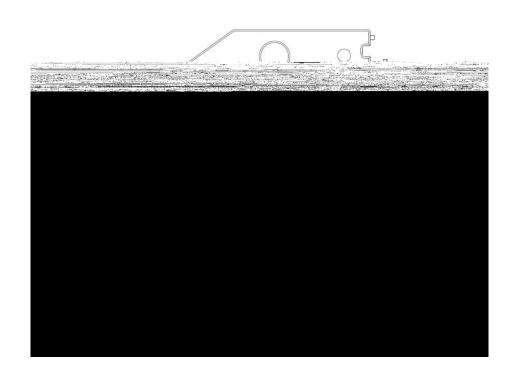

7. For the measurement point of case temperature (T\_C), please refer to Figure 2.

©2015 Semiconductor

| Control F                          | Part                                        |                          |                       |         |        |      |      |

|------------------------------------|---------------------------------------------|--------------------------|-----------------------|---------|--------|------|------|

| Symbol                             | Parameter                                   | Condition                | ns                    | Min.    | Тур.   | Max. | Unit |

| I <sub>QDD</sub>                   | Quiescent V <sub>DD</sub> Supply<br>Current |                          | V <sub>DD</sub> - COM | -       | 1.5    | 2.0  | mA   |

| I <sub>PDD</sub>                   | Operating V <sub>DD</sub> Supply<br>Current |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

| Neter                              |                                             |                          |                       |         |        |      |      |

| <b>Note:</b><br>9. Short-circuit p | protection is functioning for all six       | IGBTs.                   |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    |                                             |                          |                       |         |        |      |      |

|                                    | Figure. 5. V-T C                            | Curve of Temperature Out | out of IC (5V pull-   | up with | 10kohr | n)   |      |

|                                    |                                             |                          |                       |         |        |      |      |

©2015 Semiconductor FNB51560TD1 Rev. 1.1

| Bootstr         | ap Diode Part                |                                              |      |      |      |      |

|-----------------|------------------------------|----------------------------------------------|------|------|------|------|

| Symbol          | Parameter                    | Conditions                                   | Min. | Тур. | Max. | Unit |

| R <sub>BS</sub> | Bootstrap Diode<br>Resitance | V <sub>DD</sub> = 15V, T <sub>J</sub> = 25°C | -    | 280  | -    | Ω    |

## Figure 6. Built-In Bootstrap Diode Charaterstics

# **Recommended Operating Conditions**

| Symbol                                          | Parameter                                   | Conditions                                                                                  | Min. | Тур. | Max. | Unit   |

|-------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|--------|

| V <sub>PN</sub>                                 | Supply Voltage                              | Applied between P - $N_U$ , $N_V$ , $N_W$                                                   | -    | 300  | 400  | V      |

| V <sub>DD</sub>                                 | Control Supply Voltage                      | Applied between V <sub>DD</sub> - COM                                                       | 14.0 | 15   | 16.5 | V      |

| $V_{BS}$                                        | High - Side Bias Voltage                    | Applied between $V_{B(U)}$ - $V_{S(U)}, \; V_{B(V)}$ - $V_{S(V)}, \; V_{B(W)}$ - $V_{S(W)}$ | 13.0 | 15   | 18.5 | V      |

| dV <sub>DD</sub> / dt,<br>dV <sub>BS</sub> / dt | Control Supply Variation                    |                                                                                             | -1   | -    | 1    | V / μs |

| t <sub>dead</sub>                               | Blanking Time for<br>Preventing Arm - Short | For each input signal                                                                       | 0.5  | -    | -    | μs     |

| f <sub>PWM</sub>                                | PWM Input Signal                            | - 40°C T <sub>J</sub> 150°C                                                                 | -    | -    | 20   | kHz    |

| $V_{SEN}$                                       | Voltage for Current<br>Sensing              | Applied between N                                                                           |      |      |      |        |

#### Note:

10. This product might not make response if input pulse width is less than the recommanded value.

#### Note:

11. RC coupling at each input (parts shown dotted) might change depending on the PWM control scheme used in the application and the wiring impedance of the application's printed circuit board. The input signal section of the SPM 55 product integrates 10 kΩ (typ.) pull-down resistor. Therefore, when using an external filtering resistor, please pay attention to the signal voltage drop at input terminal.

## Figure 7. Recommended MCU I/O Interface Circuit

| Parameter                          |                                | Conditions                                                                                                             | Min.           | Тур. | Max. | Unit         |

|------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------|------|------|--------------|

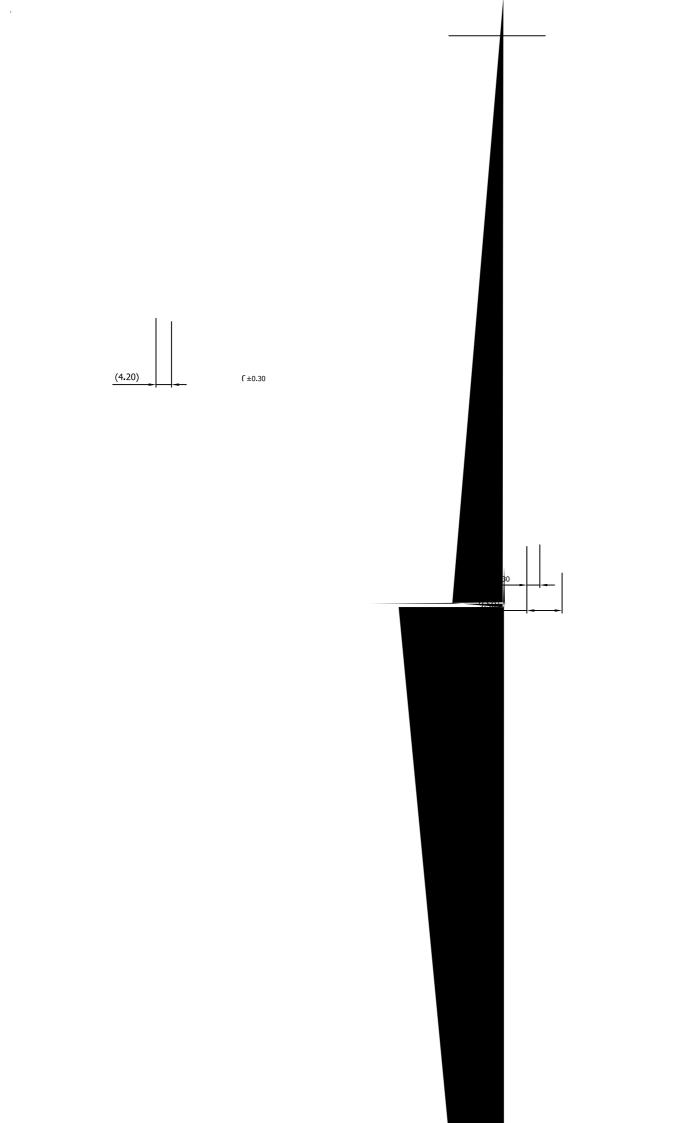

| Device Flatness                    | See Figure 8                   |                                                                                                                        | -50            | -    | 100  |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    | Figure                         | 8. Flatness Measuren                                                                                                   | nent Position  |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    | Figu                           | ure 9. Mounting Screw                                                                                                  | s Torque Order |      |      |              |

| Note:                              |                                |                                                                                                                        |                |      |      |              |

| 13. Avoid one side tightening stre | ess. Figure 11 shows the recon | unting torque may cause package crack<br>nmended torque order for mounting scre<br>20 ~ 30 % of maximum torque rating. |                |      |      | ne Motion SF |

|                                    |                                |                                                                                                                        |                |      |      |              |

|                                    |                                |                                                                                                                        |                |      |      |              |

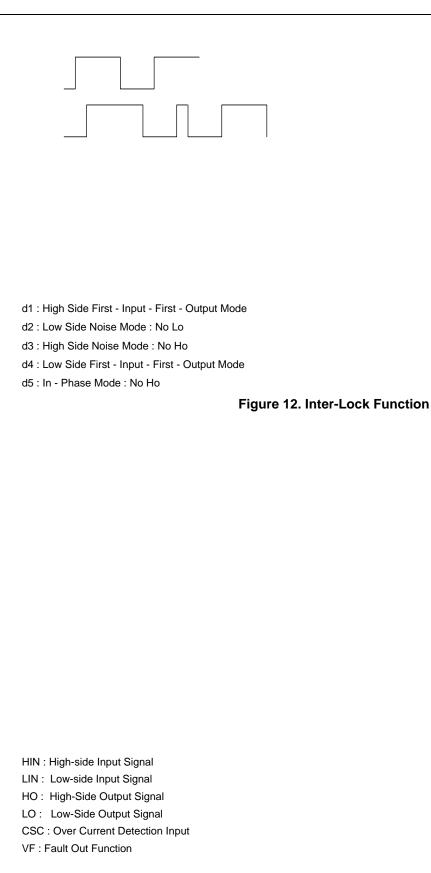

# **Time Charts of Protective Function**

Input Signal

Control Supply Voltage

Output Current

## Fault Output Signal

a1 : Control supply voltage rises: After the voltage rises UV<sub>DDR</sub>, the circuits start to operate when next input is applied.

- a2 : Normal operation: IGBT ON and carrying current.

- a3 : Under voltage detection (UV<sub>DDD</sub>).

a4 : IGBT OFF in spite of control input condition.

a5 : Fault output operation starts.

a6 : Under voltage reset (UV<sub>DDR</sub>).

a7 : Normal operation: IGBT ON and carrying current.

## Figure 10. Under-Voltage Protection (Low-Side)

b1: Control supply voltage rises: After the voltage reaches UV<sub>BSR</sub>, the circuits start to operate when next input is applied.

b2 : Normal operation: IGBT ON and carrying current.

b3 : Under voltage detection (UV\_{BSD}).

b4 : IGBT OFF in spite of control input condition, but there is no fault output signal.

b5 : Under voltage reset (UV<sub>BSR</sub>)

b6 : Normal operation: IGBT ON and carrying current

# Figure 11. Under-Voltage Protection (High-Side)

# Figure 13. Fault-Out Function By Over Current Protection

©2015 Semiconductor

#### Note:

1) To avoid malfunction, the wiring of each input should be as short as possible. (less than 2 ~ 3 cm)

2) By virtue of integrating an application specific type of HVIC inside the SPM<sup>®</sup> 55 product, direct coupling to MCU terminals without any opto-coupler or transformer isolation is possible.

3) V<sub>F</sub> is open-drain type. This signal line should be pulled up to the positive side of the MCU or control power supply with a resistor that makes I<sub>FO</sub> up to 5 mA. Please refer to Figure 15.

4)  $C_{\text{SP15}}$  of around seven times larger than bootstrap capacitor  $C_{\text{BS}}$  is recommended.

5) Input signal is active-HIGH type. There is a 10 kΩ resistor inside the IC to pull down each input signal line to GND. RC coupling circuits is recommanded for the prevention of input signal oscillation. R<sub>S</sub>C<sub>PS</sub> time constant should be selected in the range 50 ~ 150 ns

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdt/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor roducts, "ripcical" parameters witch may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and erasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equ