#### F **B251**

### **PRODUCT SUMMARY**

### **General Description**

The FUSB251 is an I2C controlled switch with over voltage protection on CC and SBU pins in Type-C interface port. The device has SPST switches on CC1/2 and SBU1/2 which enable automatically with valid VDD so that Type-C/PD controller can use the over voltage protected CC path. The FUSB251 has dead battery mode, CC pulled down hat Tyhrgi0syhrgi0d3,echip IEC protection with surge

C and SBU. Both CC and SBU ports are 24 V DC pe is WLCSP with 15 ball 3x5 array.

#### **Features**

- Low Ron SPST Switches on both CC1/2 and SBU1/2 Path for

- Dead Battery Mode Provides Default Rd Presenting on CC1/2

- 24 V DC Tolerant on CC and SBU

- ±35 V Surge Protection on CC and SBU

- Over Voltage Protection on CC and SBU

- I2C Interface with Processor with Interrupt for event Notification

- Moisture Detection on CC and SBU Pins

- On-chip IEC ESD Protection with External Capacitor on CAP Pin

- CC Ron 0.3 Ω Typical

- SBU Ron 3 Ω Typical

- 50 MHz Bandwidth on SBU Switch

- 15 ball WLCSP

#### **Applications**

- Smart Phones

- Tablets, Netbooks, Ultra-Mobile PCs

- Gaming Devices and E-books

- Portable Devices with Li-ion Battery

- Car Cigarette Jack

- External USB Storage

#### www.onsemi.com

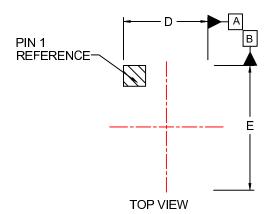

WLCSP15, 1.49x2.06x0.574 CASE 567WV

### **MARKING DIAGRAM**

UE = 2 digit Device Identifier KK = 2 digit Lot Run Code XY = 2 digit Date Code Ζ = 1 digit Plant Code = Pin A1 Mark

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

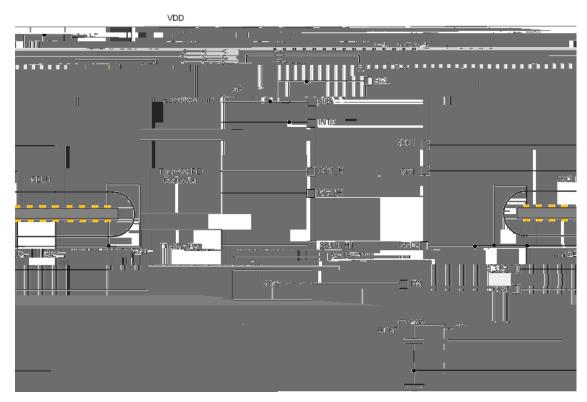

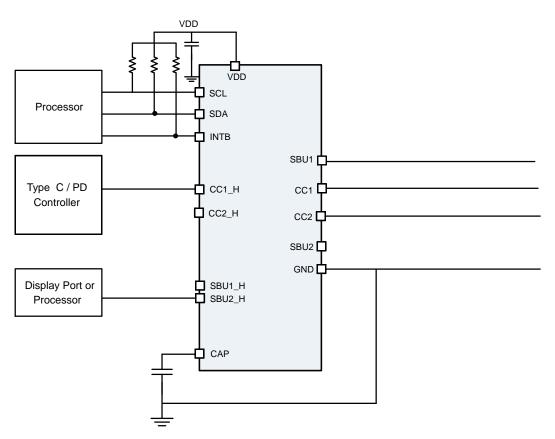

## **APPLICATION DIAGRAM**

Figure 1. Application Diagram

## **PART NUMBERING**

## **ORDERING INFORMATION**

| Part Number | Temperature Range | Package                                           | Packing Method † |  |

|-------------|-------------------|---------------------------------------------------|------------------|--|

| FUSB251UCX  | 40 to 85°C        | WLCSP, 3 x 5 array, 15 ball,<br>1.49 mm x 2.06 mm | Tape & Reel      |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

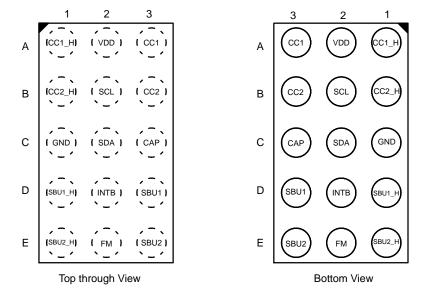

## **PRODUCT PIN ASSIGNMENTS**

## **Pin Configuration**

Figure 2. Pin Configuration

## **Pin Descriptions**

### **PIN DESCRIPTIONS**

| Pin# | Name   | Туре              | Description                                                                                                                        |

|------|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| C1   | GND    | Ground            | GND                                                                                                                                |

| A2   | VDD    | Power             | Power                                                                                                                              |

| А3   | CC1    | I/O               | Type C CC interface. Connect to USB Type C connector CC1 pin                                                                       |

| В3   | CC2    | I/O               | Type C CC interface. Connect to USB Type C connector CC2 pin                                                                       |

| A1   | CC1_H  | I/O               | Type C CC Host interface, Connect to USB Type C controller CC1 pin                                                                 |

| B1   | CC2_H  | I/O               | Type C CC Host interface, Connect to USB Type C controller CC2 pin                                                                 |

| D3   | SBU1   | I/O               | Type C SBU interface, Connect to USB Type C connector SBU1 pin                                                                     |

| E3   | SBU2   | I/O               | Type C SBU interface, Connect to USB Type C connector SBU2 pin                                                                     |

| D1   | SBU1_H | I/O               | Type C SBU Host Interface, Connect to Host side SBU1 application pin                                                               |

| E1   | SBU2_H | I/O               | Type C SBU Host Interface, Connect to Host side SBU2 application pin.                                                              |

| E2   | FM     | I/O               | Factory test mode pin, Connect to ADC input of host processor. If not used, connect to GND. FM can be switched over to one of SBU. |

| C3   | CAP    | 0                 | Capacitor pin, Connect to 0.1 μF capacitor to GND                                                                                  |

| B2   | SCL    | Open Drain Input  | I <sup>2</sup> C interface, Pull up to Vdd is required, Connect to SCL pin of Processor                                            |

| C2   | SDA    | Open Drain I/O    | I <sup>2</sup> C interface, Pull up to Vdd is required, Connect to SDA pin of Processor                                            |

| D2   | INTB   | Open Drain Output | Interrupt for Host alert, Pull up to VDD required, Connect to processor Interrupt input                                            |

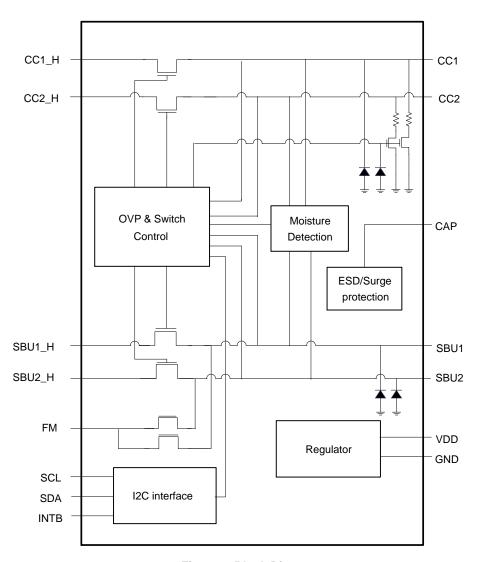

## PRODUCT BLOCK DIAGRAM

## **Block Diagram**

Figure 3. Block Diagram

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                | Parameter              | Conditions                                  | Min | Тур | Max  | Units |

|-----------------------|------------------------|---------------------------------------------|-----|-----|------|-------|

| TJ                    | Junction Temperature   |                                             | 40  |     | +150 | °C    |

| T <sub>STG</sub>      | Storage Temp           |                                             | 65  |     | +150 | °C    |

| VDD                   | Supply voltage         | Slew Rate 2 V/μs (rising), 1 V/μs (falling) | 0.5 |     | 12.0 | V     |

| VCC                   | Vccx to GND            |                                             | 0.5 |     | 24   | V     |

| VSBU                  | VSBUx to GND           |                                             | 0.5 |     | 24   | V     |

| VCCx_H and<br>VSBUx_H | VCCX_H, VSBUx_H to GND |                                             | 0.5 |     | 6.0  | V     |

| ICCSW                 | DC CC switch current   |                                             |     |     | 1.25 | Α     |

## **ESD RATINGS - JEDEC / IEC SPECIFICATION**

| Electro Static Discharge (ESD) Specifications | Condition                |                   | Value  | Unit |

|-----------------------------------------------|--------------------------|-------------------|--------|------|

| Human Body Model, JEDEC JESD22 A114           | CCx and SBUx pins to GND |                   | ±5000  | V    |

|                                               | Other pins               |                   | ±2000  |      |

| Charged Device Model, JEDEC JESD22 C101       | All pins                 |                   | ±1000  |      |

| IEC 61000 4 2 System ESD                      | CCx and SBUx pins to GND | Air gap Discharge | ±15000 |      |

|                                               |                          | Contact Discharge | ±8000  |      |

| IEC 61000 4 5 Lightning and Surge             | CCx and SBUx pins to GND |                   | ±35    |      |

## **OPERATING CONDITIONS**

VDD

$\textbf{ELECTRICAL SPECIFICATION TABLE} \ \ \textbf{Unless otherwise specified: Recommended } \ T_A \ \ \text{and } \ T_J \ \ \text{temperature ranges. All typical values are at } \ T_A = 25^{\circ}\text{C} \ \ \text{and } \ \ VDD = 3.8 \ \ V \ \ \ \text{unless otherwise specified.}$

| Symbol                    | Parameter                                                 | Conditions                                                                                                | Min  | Тур                                                          | Max           | Unit      |

|---------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|---------------|-----------|

| IQ                        | Quiescent supply current                                  | VDD = 2.7 to 5.5 V, Switch is closed, no load, moisture detection is not enabled                          |      | 15                                                           |               | μΑ        |

| I <sub>MOS</sub>          | Current with moisture detection enabled                   | VDD = 2.7 to 5.5 V, Switch is closed,<br>CC toggle and CC moisture<br>detection is enabled, Avg for 1 sec |      | 30                                                           |               | μΑ        |

| I <sub>DRY</sub>          | Current consumption when Dry check is working on          | VDD = 2.7 to 5.5 V,<br>Moisture detected, and Dry check<br>enabled, T(PD, period) = 4 sec                 |      | 15                                                           |               | μΑ        |

| I <sub>OFF</sub>          | Power off leakage current                                 | VDD = 0 V, Except CC1/CC2                                                                                 |      | 1                                                            |               | μΑ        |

| V <sub>UVLO</sub>         | Under voltage Lockout                                     | VDD Rising, VDD Falling                                                                                   |      | 2.45 (Rising),<br>2.40 (Falling)                             | 2.55 (Rising) | V         |

| T <sub>SD</sub>           | Thermal Shut down                                         | Shutdown Threshold/ Return from<br>Shutdown/ Hysteresis                                                   |      | 150°C<br>(shutdown),<br>130°C (Return),<br>20°C (Hysteresis) |               |           |

| ICC_LEAK                  | CC ON leakage current                                     | VDD = 2.7 to 5.5 V, CC Switch<br>closed, CCx_H float, measure<br>leakage from CCx with 3.3 V              |      |                                                              | 0.5           | μΑ        |

| R <sub>ON_CC</sub>        | CC1, CC2 RON resistance                                   | VDD = 2.7 to 5.5 V, IOUT = 200 mA                                                                         |      | 300                                                          |               | $m\Omega$ |

| R <sub>Flatness_CC</sub>  | VDD = 2.7 to 5.5 V,<br>Vcc swing = 0 V 1.2 V              |                                                                                                           |      | 10                                                           |               | mΩ        |

| V <sub>OVP_CC</sub>       | CC over voltage protection threshold                      | VDD = 2.7 to 5.5 V, VCC rising                                                                            | 5.70 | 5.85                                                         | 6.00          | ٧         |

| V <sub>OVP_CC_FALL</sub>  | CC recover threshold when voltage on CC is falling        | VDD = 2.7 V to 5.5 V                                                                                      |      | 5.70                                                         |               | V         |

| V <sub>OV_HYS_CC</sub>    | CC OVP threshold Hysteresis                               | VDD = 2.7 to 5.5 V                                                                                        |      |                                                              | 0.15          | V         |

| t <sub>CC_OVP</sub>       | CC OVP Trip time (Note 1)                                 | VDD = 2.7 to 5.5 V, CCx rise from 4 V to 6 V with 1 V/ns slew rate, RL = 30 $\Omega$ on CCx_H             |      | 250                                                          |               | ns        |

| Rd_CC                     | Dead battery pull down resistance                         | VDD = 0 to UVLO, Dead battery resistance / Voltage on pin 4.1                                             |      | 5.1                                                          | 6.1           | kΩ        |

| V <sub>OVP_SBU</sub>      | SBU over voltage threshold                                | VDD = 2.7 to 5.5 V, SBU Rising                                                                            | 4.4  | 4.5                                                          | 4.7           | V         |

| V <sub>OVP</sub> SBU_FALL | SBU OVP recovery threshold when voltage on SBU is falling | VDD = 2.7 V to 5.5 V                                                                                      |      | 4.35                                                         |               | V         |

| V <sub>OV_SBU_HYS</sub>   | SBU OVP Hysteresis                                        | VDD = 2.7 to 5.5 V, Measure<br>difference between SBUX rising and<br>falling OVP threshold                |      |                                                              | 0.15          | V         |

#### **FUNCTIONAL SPECIFICATIONS**

### **POR and Reset**

The FUSB251 closes both CC and SBU switches with a valid VDD supply after Power On reset. Until valid VDD is supplied, FUSB251 presents Rd on both CC1 and CC2 so that a source device can provide Vbus and Type–C controller can present Rd continuously after POR so VBUS will be consistent. At UVLO condition which is 2.4 volt (falling), CC and SBU switches get open again and Rd will be presented on both CC.

There is device reset register, bit0 in 0x0B register. If the register bit is set, all registers in the device are set to default, so momentarily both switches will be open and closed back.

so momentarily both switches will be open and closed back. y Dead Batitoyn MOei abteristics Tw[661 a)1 Tf.552615 Tm-0450 Tcthroughegistalid 598(.) TJ2.3711 0 TD-02(CC and from(vrx\_Hice CC and SBU Switch Characteristics

The FUSB251 has 2x SPSTChara,(vrx0001ches with a) TJ-8957 52 TD0Twx3245that a

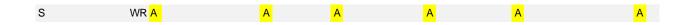

## **I2C Interface**

The FUSB251 includes a full I2C slave controller. The I2C slave fully complies with the I2C specification version

6 requirements. This block is designed for fast mode signals. Examples of an  $I^2C$  write and read sequence are shown in below figures respectively.

Figure 5. I<sup>2</sup>C Write Example

Detection time on CC moisture is dependent on the settling time and number of ADC read, default is 1 time ADC and 400  $\mu$ s settle time. They can be programmed in Timer2 register, 0x0C.

#### **SBU Moisture Detection**

If CC port is on DRP or Source mode, moisture inside connector can make leakage path from CC to SBU, which makes SBU can have float voltage similar to the shape of CC. So the SBU float voltage can be detected if moisture is present while CC is on toggle or SRC mode. SBU float voltage detection can be started with the EN\_SBUFT register set. If the bit is set, FUSB251 starts monitoring voltage on both SBU1 and SUB2, and if the voltage on either port is the same or above the threshold, the moisture\_status register (0x06, bit 4 and/or 5) is set with an interrupt. With the interrupt, processor can turn off the CC and SBU switch path to protect from corrosion, or processor could further moisture check using force SBU detection.

SBU float voltage detection also can be enabled when CC moisture detection result is timer expire, which can happen where there is no DRP toggle on CC. For example, if CC moisture detection is enabled where Type-C accessory is already plugged-in, the moisture detection will end up timer expire and so SBU float voltage detection will be started instead.

Once SBU float voltage detection is enabled, it keeps monitoring until moisture found. If device is reset or both EN\_CC and EN\_SBUFT are disabled, the floating detection stops and goes back to disable mode which is idle mode.

Force SBU detection is initiated by EN\_SBU or Auto\_EN\_SBU bit. Auto\_EN\_SBU bit is for pre-set before

moisture is detected, EN\_SBU can be set at anytime when SBU moisture detection is needed. After either CC or SBU float voltage detection detected moisture, if Auto\_EN\_SBU bit is set, FUSB251 goes to moisture detection on SBU with

## ADC TABLE FOR MOISTURE DETECTION

|    | Bit  | Pull up (kΩ) to 1 V | Moisture resistance (kΩ) | Voltage (V) |

|----|------|---------------------|--------------------------|-------------|

| 0  | 0    | 320                 | 17                       | 0.05        |

| 1  | 1    | 320                 | 36                       | 0.1         |

| 2  | 10   | 320                 | 56                       | 0.15        |

| 3  | 11   | 320                 | 80                       | 0.2         |

| 4  | 100  | 320                 | 107                      | 0.25        |

| 5  | 101  | 320                 | 137                      | 0.3         |

| 6  | 110  | 320                 | 172                      | 0.35        |

| 7  | 111  | 320                 | 213                      | 0.4         |

| 8  | 1000 | 320                 | 262                      | 0.45        |

| 9  | 1001 | 320                 | 320                      | 0.5         |

| 10 | 1010 | 320                 | 391                      | 0.55        |

| 11 | 1011 | 320                 | 480                      | 0.6         |

|    | 1100 | 320                 | 594                      | 0.65        |

|    | 1101 | 320                 | 747                      | 0.7         |

|    | 1110 | 320                 | 960 _                    | 0.75        |

|    | 1111 | 320                 | 1,280                    | 0.8         |

ABLE

|       |        |        | Read Only | Write Only | Read / Write | Read / Clear | Write / Clear |  |

|-------|--------|--------|-----------|------------|--------------|--------------|---------------|--|

| it[7] | Bit[6] | Bit[5] |           |            |              |              |               |  |

DEVICE ID Address: 01h

Reset Value: 0x100X\_XXXX

Type: Read

Bit # Name R/W/C Size (Bits)

INTERRUPT\_MASK

Address: 04h

Reset Value: 0x0000\_0000

Type: Read / Write

| 3 | Mask_Dry_Detect | R/W | 1 | 1 : Mask DRY status change interrupt      |

|---|-----------------|-----|---|-------------------------------------------|

| 2 | Mask_MOS_Detect | R/W | 1 | 1 : Mask Moisture status change interrupt |

| 1 | Mask_OVP_REC    | R/W | 1 | 1 : Mask OVP recovery interrupt           |

| 0 | Mask_OVP        | R/W | 1 | 1 : Mask OVP Interrupt                    |

STATUS

Address: 05h

Reset Value: 0x0000\_0000

Type: Read

| Bit # | Name     | R/W/C | Size (Bits) | Description                                                                     |

|-------|----------|-------|-------------|---------------------------------------------------------------------------------|

| 7     | LOOK4CC  | R     | 1           | 1 : Device is monitoring moisture on CC1 or CC2                                 |

| 6     | LOOK4SBU | R     | 1           | 1 : Device is monitoring moisture on SBU1 or SBU2 using float voltage detection |

| 5     | LOOK4DRY | R     | 1           | 1 : Monitoring Dry check on SBU1 and SBU2                                       |

| 3:2   | NU       | R     | 1           | Do not use                                                                      |

| 1     | OVP_SBU  | R     | 1           | 1 : OVP conditions on SBU1 or SBU2                                              |

| 0     | OVP_CC   | R     | 1           | 1 : OVP conditions on CC1 or CC2                                                |

MOISTURE\_STATUS

Address: 06h

Reset Value: 0x0000\_0000

Type: Read

| Bit # | Name  | R/W/C | Size (Bits) | Description                                                   |

|-------|-------|-------|-------------|---------------------------------------------------------------|

| 7:6   | FAULT | R     | 2           | These bits are set when moisture detection on SBU using volt- |

|       |       |       |             |                                                               |

|       |       |       |             |                                                               |

|       |       |       |             |                                                               |

|       |       |       |             |                                                               |

|       |       |       |             |                                                               |

## **SWITCH CONTROL**

Address: 07h

Reset Value: 0x0000\_0000 Type: Read / Write

| 2:1 | SBU | R/W | 2 | 00 : Open both SBU1 and SBU2 switches 01 : SBU1 and SBU2 close to SBU1_H and SBU2_H 10 : SBU2 closes to FM, SBU1, SBU1_H and SBU2_H are open 11 : SBU1 closes to FM, SBU2, SBU1_H and SBU2_H are open |

|-----|-----|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | СС  | R/W | 1 | 0 : CC1 and CC2 switch are open 1 : CC1 and CC2 close to CC1_H and CC2_H                                                                                                                              |

## THRESHOLD 1

Address: 08h

Reset Value: 0x1011\_1011 Type: Read / Write

| Bit # | Name        | R/W/C | Size (Bits) | Description                                  |

|-------|-------------|-------|-------------|----------------------------------------------|

| 7:4   | SBU_MOS_DET | R/W   | 4           | 0000 : 17 kΩ   0001 : 36 kΩ     1011 : 480 k |

**TIMER** Address: 0Ah

Reset Value: 0x0000\_0100

Type: Read / Write

| Bit # | Name | R/W/C | Size (Bits) | Description                                                                                                             |

|-------|------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 7:3   | NU   | R     | 5           | Do not use                                                                                                              |

| 2:0   | TDRY | R/W   | 3           | 000 : 50 ms<br>001 : 100 ms<br>010 : 250 ms<br>011 : 1 sec<br>100 : 2 sec<br>101 : 4 sec<br>110 : 8 sec<br>111 : 10 sec |

**RESET** Address: 0Bh

Reset Value: 0x0000\_0100 Type: Read / Write

| Bit # | Name      | R/W/C | Size (Bits) | Description                                                                                                                                                                                                                                 |

|-------|-----------|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2   | NU        | R     | 6           | Do not use                                                                                                                                                                                                                                  |

| 1     | MOS Reset | R/W/C | 1           | 1 : Reset moisture detection state machine and clear moisture status, Read returns '0'.                                                                                                                                                     |

|       |           |       |             | This register bit resets moisture detection state machine and moisture status register is cleared. Control register is not affected by this bit. If any moisture detection enable bit was set, moisture detection will restart by MOS Reset |

| 0     | Reset     | R/W/C | 1           | 1 : Reset the device, Read returns '0' The Device Reset includes FM pin configuration so FM pin status is checked after this Reset                                                                                                          |

TIMER2 Address: 0Ch

Reset Value: 0x0000\_0100 Type: Read / Write

| Bit # | Name               | R/W/C | Size (Bits) | Description                                                                |

|-------|--------------------|-------|-------------|----------------------------------------------------------------------------|

| 7:4   | NU                 | R     | 4           | Do not use                                                                 |

| 3:2   | Number of ADC Read | R/W   | 2           | 00 : 1 time<br>01 : 2 times<br>10 : 3 timers<br>11 : Do not use(no change) |

| 1:0   | CC Settle time     | R/W   | 2           | <b>00 : 400 μs</b> 01 : 300 μs 10 : 500 μs 11 : 600 μs                     |

## **APPLICATION CIRCUIT**

Figure 8. A

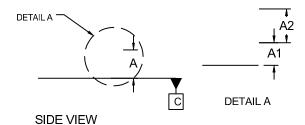

### WLCSP15, 1.49x2.06x0.574 CASE 567WV ISSUE O

**DATE 12 JUL 2018**

### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DATUM C APPLIES TO THE SPHERICAL CROWN OF THE SOLDER BALLS

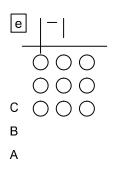

**BOTTOM VIEW**

1 2 3

RECOMMENDED MOUNTING FOOTPRINT (NSMD PAD TYPE)