CNSE

Ţ

TM

### **TYPICAL APPLICATION**

Figure 2. Typical Application

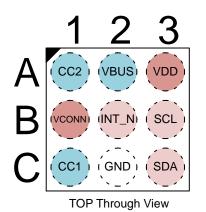

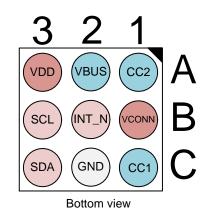

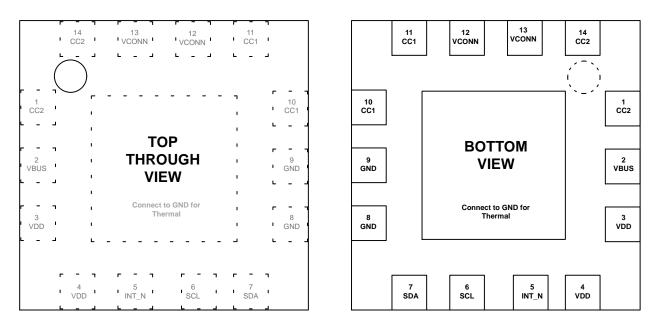

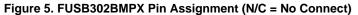

### **PIN CONFIGURATION**

### Figure 4. FUSB302BUCX Pin Assignment

#### Table 2. PIN MAP

|       | Column 1 | Column 2 | Column 3 |

|-------|----------|----------|----------|

| Row A | CC2      | VBUS     | VDD      |

| Row B | VCONN    | INT_N    | SCL      |

| Row C | CC1      | GND      | SDA      |

#### Table 3. PIN DESCRIPTION

| Name         | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB TYPE-C C | ONNECTOR INTE | RFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CC1/CC2      | I/O           | <ul> <li>Type-C connector Configuration Channel (CC) pins. Initially used to determine when an attach has occurred and what the orientation of the insertion is. Functionality after attach depends on mode of operation detected.</li> <li>Operating as a host: <ol> <li>Sets the allowable charging current for VBUS to be sensed by the attached device</li> <li>Used to communicate with devices using USB BMC Power Delivery</li> <li>Used to detect when a detach has occurred</li> </ol> </li> <li>Operating as a device: <ol> <li>Indicates what the allowable sink current is from the attached host. Used to communicate with devices using USB BMC Power Delivery</li> </ol> </li> </ul> |

| GND          | Ground        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VBUS         | Input         | VBUS input pin for attach and detach detection when operating as an upstream facing port (Device). Expected to be an OVP protected input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| POWER INTER  | FACE          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD          | Power         | Input supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VCONN        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **CONFIGURATION CHANNEL SWITCH**

•

The FUSB302B integrates the control and detection functionality required to implement a USB Type-C host, device or dual-role port including:

- Device Port Pull-Down (R<sub>D</sub>)

- Host Port Pull-Up (I<sub>P</sub>)

- VCONN Power Switch with OCP for Full-Featured USB3.1 Cables

# Table 4. PROCESSOR CONFIGURES THE FUSB302B THROUGH I<sup>2</sup>C

I<sup>2</sup>C Registers/Bits

Value

TOGGLE

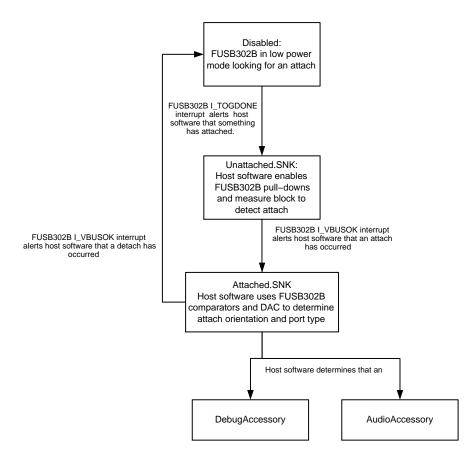

Figure 7. SNK Software Flow

cc

Figure 9. HOST\_CUR Changed prior to Attach

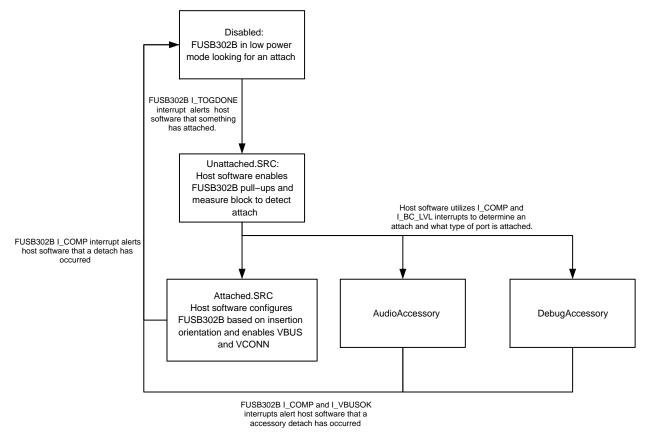

#### Manual Dual-Role Detection and Configuration

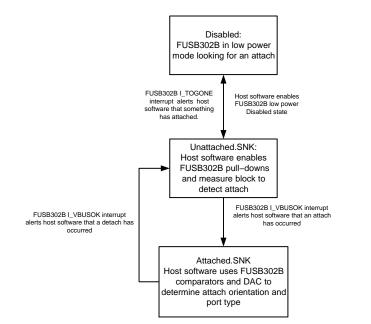

The Type-C specification allows ports to be both a device and a host depending on what type of port has attached. This functionality is similar to USB OTG ports with the current USB connectors and is called a dual-role port. The

FUSB302B can be used to implement a dual-role port. A Type-C dual role port toggles between presenting as a Type-C device and a Type-C host. The host software controls the toggle time and configuration of the FUSB302B in each state as shown in Figure 11.

Figure 11. DRP Software Flow

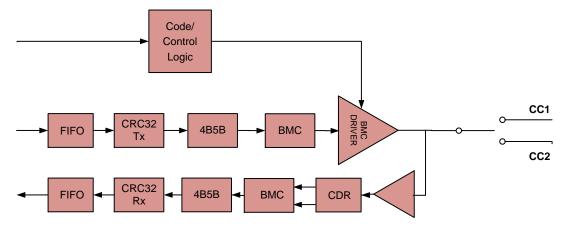

#### **BMC POWER DELIVERY**

The Type-C connector allows USB Power Delivery (PD) to be communicated over the connected CC pin between two ports. The communication method is the BMC Power Delivery protocol and is used for many different reasons with the Type-C connector. Possible uses are outlined below.

- Negotiating and controlling charging power levels

- Alternative Interfaces such as MHL, Display Port

- Vendor specific interfaces for use with custom docks or accessories

- Role swap for dual-role ports that want to switch who is the host or device

- Communication with USB3.1 full featured cables

The FUSB302B integrates a thin BMC PD client which includes the BMC physical layer and packet FIFOs (48 bytes for transmit and 80 bytes for receive) which allows packets to be sent and received by the host software through I<sup>2</sup>C accesses. The FUSB302B allows host software to implement all features of USB BMC PD through writes and

reads of the FIFO and control of the FUSB302B physical interface.

The FUSB302B uses tokens to control the transmission of BMC PD packets. These tokens are written to the transmit FIFO and control how the packet is transmitted on the CC pin. The tokens are designed to be flexible and support all aspects of the USB PD specification. The FUSB302B additionally enables control of the BMC transmitter through tokens. The transmitter can be enabled or disabled by specific token writes which allow faster packet processing by burst writing the FIFO with all the information required to transmit a packet.

The FUSB302B receiver stores the received data and the received CRC in the receive FIFO when a valid packet is received on the CC pin. The BMC receiver automatically enables the internal oscillator when an Activity is sensed on the CC pin and load to the FIFO when a packet is received. The I\_ACTIVITY and I\_CRC\_CHK interrupts alert the host software that a valid packet was received.

Figure 12. USB BMC Power Delivery Blocks

#### **Power Level Determination**

The Type-C specification outlines the order of precedence for power level determination which covers power levels from basic USB2.0 levels to the highest levels of USB PD. The host software is expected to follow the USB Type-C specification for charging current priority based on feedback from the FUSB302B detection, external BC1.2 detection and any USB Power Delivery communication.

The FUSB302B does not integrate BC1.2 charger detection which is assumed available in the USB transceiver or USB charger in the system.

#### Power Up, Initialization and Reset

When power is first applied through VDD, the FUSB302B is reset and registers are initialized to the default values shown in the register map.

The FUSB302B can be reset through software by programming the SW\_RES bit in the RESET register.

The FUSB302B can be reset through software by

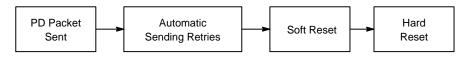

### PD Send

The FUSB302B implements part of the PD protocol layer for sending packets in an autonomous fashion.

### **PD Automatic Sending Retries**

If GoodCRC packet is not received and AUTO\_RETRY is set, then a retry of the same message that was in the TxFIFO written by the processor is executed within  $t_{Retry}$  and that is repeated for NRETRY times.

#### PD Send Soft Reset

If the correct GoodCRC packet is still not received for all retries then I\_RETRYFAIL interrupt is triggered and if AUTO\_SOFT\_RESET is set, then a Soft Reset packet is created (MessageID is set to 0 and the processor upon servicing I\_RETRYFAIL would set the true MessageIDCounter to 0.

If this Soft Reset is sent successfully where a GoodCRC control packet is received with a MessageID = 0 then I\_TXSENT interrupt occurs.

If not, this Soft Reset packet is retried NRETRIES times (MessageID is always 0 for all retries) if a GoodCRC acknowledge packet is not received with CRCReceiveTimer expiring ( $t_{Receive}$  of 1.1 ms max). If all retries fail, then I\_SOFTFAIL interrupt is triggered.

### PD Send Hard Reset

If all retries of the soft reset packet fail and if AUTO\_HARD\_RESET is set, then a hard reset ordered set is sent by loading up the TxFIFO with RESET1, RESET1, RESET1, RESET2 and sending a hard reset. Note only one

hard reset is sent since the typical retry mechanism doesn't apply. The processor's policy engine firmware is responsible for retrying the hard reset if it doesn't receive the required response.

### Flush Rx-FIFO with BIST (Built-In Self Test) Test Data

During PD compliance testing, BIST test packets are used

reCRe,

|                                                                                                                                                                                                                                                                                                                                                    | 8bits                          | 8bits         |                        | 8bits                        |                   | 8bits                 |                   |         |                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------|------------------------|------------------------------|-------------------|-----------------------|-------------------|---------|---------------------------|

| S Slave                                                                                                                                                                                                                                                                                                                                            | Address WR A                   | Register Addr | ess K <mark>A</mark> S | Slave Address                | RD <mark>A</mark> | Read Data K           | A Read Data K+1 A | Read D  | ata K+N-1 NA P            |

| Single or multi byte read executed from current register location (Single Byte read is<br>Register address to Read specified initiated by Master with NA immediately following first data byte)<br>Note: If Register is not specified Master will begin read from current register. In this case only sequence showing in Red<br>bracket is needed |                                |               |                        |                              |                   |                       |                   |         | byte)                     |

|                                                                                                                                                                                                                                                                                                                                                    | From Master t<br>From Slave to |               |                        | ondition<br>vledge (SDA Low) | NA<br>WR          | NOT Acknow<br>Write=0 | vledge (SDA High) | RD<br>P | Read =1<br>Stop Condition |

|                                                                                                                                                                                                                                                                                                                                                    |                                |               |                        |                              |                   |                       |                   |         |                           |

## Figure 15. I<sup>2</sup>C Read Example

#### Table 7. ABSOLUTE MAXIMUM RATINGS

| Symbol                | Parameter                                                 | Min  | Max | Unit |

|-----------------------|-----------------------------------------------------------|------|-----|------|

| Vv <sub>DD</sub>      | Supply Voltage from V <sub>DD</sub>                       | -0.5 | 6.0 | V    |

| V <sub>CC_HDDRP</sub> | CC pins when configured as Host, Device or Dual Role Port | -0.5 | 6.0 | V    |

VvBUSHost, Device ordjET59.754 514.602 .68033 154 513.921 59.754 .6803 ref mf(NOT Acko29.228 60.435 .6803 refB8 W 8 394.9228 511.84)m3.406 I-14592 60.435 .6803 refB13.9

T

### DC AND TRANSIENT CHARACTERISTICS

All typical values are at  $T_A = 25^{\circ}C$  unless otherwise specified.

### Table 9. BASEBAND PD

tRxFilter

|                          |                                                                                                          | T <sub>A</sub><br>T <sub>A</sub> = -40<br>T <sub>J</sub> = |     |      |      |

|--------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|------|------|

| Symbol                   | Parameter                                                                                                | Min                                                        | Тур | Max  | Unit |

| UI                       | Unit Interval                                                                                            | 3.03                                                       | -   | 3.70 | μs   |

| TRANSMITTER              | 2                                                                                                        |                                                            |     |      |      |

| zDriver                  | Transmitter Output Impedance                                                                             | 33                                                         | -   | 75   | Ω    |

| t <sub>EndDriveBMC</sub> | Time to Cease Driving the Line after the end of the last bit of the Frame                                | -                                                          | -   | 23   | μs   |

| t <sub>HoldLowBMC</sub>  | Time to Cease Driving the Line after the final High-to-Low Transition                                    | 1                                                          | -   | _    | μs   |

| V <sub>OH</sub>          | Logic High Voltage                                                                                       | 1.05                                                       | -   | 1.20 | V    |

| V <sub>OL</sub>          | Logic Low Voltage                                                                                        | 0                                                          | -   | 75   | mV   |

| t <sub>StartDrive</sub>  | Time before the start of the first bit of the preamble when the transmitter shall start driving the line | -1                                                         | _   | 1    | μS   |

| t <sub>RISE_TX</sub>     | Rise Time                                                                                                | 300                                                        | -   | _    | ns   |

| t <sub>FALL_TX</sub>     | Fall Time                                                                                                | 300                                                        | -   | -    | ns   |

| RECEIVER                 | •                                                                                                        | ·                                                          |     | •    | •    |

| cReceiver                | Receiver Capacitance when Driver isn't Turned On                                                         | -                                                          | 50  | -    | pF   |

| zBmcRx                   | Receiver Input Impedance                                                                                 | 1                                                          | -   | -    | MΩ   |

Rx Bandwidth Limiting Filter (Note 4) 4. Guaranteed by Characterization and/or Design. Not production tested.

100

\_

\_

ns

Figure 16. Transmitter Test Load

#### Table 10. TYPE-C CC SWITCH

|        |           | T <sub>A</sub> = -40 | = –40 to +8<br>to +105°C (<br>= –40 to +12 | Note 11) |      | l |

|--------|-----------|----------------------|--------------------------------------------|----------|------|---|

| Symbol | Parameter | Min                  | Тур                                        | Max      | Unit |   |

| R      |           |                      | •                                          |          | -    |   |

#### Table 11. CURRENT CONSUMPTION

|               |                                        |                     |                                                                                              | T <sub>A</sub> = -<br>T <sub>A</sub> = -40 to<br>T <sub>J</sub> = - |      | (Note 11) |      |

|---------------|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----------|------|

| Symbol        | Parameter                              | V <sub>DD</sub> (V) | Conditions                                                                                   | Min                                                                 | Тур  | Max       | Unit |

| Idisable      | Disabled Current                       | 3.0 to 5.5          | Nothing Attached,<br>No I <sup>2</sup> C Transactions                                        | -                                                                   | 0.37 | 5.0       | μΑ   |

| Idisable      | Disabled Current<br>(Note 11)          | 3.0 to 5.5          | Nothing Attached,<br>No I <sup>2</sup> C Transactions                                        | -                                                                   | 0.37 | 8.5       | μΑ   |

| Itog          | Unattached (standby)<br>Toggle Current | 3.0 to 5.5          | Nothing attached,<br>TOGGLE = 1,<br>PWR[3:0] = 1h,<br>WAKE_EN = 0,<br>TOG_SAVE_PWR2:1 = 01   | _                                                                   | 25   | 40        | μΑ   |

| lpd_stby_meas | BMC PD Standby<br>Current              | 3.0 to 5.5          | Device Attached, BMC PD<br>Active But Not Sending or<br>Receiving Anything,<br>PWR[3:0] = 7h | _                                                                   | 40   | -         | μΑ   |

#### Table 12. USB PD SPECIFIC PARAMETERS

|                        |                                                                                                                                                                                                                                |     | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$<br>$T_{A} = -40 \text{ to } +105^{\circ}\text{C} \text{ (Note 11)}$<br>$T_{J} = -40 \text{ to } +125^{\circ}\text{C}$ |     |      |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--|

| Symbol                 | Parameter                                                                                                                                                                                                                      | Min | Тур                                                                                                                                                                 | Max | Unit |  |

| tHardReset             | If a Soft Reset message fails, a Hard Reset is sent after tHardReset of CRCReceiveTimer expiring                                                                                                                               | -   | -                                                                                                                                                                   | 5   | ms   |  |

| tHardReset<br>Complete | If the FUSB302B cannot send a Hard Reset within tHardResetComplete time because of a busy line, then a I_HARDFAIL interrupt is triggered                                                                                       | -   | -                                                                                                                                                                   | 5   | ms   |  |

| tReceive               | This is the value for which the CRCReceiveTimer expires.<br>The CRCReceiveTimer is started upon the last bit of the EOP of the<br>transmitted packet                                                                           | 0.9 | -                                                                                                                                                                   | 1.1 | ms   |  |

| tRetry                 | Once the CRCReceiveTimer expires, a retry packet has to be sent out within tRetry time. This time is hard to separate externally from tReceive since they both happen sequentially with no visible difference in the CC output | _   | -                                                                                                                                                                   | 75  | μs   |  |

| tSoftReset             | If a GoodCRC packet is not received within tReceive for NRETRIES then a Soft Reset packet is sent within tSoftReset time.                                                                                                      | -   | -                                                                                                                                                                   | 5   | ms   |  |

| tTransmit              | From receiving a packet, we have to send a GoodCRC in response within tTransmit time. It is measured from the last bit of the EOP of the received packet to the first bit sent of the preamble of the GoodCRC packet           | -   | -                                                                                                                                                                   | 195 | μs   |  |

#### Table 13. IO SPECIFICATIONS

|        |           |                     |            | $T_A = -40$ | = –40 to +8<br>to +105°C (<br>= –40 to +12 | (Note 11) |      |

|--------|-----------|---------------------|------------|-------------|--------------------------------------------|-----------|------|

| Symbol | Parameter | V <sub>DD</sub> (V) | Conditions | Min         | Тур                                        | Max       | Unit |

#### HOST INTERFACE PINS (INT\_N)

| V <sub>OLINTN</sub>   | Output Low Voltage                                                       | 3.0 to 5.5 | I <sub>OL</sub> = 4 mA | -  | - | 0.4 | V  |

|-----------------------|--------------------------------------------------------------------------|------------|------------------------|----|---|-----|----|

| T <sub>INT_Mask</sub> | Time from global interrupt<br>mask bit cleared to when<br>INT_N goes LOW | 3.0 to 5.5 |                        | 50 | - | _   | μs |

#### I<sup>2</sup>C INTERFACE PINS – STANDARD, FAST, OR FAST MODE PLUS SPEED MODE (SDA, SCL) (Note 6)

| V <sub>ILI2C</sub> | Low-Level Input Voltage  | 3.0 to 5.5 | _    | - | 0.51 | V |

|--------------------|--------------------------|------------|------|---|------|---|

| V <sub>IHI2C</sub> | High-Level Input Voltage | 3.0 to 5.5 | 1.32 | - | -    | V |

#### Table 13. IO SPECIFICATIONS

|                                                                                                    |           |                     |            | $T_A = -40$ | = -40 to +8<br>to +105°C (<br>= -40 to +12 | (Note 11) |      |  |

|----------------------------------------------------------------------------------------------------|-----------|---------------------|------------|-------------|--------------------------------------------|-----------|------|--|

| Symbol                                                                                             | Parameter | V <sub>DD</sub> (V) | Conditions | Min         | Тур                                        | Max       | Unit |  |

| I <sup>2</sup> C INTERFACE PINS – STANDARD, FAST, OR FAST MODE PLUS SPEED MODE (SDA, SCL) (Note 6) |           |                     |            |             |                                            |           |      |  |

Hysteresis of Schmitt Trigger Inputs 3.0 to 5.5 mV 94 V<sub>HYS</sub> \_ \_ Input Current of SDA and SCL Pins 3.0 to 5.5 Input Voltage 0.26 V to 2.0 V -10 10 μΑ I<sub>I2C</sub> \_ VDD Current when SDA or 3.0 to 5.5 Input Voltage 1.8 V -10 10 I<sub>CCTI2C</sub> \_ μΑ SCL is HIGH Low-Level Output Voltage V 3.0 to 5.5 VOLSDA  $I_{OL} = 2 \text{ mA}$ 0 \_ 0.35 (Open-Drain) Low-Level Output Current IOLSDA 3.0 to 5.5  $V_{OLSDA} = 0.4 V$ 20 mΑ \_ \_ (Open-Drain) Capacitance for Each I/O CI 3.0 to 5.5 \_ 5 pF \_ Pin (Note 7)

6.  $I^2C$  pull up voltage is required to be between 1.71 V and V<sub>DD</sub>.

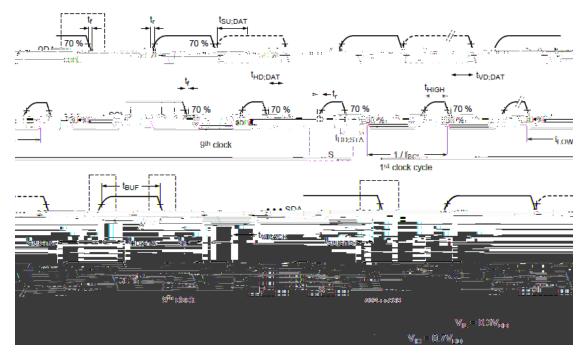

### Table 14. I<sup>2</sup>C SPECIFICATIONS FAST MODE PLUS I<sup>2</sup>C SPECIFICATIONS

|                     |                                                   | Fast Mo |      |      |

|---------------------|---------------------------------------------------|---------|------|------|

| Symbol              | Parameter                                         | Min     | Max  | Unit |

| f <sub>SCL</sub>    | I2C_SCL Clock Frequency                           | 0       | 1000 | kHz  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition              | 0.26    | -    | μs   |

| t <sub>LOW</sub>    | Low Period of I2C_SCL Clock                       | 0.5     | -    | μS   |

| t <sub>HIGH</sub>   | High Period of I2C_SCL Clock                      | 0.26    | -    | μs   |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition          | 0.26    | -    | μs   |

| t <sub>HD;DAT</sub> | Data Hold Time                                    | 0       | -    | μS   |

| t <sub>SU;DAT</sub> | Data Set-up Time                                  | 50      | -    | ns   |

| tr                  | Rise Time of I2C_SDA and I2C_SCL Signals (Note 7) | -       | 120  | ns   |

| t <sub>f</sub>      | Fall Time of I2C_SDA and I2C_SCL Signals (Note 7) | 6       |      |      |

Figure 17. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus

#### Table 15. I<sup>2</sup>C SLAVE ADDRESS

| Name                                         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| FUSB302BUCX,<br>FUSB302BMPX,<br>FUSB302BVMPX | 0     | 1     | 0     | 0     | 0     | 1     | 0     | R/W   |

| FUSB302B01MPX                                | 0     | 1     | 0     | 0     | 0     | 1     | 1     | R/W   |

| FUSB302B10MPX                                | 0     | 1     | 0     | 0     | 1     | 0     | 0     | R/W   |

| FUSB302B11MPX                                | 0     | 1     | 0     | 0     | 1     | 0     | 1     | R/W   |

Table 16. REGISTER DEFINITIONS

### Table 18. SWITCHES0

(Address: 02h; Reset Value: 0x0000\_0011; Type: Read/Write)

| Bit # | Name      | R/W/C | Size (Bits) | Description                                                       |

|-------|-----------|-------|-------------|-------------------------------------------------------------------|

| 7     | PU_EN2    | R/W   | 1           | 1: Apply host pull up current to CC2 pin                          |

| 6     | PU_EN1    | R/W   | 1           | 1: Apply host pull up current to CC1 pin                          |

| 5     | VCONN_CC2 | R/W   | 1           | 1: Turn on the VCONN current to CC2 pin                           |

| 4     | VCONN_CC1 | R/W   | 1           | 1: Turn on the VCONN current to CC1 pin                           |

| 3     | MEAS_CC2  | R/W   | 1           | 1: Use the measure block to monitor or measure the voltage on CC2 |

| 2     | MEAS_CC1  | R/W   | 1           | 1: Use the measure block to monitor or measure the voltage on CC1 |

| 1     | PDWN2     | R/W   | 1           | 1: Device pull down on CC2. 0: no pull down                       |

| 0     | PDWN1     | R/W   | 1           | 1: Device pull down on CC1. 0: no pull down                       |

#### Table 19. SWITCHES1

(Address: 03h; Reset Value: 0x0010\_0000; Type: Read/Write)

| Bit # | Name                  | R/W/C | Size (Bits) | Description                                                                                                                                                                                                                        |

|-------|-----------------------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | POWERROLE             | R/W   | 1           | Bit used for constructing the GoodCRC acknowledge packet. This<br>bit corresponds to the Port Power Role bit in the message header if<br>an SOP packet is received:<br>1: Source if SOP<br><b>0: Sink if SOP</b>                   |

| 6:5   | SPECREV1:<br>SPECREV0 | R/W   | 2           | Bit used for constructing the GoodCRC acknowledge packet.<br>These bits correspond to the Specification Revision bits in the<br>message header:<br>00: Revision 1.0<br><b>01: Revision 2.0</b><br>10: Do Not Use<br>11: Do Not Use |

| 4     | DATAROLE              | R/W   | 1           | Bit used for constructing the GoodCRC acknowledge packet. This bit corresponds to the Port Data Role bit in the message header. For SOP:<br>1: SRC<br>0: SNK                                                                       |

| 3     | Reserved              | N/A   | 1           | Do Not Use                                                                                                                                                                                                                         |

| 2     | AUTO_CRC              | R/W   | 1           | <ol> <li>Starts the transmitter automatically when a message with a good CRC is received and automatically sends a GoodCRC acknowledge packet back to the relevant SOP*</li> <li>Feature disabled</li> </ol>                       |

| 1     | TXCC2                 | R/W   | 1           | 1: Enable BMC transmit driver on CC2 pin                                                                                                                                                                                           |

| 0     | TXCC1                 | R/W   | 1           | 1: Enable BMC transmit driver on CC1 pin                                                                                                                                                                                           |

#### Table 20. MEASURE

(Address: 04h; .Reset Value: 0x0011\_0001; Type: Read/Write)

| Bit # | Name      | R/W/C | Size (Bits) | Description                                                                                                                                                                |

|-------|-----------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Reserved  | N/A   | 1           | Do Not Use                                                                                                                                                                 |

| 6     | MEAS_VBUS | R/W   | 1           | <ol> <li>MDAC/comparator measurement is controlled by MEAS_CC*<br/>bits</li> <li>Measure VBUS with the MDAC/comparator. This requires<br/>MEAS_CC* bits to be 0</li> </ol> |

| 5:0   | MDAC[5:0] | R/W   | 6           |                                                                                                                                                                            |

#### Table 21. SLICE

(Address: 05h; Reset Value: 0x0110\_0000; Type: Read/Write)

| Bit # | Name          | R/W/C               | Size (Bits)                                                                                                                                                        | Description                                                                                                                                                                                                                                                                            |

|-------|---------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | SDAC_HYS[1:0] | SDAC_HYS[1:0] R/W 2 | Adds hysteresis where there are now two thresholds, the <i>lower threshold which is always the value programmed by</i> SDAC[5:0] and the higher threshold that is: |                                                                                                                                                                                                                                                                                        |

|       |               |                     |                                                                                                                                                                    | <ul> <li>11: 255 mV hysteresis: higher threshold = (SDAC value + 20hex)</li> <li>10: 170 mV hysteresis: higher threshold = (SDAC value + Ahex)</li> <li>01: 85 mV hysteresis: higher threshold = (SDAC value + 5)</li> <li>00: No hysteresis: higher threshold = SDAC value</li> </ul> |

| 5:0   | SDAC[5:0]     | R/W                 | 6                                                                                                                                                                  | BMC Slicer DAC data input. Allows for a programmable threshold so as to meet the BMC receive mask under all noise conditions.                                                                                                                                                          |

#### Table 22. CONTROL0

(Address: 06h; Reset Value: 0x0010\_0100; Type: (see column below))

| Bit # | Name     | R/W/C | Size (Bits) | Description                                                                     |

|-------|----------|-------|-------------|---------------------------------------------------------------------------------|

| 7     | Reserved | N/A   | 1           | Do Not Use                                                                      |

| 6     | TX_FLUSH | W/C   | 1           | 1: Self clearing bit to flush the content of the transmit FIFO                  |

| 5     | INT_MASK | R/W   | 1           | <ol> <li>Mask all interrupts</li> <li>Interrupts to host are enabled</li> </ol> |

| 4     |          |       | •           |                                                                                 |

#### Table 23. CONTROL1

(Address: 07h; Reset Value: 0x0000\_0000; Type: (see column below))

| Bit # | Name | R/W/C | Size (Bits) | Description |

|-------|------|-------|-------------|-------------|

| 7     |      |       |             |             |

### Table 25. CONTORL3

(Address: 09h; Reset Value: 0x0000\_0110; Type: (see column below))

| Bit # | Name            | R/W/C | Size (Bits) | Description                                                                                                                                                       |

|-------|-----------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Reserved        | N/A   | 1           | Do Not Use                                                                                                                                                        |

| 6     | SEND_HARD_RESET | W/C   | 1           | <ol> <li>Send a hard reset packet (highest priority)</li> <li>Don't send a soft reset packet</li> </ol>                                                           |

| 5     | BIST_TMODE      | R/W   | 1           | <ol> <li>BIST mode. Receive FIFO is cleared immediately after<br/>sending GoodCRC response</li> <li>Normal operation, All packets are treated as usual</li> </ol> |

| 4     | _               |       |             |                                                                                                                                                                   |

#### Table 35. INTERRUPTA

(Address: 3Eh; Reset Value: 0x0000\_0000; Type: Read/Clear)

| Bit # | Name       | R/W/C | Size (Bits) | Description                                                                                      |

|-------|------------|-------|-------------|--------------------------------------------------------------------------------------------------|

| 7     | I_OCP_TEMP | R/C   | 1           | 1: Interrupt from either a OCP event on one of the VCONN switches or an over-temperature event   |

| 6     | I_TOGDONE  | R/C   | 1           | 1: Interrupt indicating the TOGGLE functionality was terminated<br>because a device was detected |

| 5     |            |       |             |                                                                                                  |

#### Table 39. INTERRUPT

(Address: 42h; Reset Value: 0x0000\_0000; Type: Read/Clear)

| Bit # | Name        | R/W/C | Size (Bits) | Description                                                                                                                                                                     |

|-------|-------------|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | I_VBUSOK    | R/C   | 1           | 1: Interrupt occurs when VBUS transitions through 4.5 V. This bit typically is used to recognize port partner during startup                                                    |

| 6     | I_ACTIVITY  | R/C   | 1           | 1: A change in the value of ACTIVITY of the CC bus has oc-<br>curred                                                                                                            |

| 5     | I_COMP_CHNG | R/C   | 1           | 1: A change in the value of COMP has occurred. Indicates se-<br>lected CC line has tripped a threshold programmed into the<br>MDAC                                              |

| 4     | I_CRC_CHK   | R/C   | 1           | 1: The value of CRC_CHK newly valid. I.e. The validity of the<br>incoming packet has been checked                                                                               |

| 3     | I_ALERT     | R/C   | 1           | 1: Alert software an error condition has occurred. An alert is caused by:<br>TX_FULL: the transmit FIFO is full<br>RX_FULL: the receive FIFO is full<br>See <b>Status1</b> bits |

| 2     | I_WAKE      | R/C   | 1           | 1: Voltage on CC indicated a device attempting to attach.<br>Software must then power up the clock and receiver blocks                                                          |

| 1     | I_COLLISION | R/C   | 1           | 1: When a transmit was attempted, activity was detected on the active CC line. Transmit is not done. The packet is received normally                                            |

| 0     | I_BC_LVL    | R/C   | 1           | 1: A change in host requested current level has occurred                                                                                                                        |

### Table 40. FIFOS

(Address: 43h; Reset Value: 0x0000\_0000; Type: (see column below))

Bit # Name R/W/C Size (Bits)

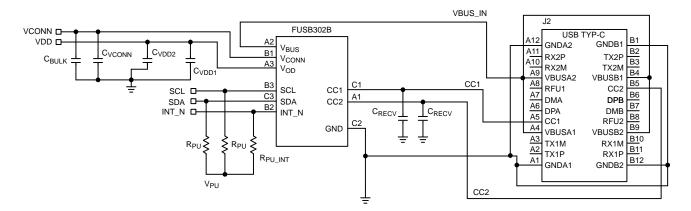

### **REFERENCE SCHEMATIC**

#### Table 43. RECOMMENDED COMPONENT VALUES FOR REFERENCE SCHEMATIC

|        |           | Recommended Value |      |

|--------|-----------|-------------------|------|

| Symbol | Parameter | Min               | Unit |

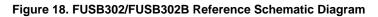

WQFN14 2.5x2.5, 0.5P CASE 510BR ISSUE O

DATE 31 AUG 2016

2.43

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi