#

## USB Power Delivery 3.0 Adaptive Source Charging Controller FUSB3307

FUSB3307 is a highly integrated USB Power Delivery (PD) power sourcecontroller that can control a DiDC port power regulator or the optoïcoupler in the second/a side of an AODC adapter. It implements the Source finite state machines of USB Power Delivery 3.0 (PD 3.0) and Typi€<sup>TM</sup> which includes Programmable Power Supplies (PPS). In order to meet the PPS specification, FUSB3307 supports minimum 3.3 V and maximum 21 V output voltage control. It includes Constant Voltage (Cp < 0 Tc <00ef>Tj /TTB7r9rcm0 to meecrts L inclut includes Constan . 3Cn7C0TsV outpute

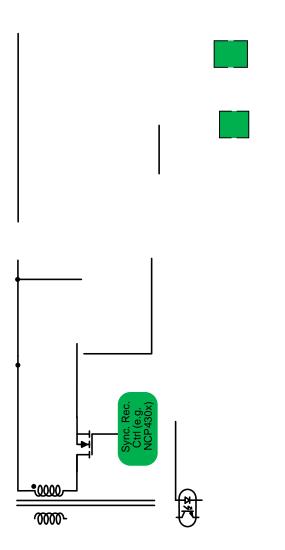

## APPLICATION DIAGRAM

-11

→

Figure 1. Offline Application Diagram

Figure 3. Block Diagram

#### PIN FUNCTION DESCRIPTION

| SOIC Pin<br>Number | QFN Pin<br>Number | Pin Name | I/О Туре | Description                                                                                                                                                                                |

|--------------------|-------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 14                | VCC      | Supply   | Output voltage (Input voltage to the FUSB3307). This pin is tied to the output of the power source to monitor its output voltage and supply internal bias to the FUSB3307 via the VDD pin. |

| 4                  | 19                | VDD      | Supply   | Internal supply voltage regulator output. This pin should be connected to an 1 $$ F external capacitor                                                                                     |

| 2                  | 4, 15,<br>DAP     | GND      |          |                                                                                                                                                                                            |

#### ORDERING INFORMATION

Part Number

|             | Parameter | Test Conditions | Symbol | Min | Тур | Max | Unit |  |

|-------------|-----------|-----------------|--------|-----|-----|-----|------|--|

| VOO OFOTION |           |                 |        |     |     |     |      |  |

VCC SECTION

#### Table 4. ELECTRICAL CHARACTERISTICS $V_{CC} = 5 V$ , $T_J = ~i40^{\circ}C$ to 125°C unless otherwise specified.

| Parameter                                                    | Test Conditions                                       | Symbol                       | Min   | Тур   | Max   | Unit |  |  |  |

|--------------------------------------------------------------|-------------------------------------------------------|------------------------------|-------|-------|-------|------|--|--|--|

| CONSTANT VOLTAGE SENSING SECTION                             | CONSTANT VOLTAGE SENSING SECTION                      |                              |       |       |       |      |  |  |  |

| VFB Reference Voltage at 5.0 V<br>(Power ïon reset, default) | $V_{CC} = 5.0 \text{ V}, V_{CS} = 0 \text{ V}$        | V <sub>CVR ï5.0V</sub>       | 0.485 | 0.500 | 0.515 | V    |  |  |  |

| VFB Reference Voltage at 9 V                                 | $V_{CC} = 9 V, V_{CS} = 0 V$                          | V <sub>CVR ï9V</sub>         | 0.873 | 0.900 | 0.927 | V    |  |  |  |

| VFB Reference Voltage at 12 V                                | $V_{CC} = 12 \text{ V}, \text{ V}_{CS} = 0 \text{ V}$ | V <sub>CVR ï12V</sub>        | 1.164 | 1.200 | 1.236 | V    |  |  |  |

| VFB Reference Voltage at 15 V                                | $V_{CC} = 15 \text{ V}, \text{ V}_{CS} = 0 \text{ V}$ | V <sub>CVR ï15</sub> v       | 1.455 | 1.500 | 1.545 | V    |  |  |  |

| VFB Reference Voltage at 20 V                                | $V_{CC} = 20 \text{ V}, \text{ V}_{CS} = 0 \text{ V}$ | V <sub>CVR ï20V</sub>        | 1.940 | 2.000 | 2.060 | V    |  |  |  |

| VFB Reference Voltage of 20 mV step                          | $V_{CC}$ = 20 mV, $V_{CS}$ = 0 V                      | V <sub>CVR</sub> ïSTEP ï20mV | 1.940 | 2.000 | 2.060 | mV   |  |  |  |

FEEDBACK SECTION

| CATH Pin Sink Current | Minimum guaranteed sink current expected from CATH pin | I <sub>CATH</sub> ïSink | 2 |  | mA |

|-----------------------|--------------------------------------------------------|-------------------------|---|--|----|

|                       |                                                        |                         |   |  |    |

DISCHARGE SECTION VBUS to GND leakage resistance w

| VBUS to GND leakage resistance when<br>VBUS is not being sourced | GATE = 0 V | R <sub>DISC ïBUS</sub> | 72.4 | 155 |  | k |  |

|------------------------------------------------------------------|------------|------------------------|------|-----|--|---|--|

|------------------------------------------------------------------|------------|------------------------|------|-----|--|---|--|

VCC Pin Sink Current when discharging (Note 5)

Discharging current on VCC after a fault has trif 0 0 8j 0 -1.226.148 504.6804N.928 Ux. -.0004 Trif 0 0 .0019 T4 0 8 64.8 504.6804 Tm -.0015 Tc

#### **Application Information**

FUSB3307 has the entire PD Device Policy Manager where the FUSB3307 directly controls the DC/DC (DPM), PD Policy Engine, Protocol and PHY layers within controller. In the descriptions that follow, both of these hardware and responds to all the messages typical for PD designs are discussed when describing the operation of the Power Sources. No external processor is needed and it is FUSB3307 Interspersed within these descriptions dow it completely USB PD 3.0 with PPS compliant. relates to USB Power Delivery (PD) and Type C

#### Two Reference Design Examples

specifications. These are just two example designs since there are considerably more use cases of the FUSB3307 in

Below are two reference design example applications of reference designs for power source applications. For more the FUSB3307. One is an AC/DC design on the secondary information on specific design needs, please contact your side of the offline design and the other is a DC/DC design onsemifield application engineers.

Figure 5. Offline Reference Design Example

Power Up and Assumptions

For Figure 5, the focus ion only the secondary side of this of power source and only on the interactions with the FUSB3307 device. For Figure 6, only the interconnections of the FUSB3307 with the budikoost shown will be discussed, not the buckiboost operation. It is assumed all other functionality of these AC/DC and DC/DC designs is known.

For Figure 5, upon application of an AC source, the secondary side VCC starts at 5 V and for Figure 6, upon application of input VBAT, the buckboost regulates VCC at 5 V for USBiC operation. The FUSB3307 takes its input from the resistor divider ratio comprising of R8 and R9 in Figure 5 and Figure 6 above. In Figure 5, FUSB3307 controls the CATH pin current through the optioupler, R11 and R10 resistors for providing the feedback to the primary side controller to regulate to 5 V as shown in Figure 7.

typical default operation. However this build boost resistor divider is

Figure 7. Constant Voltage / Constant Current (CV/CC) section of Application Diagram

---

1

In Figure 6, FUSB3307 controls the CATH pin voltage which is tied to the COMP pin of the buildboost which directly regulates the output voltage to 5 V. The ratio of R9:(R8+R9) is expected the 1:10 to achieve 5 V on VCC upon power up which is typically R8 = 120 kohms and R9 = 13.3 kohms.

In Figure 6, the buckboost has its feedback FB pin which has the resistor that also expects a 1:10 resistor divider in

CC1 and CC2 Lines and USB ïC Receptacle Assumptions

If a USBïC receptacle is used, CC1 and CC2 are connected from the receptacle to the FUSB3307's CC1 and CC2 pins. If ahardwired connection (called "captive cable" in TypeïC and USB PD specifications) is desired, the CC line is connected to CC1 (or CC2 if more convenient for routing) and the VCONN line is connected to CC2 (or CC1) pin not used above.

The design in the figures above assumes a Type C receptacleas opposed to captive cable) and all the following descriptions are consistent with this configuration. Also assumed is SB 2.0 only receptacle (D+ andi) D for a power sourceapplication without data (that is, the USB D+ and D do not go to a USB PHY). All SuperSpeed lines (TX1+, TX1 ï, RX1+, RX1ï

#### Figure 10. VBUS Discharge by FUSB3307 via DISC Pin

VBUS is discharged through a resistor (Rita) the DISC USB Type C specification requires that the supply voltage pin of the FUSB3307 as shown in the highlighted section in is not sourced on VBUS until an attach per Type C specification has been determined. Dual bitatorikback

The external resistor R1 value is dependent on the total FET's for theload switch are not needed for reverse voltage bulk capacitance (C8) of this power source so that VBUS is protection since it is unlikely that VBUS is charged from an discharged within the time limits dictated by USB PD. A external source For interoperability with legacy connectors, typical value for R1 is 39, 1 W and in addition, there is there is a case where a Type A type TC cable is first plugged internal resistance that causes a expected discharge current to a Type A port of a power source which then supplies 5 V within the FUSB3307 in its discharge path & c iSink in the on VBUS of the cable. The Type C connector is plugged electrical tables above). If the load current to the Sink is into this design which is not the AC outlet nor sufficient (exceeds chien internal discharge is not The 5 V from the cable will forward conduct through the Q1 needed, then the FUSB3307 will automatically disable FET and charge the bulk capacitor C8. This doesn't cause an internal discharge.

Upon power up, the FUSB3307 will discharge VBUS in and CC2 lines and realize it is not a legitimate Sink device casethere is any voltage on VBUS since the only way a Sink plugged in and stay detached. Upon unplugging the A to C can be attached per Type C specification is if VBUS is cable, the discharge resistance (R<sub>C iBUS</sub>) in the electrical discharge to ground (below VSafe0V) upon attach. The tables above) will discharge VBUS to ground if the input discharge resistance limits are governed by the Type Cvoltage is still unavailable. Even if the input power is specification when not sourcing power on VBUS supplied to this design during this incorrect connection, (R<sub>DISC iBUS</sub> in the electrical tables above). It is preferred that VCC will regulate to 5 V which will prevent the previously no external load/discharge resistor is connected to VBUSforwardbias body diode of QfFET from conducting and the other than R1 to the FUSB3307 discharge DISC pin.

A TVS diode connected from BUS to ground and shown beforeturning on FET Q1The maximum bulk capacitance in the figures ([SZ]ESD7241) allow operating voltages up is specified in the Type C specification to handle this fault to 24 V covering the entire VBUS range of 3.3 V to 21 V for case ashown in Table 5 from the USBy De C specification a USB PD PPS contract. This can be replaced by a TVS that o as to allow for just on ET use for optimum efficiency. covers the VBUS range for the use case of this design if needed.

Table 5. TYPE IC SPECIFICATION FOR VBUS BULK CAPACITANCE

| Symbol              | Notes                                                                                                      | Min | Max  | Units |

|---------------------|------------------------------------------------------------------------------------------------------------|-----|------|-------|

| VBUS<br>Capacitance | Capacitance for source ïonly ports between VBUS and GND pins on receptacle when VBUS is not being sourced. |     | 3000 | F     |

|                     | Capacitance for DRP ports between VBUS and GND pins on recep-<br>tacle when VBUS is not being sourced.     |     | 10   | F     |

Capacitance to ground on the connector side VBUS connection (source of Q1) can be added if needed but it hasn't been shown in the application diagrams above. If added, it is recommended it doesn't exceedF1for recovery from the source case mentioned above.

#### Voltage and Current Sensing Operation

As mentioned above (seewer Up and Assumptions), the resistor ratio from VCC to ground formed by resistors R8 and R9 (typically 1:10atio where R8=120and R9=13.3k) and sensed via FUSB3307 VFB pin will sense the voltage for VCC in order to set a new voltage. For Figure 5 offline design, this will be done via the FUSB3307 CATH pin, the optoïcoupler, resistor R10 and the primary side PWM controller operation. R11 provides a bias current to the CATH pin feedback circuit within the FUSB3307 and is optional. ForFigure 6 buckboost design, this will be done via the FUSB3307 CATH pin controlling the buildoost PWM via its COMP pin. The FUSB3307 will automatically control the CATH pin based on the desired voltage as determine by the USB PD contract and the existing VCC voltagesensed by VFB. IFUSB3307'sPD communication is not responded to by the Sink upon initial attach, the

USB 2.0 Data Lines

The USB 2.0 Data Lines D+ and īDcan be externally connected together via a 100 ohms resistor to provide the maximum power, a legacy USB device can take, which is 1.5 A per USB Batter@hargingv1.2 (BC1.2)specification. This will usually be the case when a USB to microïB cable isplugged into this design where this adapter cable has the required Sink Rd resistors within it to allow the FUSB3307 to recognize a Type C attach and to source 5 V When a Sink device is connected via the **USB** connector, as mentioned above, the FUSB3307 will detect a legitimate Type C attached drive the GATE pin to turn on the VBUS load switch Q1. The initial voltage on VBUS is always 5 V (4.75 V to 5.5 V voltage range) and the CC pin will advertise 3 A capability which is the maximum power allowed by a Type C (without PD) port. FUSB3307 is not expected to S0B us>Tj5 5 V (4.75 B a w [W9c 0 Tw [ a 9a the USB

PD Status message sent to indicate that the source is 5 Apin for a typical Type C connection but no Sink device has capable but the cable has limited the source capabilities to be attached to the FUSB3307, then the current consumed 3 A. In Table 7 the section of the SOP Status Data Block is just I<sub>CC iGREEN</sub> ( < 870 A typical). This low standby (SDB) is shown that communicates this power limitation. currentallows for all the energy standard specifications to be

Table 7. PD Status Message to Sink Showing Power is Limited by the Cable

| Offset | Field           | Bit | Description                                            |

|--------|-----------------|-----|--------------------------------------------------------|

| 5      | Power<br>Status | 0   |                                                        |

|        | Status          | 1   | Source power limited due to<br>cable supported current |

|        |                 | 2   |                                                        |

|        |                 | 67  |                                                        |

The FUSB3307 follows all USB PD specifications including droppingdown to USB PD 2.0 operation when it detects a USB PD 2.0 Sink and dSB PD2.0 cable eMarker (if applicable). All subsequent operation will follow the USB PD 2.0 specification until the FUSB3307 is reset via a Hard Reset message or undergoes a power cycle.

Standby Operation

When the FUSB3307 is in standby, where the source powersupply still has to be maintained at 5 V via the CATH

| Table 8. MODIFIED ADVERTISED PDP BASED ON F | PDIVx |

|---------------------------------------------|-------|

|---------------------------------------------|-------|

currentallows for all the en**g**y standard specifications to be well exceeded for offline designs (typically the FUSB3307 within the offline design can achieve 21 mW standby power).

#### PDIVx Operation

The FUSB3307P6A0BF version of the FUSB3307 can adjust the output power to have any PDP (Power Delivery Power) from 16 W to 60 W in 7.5 W increments using the PDIV pins. Other FUSB3307 versions in the SOIC package will only advertise full power. The FUSB3307 versions in QFN package have the PDIV2 pin which will reduce the total power by 50% when set high. All other versions of the FUSB3307will advertise the PDPs as shown in Table 6. The output power adjustment is accomplished through the PDIV2, PDIV1 and PDIV0 pins which are shared with the D+ and Dï pins of other FUSB3307 versions.

The FUSB3307P6A0BF version can control the power as shown below (Table 8).

| Table 6. MODIFIED ADVERTISED FOF BASED ON FDIVA |       |       |                    |                    |                                        |  |  |  |

|-------------------------------------------------|-------|-------|--------------------|--------------------|----------------------------------------|--|--|--|

| PDIV2                                           | PDIV1 | PDIV0 | Total<br>Power (W) | % of 60 W<br>Total | Advertised PDP (Power Delivery Power)  |  |  |  |

| 1                                               | 1     | 1     | 60                 | 100%               | PDO's:5,9,12,15,20V @ 3A               |  |  |  |

| 1                                               | 1     | 0     | 52.5               | 87.50%             | PDO's:5,9,12,15 @ 3A, 20V @ 2.6A       |  |  |  |

| 1                                               | 0     | 1     | 45                 | 75%                | PDO's:5,9,12,15V @ 3A, 20V @ 2.25A     |  |  |  |

| 1                                               | 0     | 0     | 37.5               | 62.50%             | PDO's:5,9,12V @ 3A, 15V @ 2.46A        |  |  |  |

| 0                                               | 1     | 1     | 30                 | 50%                | PDO's:5,9V @ 3A, 12V @ 2.5A, 15V @ 2A  |  |  |  |

| 0                                               | 1     | 0     | 22.5               | 37.50%             | PDO's:5V @ 3A, 9V @ 2.44A, 12V @ 1.83A |  |  |  |

| 0                                               | 0     | Х     | 16                 | 25%                | PDO's:5V@3A, 9V @ 1.77A, 12V @ 1.33A   |  |  |  |

PDIV0 and PDIV1 are sampled during POR or when the FUSB3307P6A0BF tadvertise the new PDP values based FUSB3307P6A0BF executes a Soft\_Reset or Hard\_Reset new PDIV0 and PDIV1 pin settings.

which causes the new advertised capabilities to be sent to the

sink by the FUSB3307P6A0BF. Alternatively, recovery Protection Operation

from any protection operation would cause the shown in Table 9.

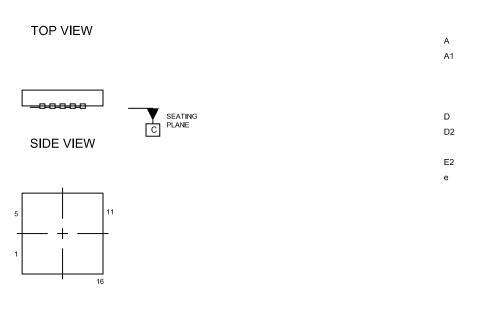

#### PACKAGE DIMENSIONS

SOIC ï14 NB CASE 751A ï03 ISSUE L

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

#### PACKAGE DIMENSIONS

QFNW20 4x4, 0.5P CASE 484AT ISSUE O

1. 6

3. DIMENSION b APPLIES TO THE PLATED

BOTTOM VIEW