# Serial Flash Memory 2 Mb (256K x 8)

www.onsemi.com

#### Overview

The LE25S20XA is a SPI bus flash memory device with a 2M bit (256K 8-bit) configuration. It uses a single 1.8V power supply. While making the most of the features inherent to a serial flash memory device, the LE25S20XA is housed in an 8-pin ultra-miniature package. All these features make this device ideally suited to storing program in applications more compact dimensions. The LE25S20XA also has a small sector erase capability which makes the device ideal for storing parameters or data that have fewer rewrite cycles and conventional EEPROMs cannot handle due to insufficient capacity.

WLCSP8, 1.55x1.53

#### Features

#### 1.

| Operations power supply   | : 1.65 to 1.95V supply voltage range                            |

|---------------------------|-----------------------------------------------------------------|

| Operating frequency       | : 40MHz (max)                                                   |

| Temperature range         | : -40 to +85 C                                                  |

| Serial interface          | : SPI mode 0, mode 3 supported                                  |

| Electronic Identification | : JDEC ID, Device ID                                            |

| Sector size               | : 4K bytes/small sector, 64K bytes/sector                       |

| Erase functions           | : Small Sector Erase (SSE), Sector Erase (SE), Chip Erase (CHE) |

| Page program function     | : 256 bytes/page                                                |

| Status functions          | : Ready/Busy information, protect information                   |

| Low operation current     | : 6.0mA (Read mode operation current ,40MHz)                    |

|                           | :15mA (Erase or Program mode operating current)                 |

|                           | :10uA (CMOS standby current)                                    |

| Erase time                | : 40ms (SSE, typ), 80ms (SE, typ), 300ms (CHE, typ)             |

| Page program time (tPP)   | : 3.0ms/256 bytes (typ.), 3.5ms/256 bytes (max.)                |

| High reliability          | : 100,000 erase/program cycles                                  |

|                           | : 20 years data retention period                                |

| Package                   | : WLCSP8                                                        |

\* This product is licensed from Silicon Storage Technology, Inc. (USA).

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 24 of this data sheet.

# Package Dimensions unit : mm

## Figure 1 Ball Assignments

| Ball No. | Symbol          | Pin Name           |

|----------|-----------------|--------------------|

| A1       | V <sub>DD</sub> | Power supply       |

| A2       | HOLD            | Hold               |

| A3       | CS              | Chip select        |

| B1       | SCK             | Serial clock       |

| B2       | SO              | Serial data output |

| C1       | SI              | Serial data input  |

| C2       | WP              | Write protect      |

| C3       | V <sub>SS</sub> | Ground             |

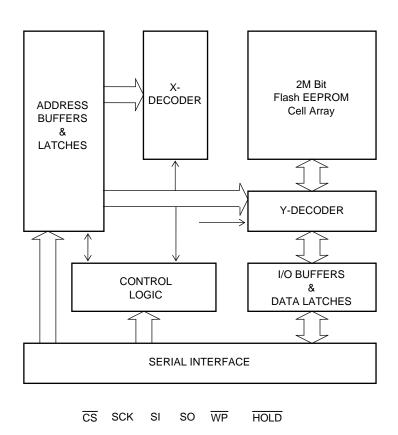

## Figure 2 Block Diagram

## **Table 1 Pin Description**

| Symbol          | Pin Name           | Description                                                                                                     |

|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------|

| SCK             | Serial clock       | This pin controls the data input/output timing.                                                                 |

|                 |                    | The input data and addresses are latched synchronized to the rising edge of the serial clock, and the data      |

|                 |                    | is output synchronized to the falling edge of the serial clock.                                                 |

| SI              | Serial data input  | The data and addresses are input from this pin, and latched internally synchronized to the rising edge of       |

|                 |                    | the serial clock.                                                                                               |

| SO              | Serial data output | The data stored inside the device is output from this pin synchronized to the falling edge of the serial clock. |

| CS              | Chip select        | The device becomes active when the logic level of this pin is low; it is deselected and placed in standby       |

|                 |                    | status when the logic level of the pin is high.                                                                 |

| WP              | Write protect      | The status register write protect (SRWP) takes effect when the logic level of this pin is low.                  |

| HOLD            | Hold               | Serial communication is suspended when the logic level of this pin is low.                                      |

| V <sub>DD</sub> | Power supply       | This pin supplies the 1.65 to 1.95V supply voltage.                                                             |

| V <sub>SS</sub> | Ground             | This pin supplies the 0V supply voltage.                                                                        |

## **Device Operation**

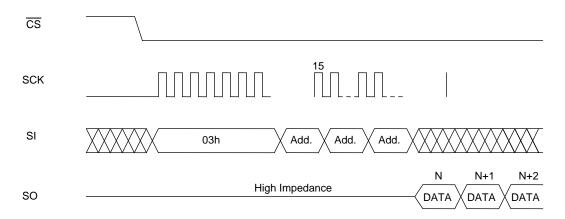

The read, erase, program and other required functions of the device are executed through the command registers. The serial I/O corrugate is shown in Figure 3 and the command list is shown in Table 2. At the falling  $\overline{CS}$  edge the device is selected, and serial input is enabled for the commands, addresses, etc. These inputs are normalized in 8 bit units and taken into the device interior in synchronization with the rising edge of SCK, which causes the device to execute operation according to the command that is input.

The LE25S20XA supports both serial interface SPI mode 0 and SPI mode 3. At the falling  $\overline{CS}$  edge, SPI mode 0 is automatically selected if the logic level of SCK is low, and SPI mode 3 is automatically selected if the logic level of SCK is high.

#### Figure 3 I/O waveforms

#### **Table 2 Command Settings**

| Command            | 1st bus cycle | 2nd bus<br>cycle | 3rd bus cycle | 4th bus cycle | 5th bus cycle | 6th bus cycle | Nth bus cycle |

|--------------------|---------------|------------------|---------------|---------------|---------------|---------------|---------------|

| Read               | 03h           | A23-A16          | A15-A8        | A7-A0         | RD *1         | RD *1         | RD *1         |

|                    | 0Bh           | A23-A16          | A15-A8        | A7-A0         | х             | RD *1         | RD *1         |

| Small sector erase | 20h / D7h     | A23-A16          | A15-A8        | A7-A0         |               |               |               |

| Sector erase       | D8h           | A23-A16          | A15-A8        | A7-A0         |               |               |               |

| Chip erase         | 60h / C7h     |                  |               |               |               |               |               |

| Page program       | 02h           | A23-A16          | A15-A8        | A7-A0         | PD *2         | PD *2         | PD *2         |

## Table 3 Command Settings

2M Bit

| sector(64KB) | small sector | address space | ce(A23 to A0) |

|--------------|--------------|---------------|---------------|

|              | 63           | 03F000h       | 03FFFFh       |

| 3            | to           |               |               |

|              | 48           | 030000h       | 030FFFh       |

|              | 47           | 02F000h       | 02FFFFh       |

| 2            | to           |               |               |

|              | 32           | 020000h       | 020FFFh       |

|              | 31           | 01F000h       | 01FFFFh       |

| 1            | to           |               |               |

|              | 16           | 010000h       | 010FFFh       |

|              | 15           | 00F000h       | 00FFFFh       |

|              | to           |               |               |

| 0            | 2            | 002000h       | 002FFFh       |

|              | 1            | 001000h       | 001FFFh       |

|              | 0            | 000000h       | 000FFFh       |

## **Description of Commands and Their Operations**

A detailed description of the functions and operations corresponding to each command is presented below.

#### 1. Standard SPI read

There are two read commands, the standard SPI read command and High-speed read command.

#### 1-1. Read command

Consisting of the first through fourth bus cycles, the 4 bus cycle read command inputs the 24-bit addresses following (03h). The data is output from SO on the falling clock edge of fourth bus cycle bit 0 as a reference. "Figure 4-a Read" shows the timing waveforms.

#### Figure 4-a Read

#### 1-2. High-speed Read command

Consisting of the first through fifth bus cycles, the High-speed read command inputs the 24-bit addresses and 8 dummy bits following (0Bh). The data is output from SO using the falling clock edge of fifth bus cycle bit 0 as a reference. "Figure 4-b High-speed Read" shows the timing waveforms.

#### Figure 4-b High-speed Read

When SCK is input continuously after the read command has been input and the data in the designated addresses has been output, the address is automatically incremented inside the device while SCK is being input, and the corresponding data is output in sequence. If the SCK input is continued after the internal address arrives at the highest address (3FFFFh), the internal address returns to the lowest address (00000h), and data output is continued. By setting the logic level of  $\overline{CS}$  to high, the device is deselected, and the read cycle ends. While the device is deselected, the output pin SO is in a high-impedance state.

#### 2. Status Registers

The status registers hold the operating and setting statuses inside the device, and this information can be read (status register read) and the protect information can be rewritten (status register write). There are 8 bits in total, and "Table 4 Status registers" gives the significance of each bit.

#### **Table 4 Status Registers**

| Bit  | Name     | Logic           | Function      | Power-on Time Information |  |

|------|----------|-----------------|---------------|---------------------------|--|

| Dito | RDY      | 0               | Ready         | 0                         |  |

| Bit0 | RDT      | 1 Erase/Program |               | 0                         |  |

| Ditt |          | 0               | 0             | Write disabled            |  |

| BITI | Bit1 WEN |                 | Write enabled | U                         |  |

| Bit2 | BP0      | 0               |               |                           |  |

Block protect information

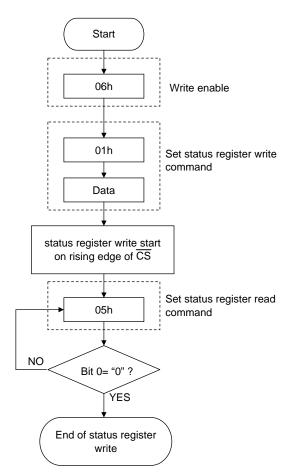

#### 2-2. Status register write

The information in status registers BP0, BP1, BP2, TB and SRWP can be rewritten using the status register write command.  $\overline{\text{RDY}}$ , WEN and bit 6 are read-only bits and cannot be rewritten. The information in bits BP0, BP1, BP2, TB and SRWP is stored in the non-volatile memory, and when it is written in these bits, the contents are retained even at power-down. "Figure 6 Status Register Write" shows the timing waveforms of status register write, and Figure 19 shows a status register write flowchart. Consisting of the first and second bus cycles, the status register write command initiates the internal write operation at the rising  $\overline{\text{CS}}$  edge after the data has been input

#### BP0, BP1, BP2, TB (Bits 2, 3, 4, 5)

Block protect BP0, BP1, BP2 and TB are status register bits that can be rewritten, and the memory space to be protected can be set depending on these bits. For the setting conditions, refer to "Table 5 Protect level setting conditions".

BP0, BP1, and BP2 are used to select the protected area and TB to allocate the protected area to the higher-order address area or lower-order address area.

ΤВ

#### **Table 5 Protect Level Setting Conditions**

Protect Level

Status Register Bits

BP1 BP0

Protected Area

#### 4. Write Disable

The write disable command sets status register WEN to "0" to prohibit unintentional writing. "Figure 8 Write Disable" shows the timing waveforms. The write disable co

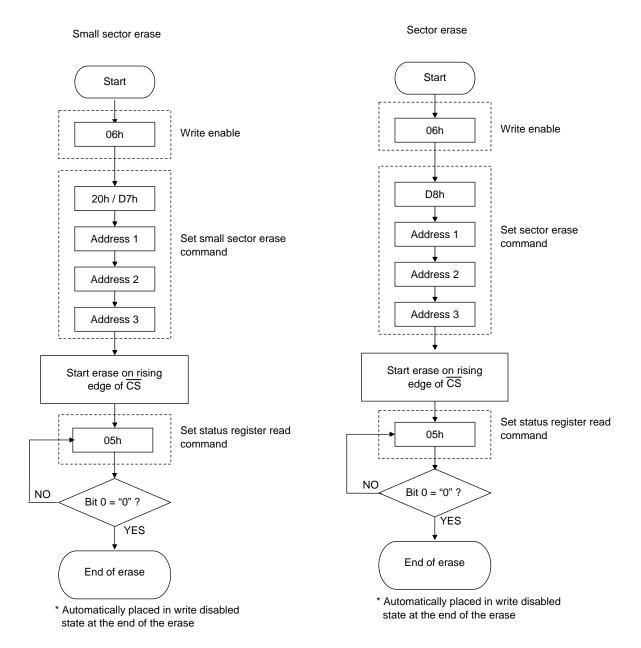

#### 6. Small Sector Erase

Small sector erase is an operation that sets the memory cell data in any small sector to "1". A small sector consists of

4Kbytes. "Figure 11 Small Sector Erase" shows the timi

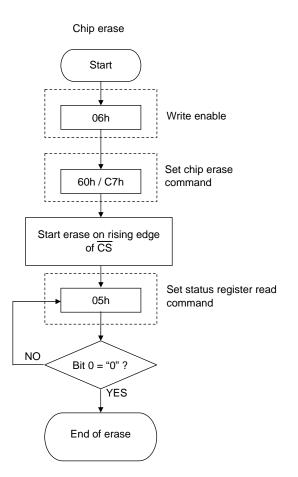

#### 8. Chip Erase

Chip erase is an operation that sets the memory cell data in all the sectors to "1". "Figure 13 Chip Erase" shows the timing waveforms, and Figure 20 shows a chip erase flowchart. The chip erase command consists only of the first bus cycle, and it is initiated by inputting (60h) or (C7h). After the command has been input, the internal erase operation starts from the rising  $\overline{CS}$  edge, and it ends automatically by the control exercised by the internal timer. Erase end can also be detected using status register  $\overline{RDY}$ .

#### Figure 13 Chip Erase

#### 9. Page Program

Page program is an operation that programs any number of bytes from 1 to 256 bytes within the same sector page (page addresses: A17 to A8). Before initiating page program, the data on the page concerned must be erased using small sector erase, sector erase, or chip erase. "Figure 14 Page Program" shows the page program timing waveforms, and Figure 21 shows a page program flowchart. After the falling  $\overline{CS}$ , edge, the command (02H) is input followed by the 24-bit addresses. Addresses A17 to A0 are valid. The program data is then loaded at each

#### 10. Silicon ID Read

ID read is an operation that reads the manufacturer code and device ID information. The silicon ID read command is not accepted during writing. There are two methods of reading the silicon ID, each of which is assigned a device ID. In the first method, the read command sequence consists only of the first bus cycle in which (9Fh) is input. In the subsequent bus cycles, the manufacturer code 62h which is assigned by JEDEC, 2-byte device ID code (memory type, memory capacity), and reserved code are output sequentially. The 4-byte code is output repeatedly as long as clock inputs are present, "Table 7-1 JEDEC ID code " lists the silicon ID codes and "Figure 15-a JEDEC ID read" shows the JEDEC ID read timing waveforms.

The second method involves inputting the ID read commanru25.3()-2(e m)1ID .3((ru25.3()-read)-5.3( co)-5.3(mman)TJ24.4551 0

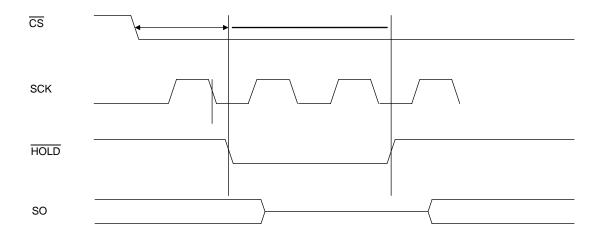

#### **11. Hold Function**

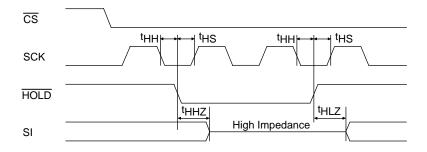

Using the  $\overline{\text{HOLD}}$  pin, the hold function suspends serial communication (it places it in the hold status). "Figure16  $\overline{\text{HOLD}}$ " shows the timing waveforms. The device is placed in the hold status at the falling  $\overline{\text{HOLD}}$  edge while the logic level of SCK is low, and it exits from the hold status at the rising  $\overline{\text{HOLD}}$  edge. When the logic level of SCK is high,  $\overline{\text{HOLD}}$  must not rise or fall. The hold function takes effect when the logic level of  $\overline{\text{CS}}$  is low, the hold status is exited and serial communication is reset at the rising  $\overline{\text{CS}}$  edge. In the hold status, the SO output is in the high-impedance state, and SI and SCK are "don't care".

### Figure 16 HOLD

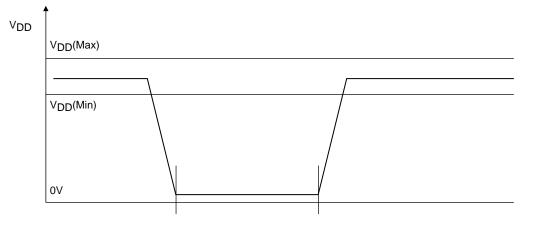

#### 12. Power-on

In order to protect against unintentional writing,  $\overline{CS}$  must be within at V<sub>DD</sub> 0.3 to V<sub>DD</sub>+0.3 on power-on. After power-on, the supply voltage has stabilized at VDD min. or higher, waits for t<sub>PU</sub> before inputting the command to start a device operation. The device is in the standby state and not in the power-down state after power is turned on. To put the device into the power-down state, it is necessary to enter a power-down command.

#### Figure 17 Power-on Timing

#### 13. Hardware Data Protection

LE25S20XA incorporates a power-on reset function. The following conditions must be met in order to ensure that the power reset circuit will operate stably.

No guarantees are given for data in the event of an instantaneous power failure occurring during the writing period.

#### Figure 18 Power-down Timing

#### **Power-on timing**

| Demonster                  | Sumbol           | sp  |     |      |  |

|----------------------------|------------------|-----|-----|------|--|

| Parameter                  | Symbol           | min | max | unit |  |

| power-on to operation time | <sup>t</sup> PU  | 100 |     | μs   |  |

| power-down time            | <sup>t</sup> PD  | 10  |     | ms   |  |

| power-down voltage         | <sup>t</sup> BOT |     | 0.2 | V    |  |

#### 14. Software Data Protection

The LE25S20XA eliminates the possibility of unintentional operations by not recognizing commands under the following conditions.

When a write command is input and the rising  $\overline{CS}$  edge timing is not in a bus cycle (8 CLK units of SCK) When the page program data is not in 1-byte increments

When the status register write command is input for 2 bus cycles or more

#### **15. Decoupling Capacitor**

A 0.1 F ceramic capacitor must be provided to each device and connected between  $V_{DD}$  and  $V_{SS}$  in order to ensure that the device will operate stably.

Specifications Absolute Maximum Ratings

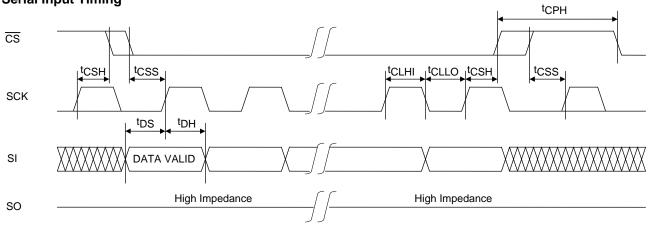

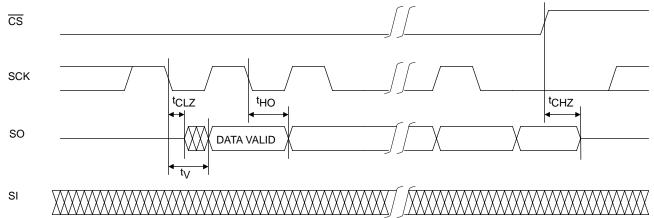

## **AC Characteristics**

|                                                 | Parameter                           |                                       |                   | Ratings |            |            | unit |

|-------------------------------------------------|-------------------------------------|---------------------------------------|-------------------|---------|------------|------------|------|

|                                                 |                                     |                                       | Symbol            | min     | typ max    |            |      |

|                                                 | Read instruct                       | Read instruction(03h)                 |                   |         |            | 25         | MHz  |

| Clock frequency                                 | All instruction                     | All instructions except for read(03h) |                   |         |            | 40         | MHz  |

| Input signal rising/fall                        | ing time                            |                                       | <sup>t</sup> RF   | 0.1     |            |            | V/ns |

| SCK logic high level                            | pulse width                         | 25MHz                                 | <sup>t</sup> CLHI | 14      |            |            |      |

|                                                 |                                     | 40MHz                                 |                   | 11.5    |            |            | ns   |

| SCK logic low level p                           | ulse width                          | 25MHz                                 | <sup>t</sup> CLLO | 14      |            |            | ns   |

|                                                 |                                     | 40MHz                                 |                   | 11.5    |            |            | 115  |

| CS setup time                                   |                                     |                                       | tCSS              | 10      |            |            | ns   |

| CS hold time                                    |                                     |                                       | <sup>t</sup> CSH  | 10      |            |            | ns   |

| Data setup time                                 |                                     |                                       | t <sub>DS</sub>   | 5       |            |            | ns   |

| Data hold time                                  |                                     |                                       | <sup>t</sup> DH   | 5       |            |            | ns   |

| $\overline{\text{CS}}$ wait pulse width         |                                     |                                       | <sup>t</sup> CPH  | 25      |            |            | ns   |

| Output high impedance time from $\overline{CS}$ |                                     |                                       | <sup>t</sup> CHZ  |         |            | 15         | ns   |

| Output data time from SCK                       |                                     |                                       | tv                |         | 8          | 11         | ns   |

| Output data hold time                           |                                     |                                       | <sup>t</sup> HO   | 1       |            |            | ns   |

| Output low impedance time from SCK              |                                     |                                       | <sup>t</sup> CLZ  | 0       |            |            | ns   |

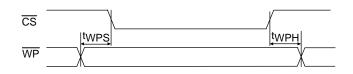

| WP setup time                                   |                                     | tWPS                                  | 20                |         |            | ns         |      |

| WP hold time                                    |                                     | <sup>t</sup> WPH                      | 20                |         |            | ns         |      |

| HOLD setup time                                 |                                     | <sup>t</sup> HS                       | 5                 |         |            | ns         |      |

| HOLD hold time                                  | HOLD hold time                      |                                       | tнн               | 5       |            |            | ns   |

| Output low impedance                            | Output low impedance time from HOLD |                                       | <sup>t</sup> HLZ  |         |            | 12         | ns   |

| Output high impedan                             | ce time from HOI                    | _D                                    | <sup>t</sup> HHZ  |         |            | 9          | ns   |

| Power-down time                                 |                                     | t <sub>DP</sub>                       |                   |         | 5          | S          |      |

| Power-down recovery time                        |                                     | <sup>t</sup> PRB                      |                   |         | 5          | S          |      |

| Write status register time                      |                                     | <sup>t</sup> SRW                      |                   | 8       | 10         | ms         |      |

| ·                                               |                                     | 256Byte                               |                   |         | 3          | 3.5        | ms   |

| Page programming cycle time                     | nByte                               | t <sub>PP</sub>                       |                   | 0.15+   | 0.20+      | ms         |      |

|                                                 |                                     |                                       |                   |         | n*2.85/256 | n*3.30/256 |      |

| Small sector erase cycle time                   |                                     | <sup>t</sup> SSE                      |                   | 0.04    | 0.15       | S          |      |

| Sector erase cycle tir                          | ne                                  |                                       | <sup>t</sup> SE   |         | 0.08       | 0.25       | S    |

| Chip erase cycle time                           | 9                                   |                                       | <sup>t</sup> CHE  |         | 0.3        | 3.0        | S    |

## **AC Test Conditions**

| Input pulse level······ 0.2V <sub>DD</sub> to 0.8V <sub>DD</sub> |

|------------------------------------------------------------------|

| Input rising/falling time ···· 5ns                               |

| Input timing level 0.3VDD, 0.7VDD                                |

| Output timing level ······ 1/2 VDD                               |

| Output load ······ 15pF                                          |

Note: As the test conditions for "typ"-4.5(te: 976 TD tes2137 11e4Tw(976 TD0 Tc( )Tj15.3054 -1.2455 TD.002lf("-4.5(te: 976 3(/fa

## **Timing waveforms**

## **Serial Input Timing**

## Serial Output Timing

### Hold Timing

#### Status register write Timing

#### Figure 19 Status Register Write Flowchart

Status register write

\* Automatically placed in write disabled state at the end of the status register write

#### **Figure 20 Erase Flowcharts**

\* Automatically placed in write disabled state at the end of the erase