### **ON Semiconducto**

http://onsemi.com

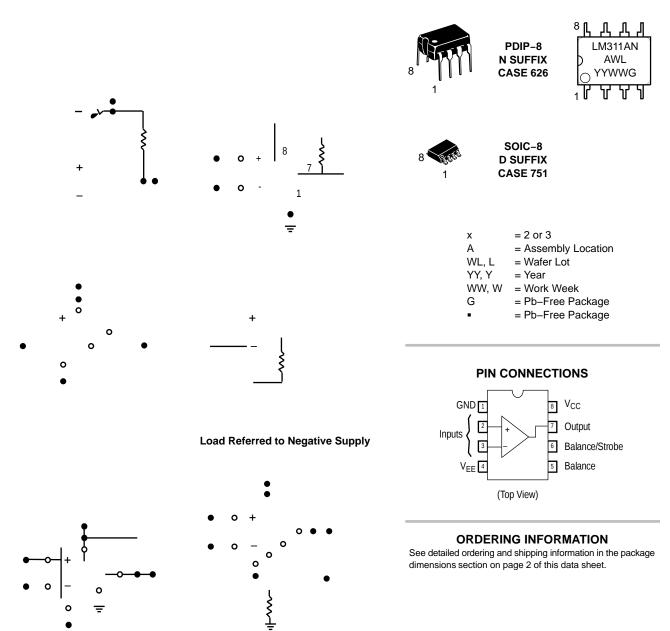

#### MARKING DIAGRAMS

0

Ξ

# LM211, LM311

|                               |                 |     | LM211 |     |     | LM311 |     |      |  |

|-------------------------------|-----------------|-----|-------|-----|-----|-------|-----|------|--|

| Characteristic                | Symbol          | Min | Тур   | Max | Min | Тур   | Max | Unit |  |

| Input Offset Voltage (Note 3) | V <sub>IO</sub> |     |       |     |     |       |     |      |  |

# LM211, LM311

# LM211, LM311

8

### TECHNIQUES FOR AVOIDING OSCILLATIONS IN COMPARATOR APPLICATIONS

When a high speed comparator such as the LM211 is used with high speed input signals and low source impedances, the output response will normally be fast and stable, providing the power supplies have been bypassed (with  $0.1 \,\mu\text{F}$  disc capacitors), and that the output signal is routed well away from the inputs (Pins 2 and 3) and also away from Pins 5 and 6.

However, when the input signal is a voltage ramp or a slow sine wave, or if the signal source impedance is high (1.0 k $\Omega$  to 100 k $\Omega$ ), the comparator may burst into oscillation near the crossing–point. This is due to the high gain and wide bandwidth of comparators like the LM211 series. To avoid oscillation or instability in such a usage, several precautions are recommended, as shown in Figure 16.

The trim pins (Pins 5 and 6) act as unwanted auxiliary inputs. If these pins are not connected to a trim–pot, they should be shorted together. If they are connected to a trim–pot, a 0.01  $\mu$ F capacitor (C1) between Pins 5 and 6 will minimize the susceptibility to AC coupling. A smaller capacitor is used if Pin 5 is used for positive feedback as in Figure 16. For the fastest response time, tie both balance pins to V<sub>CC</sub>.

Certain sources will produce a cleaner comparator output waveform if a 100 pF to 1000 pF capacitor (C2) is connected directly across the input pins. When the signal source is applied through a resistive network, R1, it is usually advantageous to choose R2 of the same value, both for DC and for dynamic (AC) considerations. Carbon, tin–oxide, and metal–film resistors have all been used with good results in comparator input circuitry, but inductive wirewound resistors should be avoided.

When comparator circuits use input resistors (e.g., summing resistors), their value and placement are particularly important. In all cases the body of the resistor should be close to the device or socket. In other words, there should be a very short lead length or printed–circuit foil run between comparator and resistor to radiate or pick up signals. The same applies to capacitors, pots, etc. For example, if  $R1 = 10 \text{ k}\Omega$ , as little as 5 inches of lead between the resistors and the input pins can result in oscillations that are very hard to dampen. Twisting these input leads tightly is the best alternative to placing resistors close to the comparator.

Since feedback to almost any pin of a comparator can result in oscillation, the printed-circuit layout should be engineered thoughtfully. Preferably there should be a groundplane under the LM211 circuitry (e.g., one side of a double layer printed circuit board). Ground, positive supply or negative supply foil should extend between the output and the inputs to act as a guard. The foil connections for the inputs should be as small and compact as possible, and stimuldt sdi8hTs(70m/s)704 interfeed09)56418048940TD-938.3(Tr(12870-res)

**0.010**

SIDE VIEW

CAMBM

NOTE 6

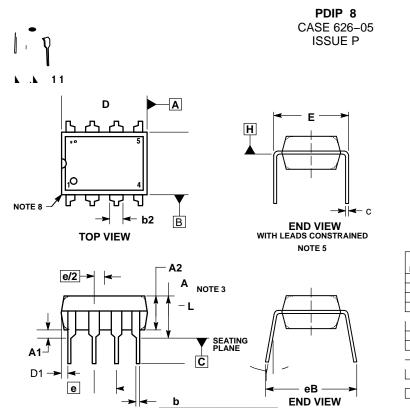

|     | INC       | HES   |      |      |

|-----|-----------|-------|------|------|

| DIM | MIN       | MAX   |      |      |

| Α   |           | 0.210 |      |      |

| A1  | 0.015     |       |      |      |

| A2  | 0.115     | 0.195 | 2.92 | 4.95 |

| b   | 0.014     | 0.022 |      |      |

|     |           |       |      |      |

| С   | 0.008     | 0.014 |      |      |

| D   | 0.355     | 0.400 |      |      |

| D1  | 0.005     |       |      |      |

| Е   | 0.300     | 0.325 |      |      |

|     |           |       |      |      |

| е   | 0.100 BSC |       |      |      |

|     |           |       |      |      |

| L   | 0.115     | 0.150 | 2.92 | 3.81 |

|     |           | 0     |      | 0    |

DATE 22 APR 2015

## GENERIC MARKING DIAGRAM\*

| Ь  | Д   | Д   | Т  |

|----|-----|-----|----|

| XX | хх> | κxx | XX |

| Þ  |     | A١  | NL |

| 0  | Y١  | ſWV | VG |

| T  | Ъ   | Ъ   | Г  |

- XXXX = Specific Device Code

- A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb–Free Package

DATE 16 FEB 2011

SEATING PLANE

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi