# 5 EC ÷2, ÷4/6 Co n r<sup>p C</sup>

#### Description

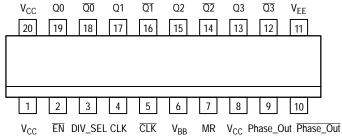

The MC100EL38 is a low skew  $\div 2$ ,  $\div 4/6$  clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, PECL input signal.

The V<sub>BB</sub> pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to V<sub>BB</sub> as a switching reference voltage. V<sub>BB</sub> may also rebias AC coupled inputs. When used, decouple V<sub>BB</sub> and V<sub>CC</sub> via a 0.01  $\mu$ F capacitor and limit current sourcing or sinking to 0.5 mA. When not used, V<sub>BB</sub> should be left open.

The common enable  $(\overline{\text{EN}})$  is synchronous so that the internal dividers will only be enabled/disabled when the internal clock is already in the LOW state. This avoids any chance of generating a runt clock pulse on the internal clock when the device is enabled/disabled as can happen with an asynchronous control. An internal runt pulse could lead to losing synchronization between the internal divider stages. The internal enable flip-flop is clocked on the falling edge of the input clock, therefore, all associated specification limits are referenced to the negative edge of the clock input.

The Phase\_Out output will go HIGH for one clock cycle whenever the  $\div 2$  and the  $\div 4/6$  outputs are both transitioning from a LOW to a HIGH. This output allows for clock synchronization within the system.

Upon startup, the internal flip-flops will attain a random state; therefore, for systems which utilize multiple EL38s, the master reset (MR) input must be asserted to ensure synchronization. For systems which only use one EL38, the MR pin need not be exercised as the internal divider design ensures synchronization between the  $\div$ 2 and the  $\div$ 4/6 outputs of a single device.

- 50 ps Output-to-Output Skew

- Synchronous Enable/Disable

- Master Reset for Synchronization

- ESD Protection:

- 2 kV Human Body Model

- 100 V Machine Model

- The 100 Series Contains Temperature Compensation

- PECL Mode Operating Range:

- $V_{CC} = 4.2 \text{ V}$  to 5.7 V with  $V_{EE} = 0 \text{ V}$

- NECL Mode Operating Range:

- $V_{CC} = 0 V$  with  $V_{EE} = 4.2 V$  to 5.7 V

- Internal 75 kΩ Input Pulldown Resistors on CLK, EN, MR, and DIVSEL

- Q Output will Default LOW with Inputs Open or at  $V_{\rm EE}$

- Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

#### www.onsemi.com

SOIC-20 WB DW SUFFIX CASE 751D-05

- Moisture Sensitivity Level: 3 (Pb-Free)

- For Additional Information, see Application Note <u>AND8003/D</u>

- Flammability Rating:

- UL 94 V 0 @ 0.125 in, Oxygen Index: 28 to 34

- Transistor Count = 388 devices

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant

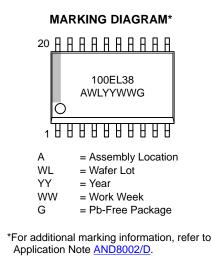

$V_{CC}$  EN DIV\_SEL CER CER V<sub>BB</sub> Mik  $V_{CC}$  Phase\_out Phase\_of \* All V<sub>CC</sub> pins are tied together on the die.

Warning: All  $V_{CC}$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

Figure 1. Pinout Assignment (Top View)

#### Table 1. PIN DESCRIPTION

| Pin                                          | Function                           |

|----------------------------------------------|------------------------------------|

| CLK, <u>CLK</u>                              | ECL Diff Clock Inputs              |

| $Q_0, Q_{1;} \overline{Q_0}, \overline{Q_1}$ | ECL Diff +2 Outputs                |

| $Q_2, Q_{3;} \overline{Q_2}, \overline{Q_3}$ | ECL Diff ÷4/6 Outputs              |

| ĒN                                           | ECL Sync Enable Input              |

| MR                                           | ECL Master Reset Input             |

| DIVSEL                                       | ECL Frequency Select Input         |

| Phase_Out, Phase_Out                         | ECL Phase Sync Diff. Signal Output |

| V <sub>BB</sub>                              | Reference Voltage Output           |

| V <sub>CC</sub>                              | Positive Supply                    |

| V <sub>EE</sub>                              | Negative Supply                    |

#### Table 2. FUNCTION TABLE

| CLK | EN | MR | Function                              |

|-----|----|----|---------------------------------------|

| Z   | L  | L  | Divide Hold $Q_{0-3}$ Reset $Q_{0-3}$ |

| ZZ  | H  | L  |                                       |

| X   | X  | H  |                                       |

Z = Low-to-High Transition

ZZ = High-to-Low Transition

X = Don't Care

| DIVSEL | $Q_2, Q_3 OUTPUTS$ |  |  |  |  |

|--------|--------------------|--|--|--|--|

| L      | Divide by 4        |  |  |  |  |

| H      | Divide by 6        |  |  |  |  |

### MAXIMUM RATINGS

| Parameter                                          | Condition 1                                    | Condition 2                                                           | Rating      | Unit |

|----------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------|-------------|------|

| PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                                                       | 8           | V    |

| NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V                          |                                                                       | -8          | V    |

| PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{l} V_{I} \leq V_{CC} \\ V_{I} \geq V_{EE} \end{array}$ | 6<br>-6     | V    |

| Output Current                                     | Continuous<br>Surge                            |                                                                       | 50<br>100   | MA   |

| V <sub>BB</sub> Sink/Source                        |                                                |                                                                       | ± 0.5       | mA   |

| Operating Temperature Range                        |                                                |                                                                       | -40 to +85  | °C   |

| Storage Temperature Range                          |                                                |                                                                       | -65 to +150 | °C   |

| Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | SOIC-20 WB                                                            | 90<br>60    | °C/W |

| Thermal Resistance (Junction-to-Case)              | Standard Board                                 | SOIC-20 WB                                                            | 30 to 35    |      |

|                 |                              | -40°C |       |       | 25°C  |       |       | 85°C  |      |      |      |

|-----------------|------------------------------|-------|-------|-------|-------|-------|-------|-------|------|------|------|

| Symbol          | Characteristic               | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current         |       | 50    | 60    |       | 50    | 60    |       | 54   | 65   | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2) | -1085 | -1005 | -880  | -1025 | -955  | -880  | -1025 | -955 | -880 | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)  | -1830 | -1695 | -1555 | -1810 | -1705 | -1620 | -     | -    | -    |      |

Table 5. 100EL SERIES NECL DC CHARACTERISTICS ( $V_{CC} = 0.0 \text{ V}$ ;  $V_{EE} = -5.0 \text{ V}$  (Note 1))

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi