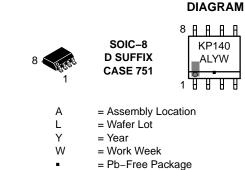

MARKING

# 3.3 ECL -F \_ D 0

# MC100E 140

### Description

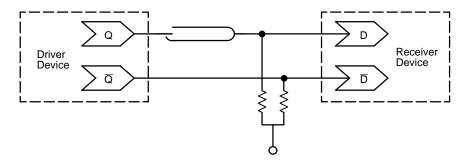

The MC100EP140 is a three state phase frequency detector intended for phase locked loop applications which require a minimum amount of phase and frequency difference at lock. Since the part is designed with fully differential internal gates, the noise is reduced throughout the circuit, especially at high speeds. The basic operation of a Phase/Frequency Detector (PFD) is to "compare" an incoming signal (feedback) to a set reference signal. When the Reference (R) and Feedback (FB) inputs are unequal in frequency and/or phase, the differential UP (U) and DOWN (D) outputs will provide pulse streams which, when subtracted and integrated, provide an error voltage for control of a VCO. Detector states of operation are shown in the Figure 2 and the State Table.

The typical output amplitude of the EP140 is 400 mV, allowing faster switching time and greater bandwidth. For proper operation, the input edge rate of the R and FB inputs should be less than 5 ns.

More information on Phase Lock Loop operation and application can be found in AND8040.

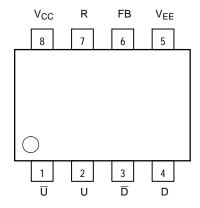

The pinout is shown in Figure 1, the logic diagram in Figure 3, and the typical termination in Figure 5.

### Features

- 500 ps Typical Propagation Delay

- Maximum Frequency > 2.1 GHz Typical

- Fully Differential Internally

- Advanced High Band Output Swing of 400 mV

- Transfer Gain: 1.0 mV/Degree at 1.4 GHz 1.2 mV/Degree at 1.0 GHz

- Rise and Fall Time: 100 ps Typical

- The 100 Series Contains Temperature Compensation

- PECL Mode Operating Range: V<sub>CC</sub> = 3.0 V to 3.6 V with V<sub>EE</sub> = 0 V

- NECL Mode Operating Range:  $V_{CC} = 0 V$ with  $V_{EE} = 3.0 V$  to 3.6 V

- Open Input Default State

- These are Pb Free Devices

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

Figure 1. 8-Lead Pinout (Top View)

#### Table 1. PIN DESCRIPTION

| PIN             | FUNCTION                  |

|-----------------|---------------------------|

| D, D            | Differential Down Outputs |

| U, <del>U</del> | Differential Up Outputs   |

| R*              | ECL Reference Input       |

| FB*             | ECL Feedback Input        |

| V <sub>CC</sub> | Positive Supply           |

| V <sub>EE</sub> | Negative Supply           |

#### Table 2. STATE TABLE

PHASE DETECTOR STATE

Figure 2. Phase Detector Logic Model

#### Table 3. ATTRIBUTES

| Characteristics                  | Value |  |  |  |

|----------------------------------|-------|--|--|--|

| Internal Input Pulldown Resistor | 75 k  |  |  |  |

|                 |                                   | -40°C |       |       | 25°C  |       |       | 85°C  |       |       |      |

|-----------------|-----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic                    | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Power Supply Current              | 45    | 65    | 85    | 50    | 70    | 90    | 53    | 73    | 93    | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 5)      | -1075 | -950  | -825  | -1025 | -900  | -775  | -1000 | -875  | -750  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 5)       | -1525 | -1400 | -1275 | -1500 | -1375 | -1250 | -1475 | -1350 | -1225 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage (Single-Ended) | -1225 |       | -880  | -1225 |       | -880  | -1225 |       | -880  | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)  | -1945 |       | -1625 | -1945 |       | -1625 | -1945 |       | -1625 | mV   |

| I <sub>IH</sub> | Input HIGH Current                |       |       | 150   |       |       | 150   |       |       | 150   | r    |

T

-

Table 6. 100EP DC CHARACTERISTICS, NECL  $V_{CC}$  = 0 V,  $V_{EE}$  = –3.6 V to –3.0 V (Note 4)

-

Figure 5. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020/D – Termination of ECL Logic Devices.)

DATE 16 FEB 2011

SEATING PLANE

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi