Table 8. AC CHARACTERISTICS  $V_{CCI} = 3.0 \text{ V}$  to 3.6 V;  $V_{CCO} = 1.6 \text{ V}$  to 2.0 V, GND = 0 V (Note 5)

|                                      |                                                                                       | 0                 |                   | 0 C        |                   | 25 C              |             | 85 C              |                   |              |                |

|--------------------------------------|---------------------------------------------------------------------------------------|-------------------|-------------------|------------|-------------------|-------------------|-------------|-------------------|-------------------|--------------|----------------|

| Symbol                               | Characteristic                                                                        | Min               | Тур               | Max        | Min               | Тур               | Max         | Min               | Тур               | Max          | Unit           |

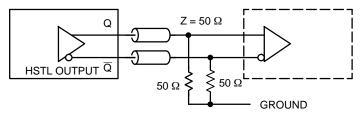

| V <sub>Opp</sub>                     | Differential Output Voltage (Figure 3)  fout < 100 MHz fout < 500 MHz fout < 750 MHz  | 600<br>600<br>450 | 850<br>750<br>575 |            | 600<br>600<br>450 | 850<br>750<br>575 |             | 600<br>600<br>450 | 850<br>750<br>575 |              | mV<br>mV<br>mV |

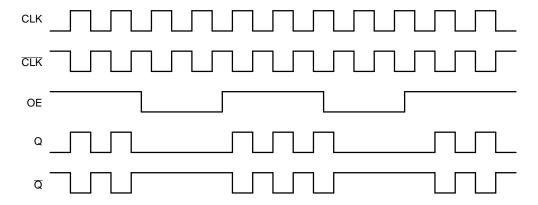

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>(Differential Configuration)<br>LVPECL_CLK to Q<br>HSTL_CLK to Q | 680<br>690        | 800<br>830        | 930<br>990 | 700<br>700        | 820<br>850        | 950<br>1000 | 780<br>790        | 920<br>950        | 1070<br>1110 | ps<br>ps       |

t

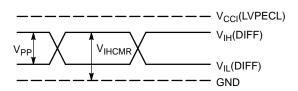

Figure 4. LVPECL Differential Input Levels

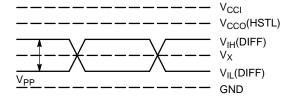

Figure 5. HSTL Differential Input Levels

Figure 6. HSTL Output Termination and AC Test Reference

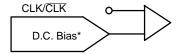

\*Must be CLK/ $\overline{\text{CLK}}$  common mode voltage: (( $V_{IH} + V_{IL}$ )/2).

Figure 7. Single-Ended CLK/CLK Input Configuration

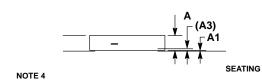

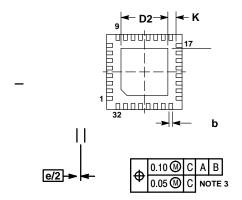

## **MECHANICAL CASE OUTLINE**

**PACKAGE DIMENSIONS**

**DATE 23 OCT 2013**

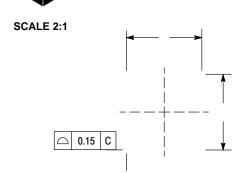

#### RECOMMENDED

|    |      | MAX         |  |

|----|------|-------------|--|

|    | 0.80 | 1.00        |  |

| A1 |      | 0.05        |  |

| A3 | 0.20 | R <u>EF</u> |  |

| b  | 0.18 | 0.30        |  |

| D  | 5.00 | BSC         |  |

| D2 | 2.95 | 3.25        |  |

| E  | 5.00 | BSC         |  |

| E2 | 2.95 | 3.25        |  |

| е  | 0.50 | BSC         |  |

| K  | 0.20 |             |  |

| ٦  | 0.30 | 0.50        |  |

| L1 |      | 0.15        |  |

XXXXXXX

XXXXXXX

AWLYYWW=

Free indicator, "G" or

| DOCUMENT NUMBER: | 98AON20032D |  |

|------------------|-------------|--|

|                  |             |  |