# onsemi

# 2.5 V/3.3 V ECL 2-Input Differential AND/NAND MC100LVEP05

Description

The MC100LVEP05 is a 2 input differential AND/NAND gate. The MC100LVEP05 is the low voltage version of the MC100EP05 and is functionally equivalent to the EL05 and LVEL05 devices. With AC performance much faster than the LVEL05 device, the MC100LVEP05 is ideal for low voltage applications requiring the fastest AC performance available.

The 100 Series contains temperature compensation.

#### Features

220 ps Typical Propagation Delay Input Clock Frequency > 3 GHz 0.2 ps Typical RMS Random Clock Period Jitter LVPECL Mode Operating Range:  $V_{CC} = 2.375$  V to 3.6 V with  $V_{EE} = 0$  V NECL Mode Operating Range:  $V_{CC} = 0$  V with  $V_{EE} = 2.375$  V to 3.6 V Open Input Default State Q Output Will Default LOW with Inputs Open These Device are Pb Free, Halogen Free and are RoHS Compliant

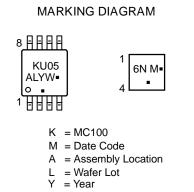

TSSOP-8 DT SUFFIX CASE 948R DFN8 MN SUFFIX CASE 506AA

- W = Work Week

- = Pb–Free Package

(Note: Microdot may be in either location) \*For additional marking information, refer to Application Note <u>AND8002/D</u>.

#### ORDERING INFORMATION

| Device           | Package              | Shipping <sup>†</sup> |

|------------------|----------------------|-----------------------|

| MC100LVEP05DTG   | TSSOP-8<br>(Pb-Free) | 100 Units /<br>Tube   |

| MC100LVEP05DTR2G | TSSOP-8<br>(Pb-Free) | 2500 /<br>Tape & Reel |

| MC100LVEP05MNTXG | DFN8<br>(Pb-Free)    | 1000 /<br>Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

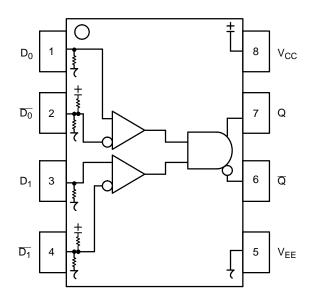

Figure 1. 8–Lead Pinout (Top View) and Logic Diagram

#### Table 1. PIN DESCRIPTION

| Pin                                  | Function         |

|--------------------------------------|------------------|

| D0*, D1*, <u>D0</u> **, <u>D1</u> ** | ECL Data Inputs  |

| $Q, \overline{Q}$                    | ECL Data Outputs |

| V <sub>CC</sub>                      | Positive Supply  |

| V <sub>EE</sub>                      | Negative Supply  |

| EP                                   | -                |

#### Table 4. MAXIMUM RATINGS

| Symbol           | Parameter                                          | Condition 1                                    | Condition 2                                                           | Rating      | Unit       |

|------------------|----------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------|-------------|------------|

| V <sub>CC</sub>  | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                                                       | 6           | V          |

| $V_{EE}$         | NECL Mode Power Supply                             | $V_{CC} = 0 V$                                 |                                                                       | -6          | V          |

| VI               | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{l} V_{I} \leq V_{CC} \\ V_{I} \geq V_{EE} \end{array}$ | 6<br>-6     | V<br>V     |

| I <sub>out</sub> | Output Current                                     | Continuous<br>Surge                            |                                                                       | 50<br>100   | mA<br>mA   |

| T <sub>A</sub>   | Operating Temperature Range                        |                                                |                                                                       | -40 to +85  | С          |

| T <sub>stg</sub> | Storage Temperature Range                          |                                                |                                                                       | -65 to +150 | С          |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | TSSOP-8<br>TSSOP-8                                                    | 185<br>140  | C/W<br>C/W |

| $\theta_{JC}$    | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | TSSOP-8                                                               | 41 to 44    | C/W        |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | DFN8<br>DFN8                                                          | 129<br>84   | C/W<br>C/W |

| θJC              | Thermal Resistance (Junction-to-Case)              | (Note 2)                                       | DFN8                                                                  | 35 to 40    |            |

|                 |                      | -40 C |     | 25 C |     |     | 85 C |     |     |     |      |

|-----------------|----------------------|-------|-----|------|-----|-----|------|-----|-----|-----|------|

| Symbol          | Characteristic       | Min   | Тур | Max  | Min | Тур | Max  | Min | Тур | Max | Unit |

| I <sub>EE</sub> | Power Supply Current | 15    | 25  | 32   | 17  |     |      |     |     |     |      |

|                                        |                                                                  |     | -40 C |      |     | 25 C |      |     | 85 C |      |      |

|----------------------------------------|------------------------------------------------------------------|-----|-------|------|-----|------|------|-----|------|------|------|

| Symbol                                 | Characteristic                                                   | Min | Тур   | Max  | Min | Тур  | Max  | Min | Тур  | Max  | Unit |

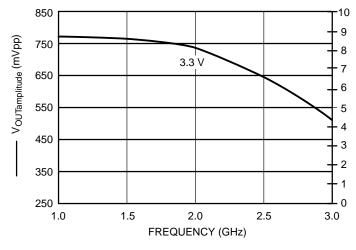

| f <sub>max</sub>                       | Maximum Frequency<br>(Figure 2)                                  | 3.0 |       |      | 3.0 |      |      | 3.0 |      |      | GHz  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay to<br>Output Differential                      | 160 | 210   | 260  | 170 | 220  | 270  | 210 | 260  | 320  | ps   |

| <b>t</b> JITTER                        | RMS Random Clock Jitter $f_{in} \leq 3.0 \text{ GHz}$ (Figure 2) |     | 0.2   | 1    |     | 0.2  | 1    |     | 0.2  | 1.5  | ps   |

| V <sub>PP</sub>                        | Input Voltage Swing<br>(Differential Configuration)              | 150 | 800   | 1200 | 150 | 800  | 1200 | 150 | 800  | 1200 | mV   |

| t <sub>r</sub><br>t <sub>f</sub>       | Output Rise/Fall Times Q<br>(20% - 80%)                          | 70  | 120   | 170  | 80  | 130  | 180  | 100 | 150  | 200  | ps   |

| Table 8. AC CHARACTERISTICS | $SV_{CC} = 0$ V; $V_{EE} = -2.375$ V to $-3.6$ V | V or $V_{CC} = 2.375$ V to 3.6 V; $V_{EE} = 0$ V (Note 13) |

|-----------------------------|--------------------------------------------------|------------------------------------------------------------|

|-----------------------------|--------------------------------------------------|------------------------------------------------------------|

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

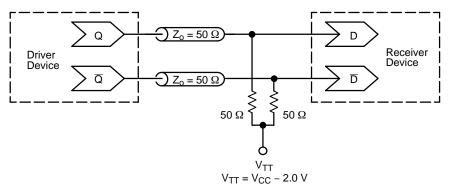

13. Measured using a 750 mV source, 50% duty cycle clock source. All loading with 50  $\Omega$  to V<sub>CC</sub> – 2.0 V.

Figure 2. F<sub>max</sub> @ 25°C

#### Resource Reference of Application Notes

- AN1405/D ECL Clock Distribution Techniques

- AN1406/D Designing with PECL (ECL at +5.0 V)

- AN1503/D ECLinPS™ I/O SPiCE Modeling Kit

- AN1504/D Metastability and the ECLinPS Family

- AN1568/D Interfacing Between LVDS and ECL

- AN1672/D The ECL Translator Guide

- AND8001/D Odd Number Counters Design

- AND8002/D Marking and Date Codes

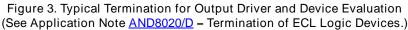

- AND8020/D Termination of ECL Logic Devices

- AND8066/D Interfacing with ECLinPS

- AND8090/D AC Characteristics of ECL Devices

ECLinPS is registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

DF 82x2, 0.5 CASE 506AA ISSUE F

DATE 04 MAY 2016

1 CA E 4:1

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb–Free strategy and soldering details, please download the **m** e Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

**TSSOP 8 3.00x3.00x0.95** CASE 948R-02 ISSUE A

DATE 07 APR 2000

|     | MILLIN | IETERS | INCHES |       |  |  |

|-----|--------|--------|--------|-------|--|--|

| DIM | MIN    | MAX    | MIN    | MAX   |  |  |

| Α   | 2:0    | 3.10   | 0.114  | 0.122 |  |  |

| В   |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

|     |        |        |        |       |  |  |

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi