# onsemi

# 2.5 V/3.3 V ECL 2, 4, 8 Clock Generation Chip

# MC100LVEP34

### Description

The MC100LVEP34 is a low skew 2, 4, 8 clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The  $V_{BB}$  pin, an internally generated voltage supply, is available to this device only. For single ended input conditions, the unused differential input is connected to  $V_{BB}$  as a switching reference voltage.  $V_{BB}$  may also rebias AC coupled inputs. When used, decouple  $V_{BB}$  and  $V_{CC}$  via a 0.01 µF capacitor and limit current sourcing or sinking to 0.5 mA. When not used,  $V_{BB}$  should be left open.

The common enable  $(\overline{EN})$  is synchronous so that the internal

Warning: All  $V_{CC}$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

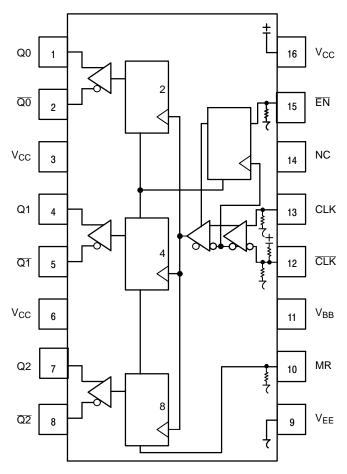

| Figure 1. 16-Lead Pinout (Top | View) and Logic Diagram |

|-------------------------------|-------------------------|

|-------------------------------|-------------------------|

| Table 1. PIN DESCRIPTION |

|--------------------------|

|--------------------------|

| Pin             | Function                 |  |  |  |

|-----------------|--------------------------|--|--|--|

| CLK*, CLK**     | ECL Diff Clock Inputs    |  |  |  |

| EN*             | ECL Sync Enable          |  |  |  |

| MR*             | ECL Master Reset         |  |  |  |

| Q0, <u>Q0</u>   | ECL Diff 2 Outputs       |  |  |  |

| Q1, <u>Q1</u>   | ECL Diff 4 Outputs       |  |  |  |

| Q2, <u>Q2</u>   | ECL Diff 8 Outputs       |  |  |  |

| V <sub>BB</sub> | Reference Voltage Output |  |  |  |

| V <sub>CC</sub> | Positive Supply          |  |  |  |

| V <sub>EE</sub> | Negative Supply          |  |  |  |

| NC              | No Connect               |  |  |  |

$^{*}$  Pins will default LOW when left open.  $^{**} \rm Pins$  will default to  $\rm V_{\rm CC}/2$  when left open.

## **Table 2. FUNCTION TABLE**

| CLK          | EN  | MR    | FUNCTION                                                  |

|--------------|-----|-------|-----------------------------------------------------------|

| Z<br>ZZ<br>X | LHX | IJIJĬ | Divide<br>Hold Q <sub>0–3</sub><br>Reset Q <sub>0–3</sub> |

Z = Low-to-High Transition ZZ = High-to-Low Transition

# Table 3. ATTRIBUTES

| Characteristics                                                             | Value                       |

|-----------------------------------------------------------------------------|-----------------------------|

| Internal Input Pulldown Resistor                                            | 75 kΩ                       |

| Internal Input Pullup Resistor                                              | 37.5 kΩ                     |

| ESD Protection<br>Human Body Model<br>Machine Model<br>Charged Device Model | > 2 kV<br>> 200 V<br>> 2 kV |

| Moisture Sensitivity, Indefinite Time Out of Drypack (Note 1)               | Level 1                     |

| Flammability Rating<br>Oxygen Index: 28 to 34                               | UL 94 V–O @ 0.125 in        |

| Transistor Count                                                            | 210 Devices                 |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test                      | ·                           |

1. For additional Moisture Sensitivity information, refer to Application Note <u>AND8003/D</u>.

# Table 4. MAXIMUM RATINGS

| Symbol | Parameter | Condition 1 | Condition 2 | Rating | Unit |

|--------|-----------|-------------|-------------|--------|------|

|        |           |             |             |        |      |

### -40 C 25 C 85 C Min Тур Max Min Тур Max Min Тур Max Unit Symbol Characteristic $I_{EE}$ Power Supply Current 40 50 60 40 50 60 42 52 62 mΑ 1355 1480 1605 1355 1480 1605 1355 1480 1605 mV VOH Output HIGH Voltage (Note 3) Output LOW Voltage (Note 3) VOL 505 680 900 505 680 900 505 680 900 mV Input HIGH Voltage (Single–Ended) (Note 4) VIH 1335 1620 1335 1620 1275 1620 mV V Input LOW Voltage (Single-Ended) 505 900 505 900 505 900 mV (Note 4)

### Table 5. 100EP DC CHARACTERISTICS, PECL $V_{CC}$ = 2.5 V, $V_{EE}$ = 0 V (Note 2)

VIHCMR

Input HIGH Voltage Common Mode Range (Diffe4.09.e 254.494 61sx1 .9070 0 8 105.4488 585.2977 Tm-0023 Tc.027.5402 Tm-0019 Tc.005O8091 .9071 refB8 0 0 8 105.4488 585

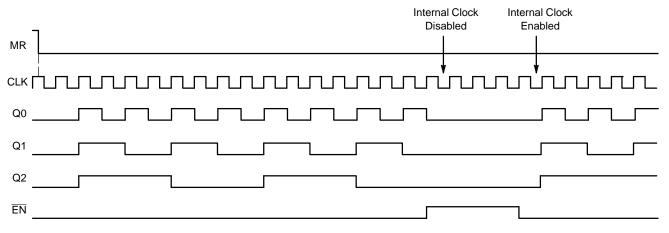

There are two distinct functional relationships between the Master Reset and Clock:

CASE 1: If the MR is de-asserted (H–L), while the Clock is still high, the outputs will follow the second ensuing clock rising edge.

#

The  $\overline{EN}$  signal will "freeze" the internal divider flip flops on the first falling edge of CLK after its assertion. The internal divider flip flops will maintain their state during the freeze. When  $\overline{EN}$  is deasserted (LOW), and after the next falling edge of CLK, then the internal divider flip flops will "unfreeze" and continue to their next state count with proper phase relationships.

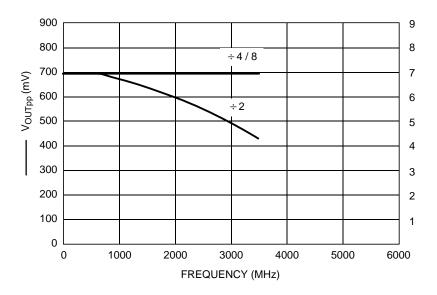

Figure 4. F<sub>max</sub>

Figure 5. Typical Termination for Output Driver and Device Evaluation

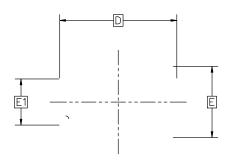

### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

DATE 18 OCT 2024

- DIMENSIONS D AND E1 DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.1<sup>r</sup>

**b** DIMENSION AT MAXIMUM MATE

nm TOTAL IN EXCESS OF THE

<u>top view</u>

### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

### DATE 18 OCT 2024

### GENERIC MARKING DIAGRAM\*

| 16 | A | - A | - A | - A | - A | A   | A   | E |

|----|---|-----|-----|-----|-----|-----|-----|---|

|    |   | XX) | (X) | XX  | XX) | XX) | XX  | G |

|    |   | XX  | XX  | XX  | XX) | XX  | XX) | X |

|    | 0 |     | A١  | NĽ  | ΥW  | /W  |     |   |

| 1  | Ŧ | H   | H   | H   | H   | Н   | H   | Ъ |

XXXXX = Specific Device Code

A = Assembly Location

- WL = Wafer Lot

- Y = Year

- WW = Work Week

- G = Pb Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42566B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1.27P                                                                                                                                                                    |  | PAGE 2 OF 2 |  |  |

|                  |                                                                                                                                                                                                 |  |             |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

SCALE 2:1

TSSOP-16 WB CASE 948F ISSUE B

DATE 19 OCT 2006

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi