# 5 V ECL D Flip-Flop with Set and Reset MC10EL31, MC100EL31

### **Description**

The MC10EL/100EL31 is a D flip-flop with set and reset. The device is functionally equivalent to the E131 device with higher performance capabilities. With propagation delays and output transition times significantly faster than the E131, the EL31 is ideally suited for those applications which require the ultimate in AC performance.

Both set and reset inputs are asynchronous, level triggered signals. Data enters the master portion of the flip-flop when clock is LOW and

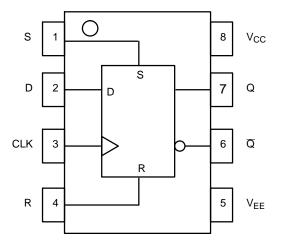

Figure 1. Logic Diagram and Pinout Assignment

### Table 1. TRUTH TABLE

| D | S* | R* | CLK | q     |

|---|----|----|-----|-------|

| L | L  | L  | Z   | L     |

| H | L  | L  | Z   | Н     |

| X | Н  | L  | X   | Н     |

| X | L  | Н  | X   | L     |

| X | Н  | н  | X   | Undef |

Z = LOW to HIGH Transition

### **Table 2. PIN DESCRIPTION**

| PIN                                                              | FUNCTION                                                                                                      |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| S<br>D<br>R<br>CLK<br>Q, Q<br>V <sub>CC</sub><br>V <sub>EE</sub> | ECL Set Input ECL Data Input ECL Reset Input ECL Clock Input ECL Data Outputs Positive Supply Negative Supply |

### **Table 3. MAXIMUM RATINGS**

| Symbol           | Parameter                                          | Condition 1                      | Condition 2                                  | Rating      | Unit |

|------------------|----------------------------------------------------|----------------------------------|----------------------------------------------|-------------|------|

| V <sub>CC</sub>  | PECL Mode Power Supply-                            | V <sub>EE</sub> = 0 V            |                                              | 8           | V    |

| V <sub>EE</sub>  | NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V            |                                              | -8          | V    |

| VI               | PECL Mode Input Voltage<br>NECL Mode Input Voltage | $V_{EE} = 0 V$<br>$V_{CC} = 0 V$ | $V_{I} \Omega V_{CC} V_{I} \emptyset V_{EE}$ | 6<br>-6     | V    |

| l <sub>out</sub> | Output Current                                     | Continuous<br>Surge              |                                              | 50<br>100   | mA   |

| T <sub>A</sub>   | Operating Temperature Range                        |                                  |                                              | -40 to +85  | ∀C   |

| T <sub>stg</sub> | Storage Temperature Range                          |                                  |                                              | -65 to +150 | AC   |

| $\theta_{JA}$    |                                                    |                                  |                                              |             |      |

<sup>\*</sup> Pins will default low when left open.

| Table 4. 10EL SERIES PECL DC CHARACTERISTICS |  |  |  |  |  |  |  |

|----------------------------------------------|--|--|--|--|--|--|--|

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

Table 7. 100EL SERIES NECL DC CHARACTERISTICS ( $V_{CC} = 0 \text{ V}$ ;  $V_{EE} = -5.0 \text{ V}$ ) (Note 1)

|                 |                              | -40∀C |       | 25∀C  |       | 85∀C  |       |       |       |       |      |

|-----------------|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic               | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Power Supply Current         |       | 27    | 32    |       | 27    | 32    |       | 31    | 37    | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2) | -1085 | -1005 | -880  | -1025 | -955  | -880  | -1025 | -955  | -880  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)  | -1830 | -1695 | -1555 | -1810 | -1705 | -1620 | -1810 | -1705 | -1620 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage           | -1165 |       | -880  | -1165 |       | -880  | -1165 |       | -880  | mV   |

| $V_{IL}$        | Input LOW Voltage            | -1810 |       | -1475 | -1810 |       | -1475 | -1810 |       | -1475 | mV   |

| I <sub>IH</sub> | Input HIGH Current           |       |       | 150   |       |       | 150   |       |       | 150   | μΑ   |

I1810

### **Resource Reference of Application Notes**

AN1405/D – ECL Clock Distribution Techniques

AN1406/D – Designing with PECL (ECL at +5.0 V)

AN1503/D – ECLinPS™ I/O SPiCE Modeling Kit

AN1504/D – Metastability and the ECLinPS Family

AN1568/D – Interfacing Between LVDS and ECL

AND8001/D - The ECL Translator Guide

AND8001/D - Odd Number Counters Design

AND8002/D - Marking and Date Codes

AND8020/D - Termination of ECL Logic Devices

AND8066/D - Interfacing with ECLinPS

AND8090/D - AC Characteristics of ECL Devices

DATE 16 FEB 2011

| onsemi | onsemi | emi | onsemi | onsemi | onsemi<br>onsemi | onsemi |

|--------|--------|-----|--------|--------|------------------|--------|

|        |        |     |        |        |                  |        |