### Description

The MC10/100EL34 is a low skew  $\div 2, \div 4, \div 8$  clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The V<sub>BB</sub> pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to V<sub>BB</sub> as a switching reference voltage. V<sub>BB</sub> may also rebias AC coupled inputs. When used, decouple V<sub>BB</sub> and V<sub>CC</sub> via a 0.01 µF capacitor and limit current sourcing or sinking to 0.5 mA. When not used, V<sub>BB</sub> should be left open.

The common enable  $(\overline{EN})$  is synchronous so that the internal

## Table 4. MAXIMUM RATINGS

| Symbol          | Parameter              | Condition 1    | Condition 2 | Rating | Unit |

|-----------------|------------------------|----------------|-------------|--------|------|

| V <sub>CC</sub> | PECL Mode Power Supply | $V_{EE} = 0 V$ |             | 8      | V    |

| V <sub>EE</sub> | NECL Mode Power Supply | $V_{CC} = 0 V$ |             | -8     | V    |

| VI              |                        |                |             |        | -    |

|                 |                        |                |             |        |      |

|                 |                                                                                  | 40°C  |       |       | 25°C  |       |       | 85°C  |       |       |      |

|-----------------|----------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic                                                                   | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| $I_{EE}$        | Power Supply Current                                                             |       |       | 39    |       |       | 39    |       |       | 42    | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2)                                                     | -1085 | -1005 | -880  | -1025 | -955  | -880  | -1025 | -955  | -880  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)                                                      | -1830 | -1695 | -1555 | -1810 | -1705 | -1620 | -1810 | -1705 | -1620 | mV   |

| VIH             | Input HIGH Voltage (Single-Ended)                                                | -1165 |       | -880  | -1165 |       | -880  | -1165 |       | -880  | mV   |

| VIL             | Input LOW Voltage (Single-Ended)                                                 | -1810 |       | -1475 | -1810 |       | -1475 | -1810 |       | -1475 | mV   |

| $V_{BB}$        | Output Voltage Reference                                                         | -1.38 |       | -1.26 | -1.38 |       | -1.26 | -1.38 |       | -1.26 | V    |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 3) | -2.8  |       | -0.4  | -2.8  |       | -0.4  | -2.8  |       | -0.4  | V    |

| I <sub>IH</sub> | Input HIGH Current                                                               |       |       | 150   |       |       | 150   |       |       | 150   | μΑ   |

| ۱ <sub>IL</sub> | Input LOW Current                                                                | 0.5   |       |       | 0.5   |       |       | 0.5   |       |       | μΑ   |

### Table 8. 100EL SERIES NECL DC CHARACTERISTICS (V<sub>CC</sub> = 0 V; V<sub>EE</sub> = -5.0 V (Note 1))

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary +0.8 V / -0.5 V.

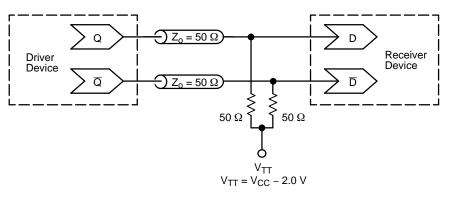

Outputs are terminated through a 50 Ω resistor to V<sub>CC</sub> - 2.0 V.

V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, V<sub>IHCMR</sub> max varies 1:1 with V<sub>CC</sub>. The V<sub>IHCMR</sub> range is referenced to the most positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the specified range and the peak-to-peak voltage lies between V<sub>PP</sub>min and 1 V.

|                                      |                                                               | 40°C       |     |              | 25°C       |     |              | 85°C       |     |              |      |

|--------------------------------------|---------------------------------------------------------------|------------|-----|--------------|------------|-----|--------------|------------|-----|--------------|------|

| Symbol                               | Characteristic                                                | Min        | Тур | Max          | Min        | Тур | Max          | Min        | Тур | Мах          | Unit |

| fmax                                 | Maximum Toggle Frequency                                      | 1.1        |     |              | 1.1        |     |              | 1.1        |     |              | GHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation<br>CLK to Q0<br>Delay to<br>CLK to Q1,2<br>Output | 960<br>900 |     | 1200<br>1140 | 960<br>900 |     | 1200<br>1140 | 970<br>910 |     | 1210<br>1150 | ps   |

|                                      | MR to Q                                                       | 750        |     | 1060         | 750        |     | 1060         | 790        |     | 1090         |      |

| t <sub>SKEW</sub>                    | Within-Device Skew (Note 2)                                   |            | 100 |              |            | 100 |              |            | 100 |              | ps   |

| t <sub>JITTER</sub>                  | Cycle-to-Cycle Jitter                                         |            | 1.0 |              |            | 1.0 |              |            | 1.0 |              | ps   |

| t <sub>S</sub>                       | Setup Time EN                                                 | 400        |     |              | 400        |     |              | 400        |     |              | ps   |

| t <sub>H</sub>                       | Hold Time EN                                                  | 250        |     |              | 250        |     |              | 250        |     |              | ps   |

| t <sub>RR</sub>                      | Set/Reset Recovery                                            | 400        | 200 |              | 400        | 200 |              | 400        | 200 |              | ps   |

| V <sub>PP</sub>                      | Input Swing (Note 3)                                          | 150        |     | 1000         | 150        |     | 1000         | 150        |     | 1000         | mV   |

| t <sub>r</sub><br>t <sub>f</sub>     | Output Rise/Fall Times Q<br>(20% – 80%)                       | 225        |     | 475          | 225        |     | 475          | 225        |     | 475          | ps   |

### Table 9. AC CHARACTERISTICS ( $V_{CC} = 5.0 \text{ V}$ ; $V_{EE} = 0.0 \text{ V}$ or $V_{CC} = 0.0 \text{ V}$ ; $V_{EE} = -5.0 \text{ V}$ (Note 1))

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

1. 10 Series: V<sub>EE</sub> can vary +0.06 V / -0.5 V.

100 Series:  $\overline{V_{EE}}$  can vary +0.8 V / -0.5 V.

2. Within-device skew is defined as identical transitions on similar paths through a device.

3. VPPmin is minimum input swing for which AC parameters guaranteed. The device has a DC gain of ~40.

There are two distinct functional relationships between the Master Reset and Clock:

CASE 1: If the MR is De-asserted (H L), While the Clock is Still High, the Outputs will Follow the First Ensuing Clock Rising Edge.

## CASE 2: If the MR is De asserted (H Lass State the HCLo); A fies fire (Distion leads Library, shido ned Low, the

The  $\overline{EN}$  signal will "freeze" the internal divider flip flops on the first falling edge of CLK after its assertion. The internal divider flip flops will maintain their state during the freeze. The  $\overline{EN}$  is deasserted (LOW), and after the next falling edge of CLK, then the internal divider flip flops will "unfreeze" and continue to their next state count with proper phase relationships.

**Resource Reference of Application Notes**

| AN1405/D  | - | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | - | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | - | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | - | Metastability and the ECLinPS Family        |

| AN1568/D  | - | Interfacing Between LVDS and ECL            |

| AN1672/D  | - | The ECL Translator Guide                    |

| AND8001/D | - | Odd Number Counters Design                  |

| AND8002/D | - | Marking and Date Codes                      |

| AND8020/D | - | Termination of ECL Logic Devices            |

| AND8066/D | - | Interfacing with ECLinPS                    |

| AND8090/D | - | AC Characteristics of ECL Devices           |

|           |   |                                             |

ECLinPS is a trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

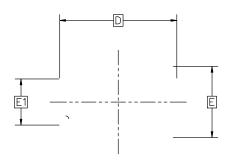

#### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

DATE 18 OCT 2024

- DIMENSIONS D AND E1 DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.1<sup>r</sup>

**b** DIMENSION AT MAXIMUM MATE

nm TOTAL IN EXCESS OF THE

<u>top view</u>

#### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

#### DATE 18 OCT 2024

### GENERIC MARKING DIAGRAM\*

| 16 | A | - A | - A | - A | - A | A   | A.  | E |

|----|---|-----|-----|-----|-----|-----|-----|---|

|    |   | XX) | (X) | XX  | XX) | XX) | (X) | G |

|    |   | XXX | XX  | XX) | XX) | XX  | XX  | X |

|    | 0 |     | A١  | NĽ  | ΥW  | /W  |     |   |

| 1  | Ŧ | H   | H   | H   | H   | Н   | H   | Ъ |

XXXXX = Specific Device Code

A = Assembly Location

- WL = Wafer Lot

- Y = Year

- WW = Work Week

- G = Pb Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42566B Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1                                                                                                                                                                     | PAGE 2 OF 2 |  |  |  |  |

|                  |                                                                                                                                                                                              |             |  |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi