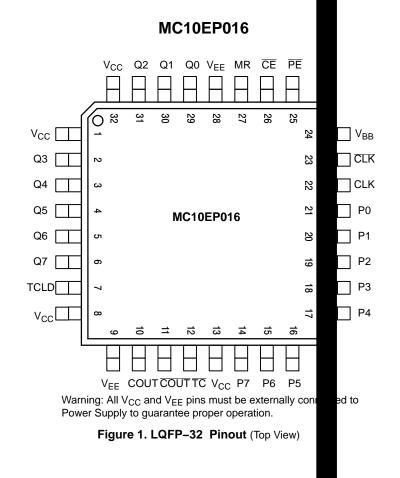

### Table 1. PIN DESCRIPTION

| Pin        | Function                               |  |

|------------|----------------------------------------|--|

| P0-P7*     | ECL Parallel Data (Preset) Inputs      |  |

| Q0-Q7      | ECL Data Outputs                       |  |

| CE*        | ECL Count Enable Control Input         |  |

| PE*        | ECL Parallel Load Enable Control Input |  |

| MR*        | ECL Master Reset                       |  |

| CLK*, CLK* | ECL Differential Clock                 |  |

| TC         | ECL Terminal Count Output              |  |

| CE     | FUNCTION |

|--------|----------|

| X      |          |

| L      |          |

| H<br>X |          |

| X      |          |

ZZ = Clock Pulse (High-to-Low) Z = Clock Pulse (Low-to-High)

### Table 5. MAXIMUM RATINGS

| Table 5.        |                        |                       |             |        |      |  |

|-----------------|------------------------|-----------------------|-------------|--------|------|--|

| Symbol          | Parameter              | Condition 1           | Condition 2 | Rating | Unit |  |

| V <sub>CC</sub> | PECL Mode Power Supply | V <sub>EE</sub> = 0 V |             | 6      |      |  |

|                 | 1                      | 1                     |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

|                 |                        |                       |             |        |      |  |

Table 6. 10EP DC CHARACTERISTICS, PECL  $V_{CC}$  = 3.3 V,  $V_{EE}$  = 0 V (Note 3)

| www.onsemi.com |

|----------------|

|                |

| 6              |

| <b>o</b>       |

|                 |                                                                                   |                 | –40°C |       |       | 25°C  |       |       | 85°C  |       |      |

|-----------------|-----------------------------------------------------------------------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic                                                                    | Min             | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Power Supply Current (Note 11)                                                    | 120             | 160   | 200   | 120   | 160   | 200   | 120   | 160   | 200   | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 12)                                                     | -1135           | -1010 | -885  | -1070 | -945  | -820  | -1010 | -885  | -760  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 12)                                                      | -1935           | -1810 | -1685 | -1870 | -1745 | -1620 | -1810 | -1685 | -1560 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage (Single–Ended)                                                 | -1210           |       | -885  | -1145 |       | -820  | -1085 |       | -760  | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)                                                  | -1935           |       | -1610 | -1870 |       | -1545 | -1810 |       | -1485 | mV   |

| $V_{BB}$        | Output Voltage Reference                                                          | -1510           | -1410 | -1310 | -1445 | -1345 | -1245 | -1385 | -1285 | -1185 | mV   |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 13) | V <sub>EE</sub> | +2.0  | 0.0   | VEE   | +2.0  | 0.0   | VEE   | +2.0  | 0.0   | V    |

| I <sub>IH</sub> | Input HIGH Current                                                                |                 |       | 150   |       |       | 150   |       |       | 150   | μΑ   |

| IIL             | Input LOW Current                                                                 | 0.5             |       |       | 0.5   |       |       | 0.5   |       |       | μΑ   |

#### Table 8. 10EP DC CHARACTERISTICS, NECL V<sub>CC</sub> = 0 V, V<sub>EE</sub> = -5.5 V to -3.0 V (Note 10)

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

board with maintained transverse airriow greater than 500 ltpm.

10. Input and output parameters vary 1:1 with V<sub>CC</sub>.

11. Required 500 ltpm air flow when using –5 V power supply. For (V<sub>CC</sub> – V<sub>EE</sub>) >3.3 V, 5 Ω to 10 Ω in line with V<sub>EE</sub> required for maximum thermal protection at elevated temperatures. Recommend V<sub>CC</sub>–V<sub>EE</sub> operation at ≤ 3.3 V.

12. All loading with 50 Ω to V<sub>CC</sub> – 2.0 V.

13. V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, V<sub>IHCMR</sub> max varies 1:1 with V<sub>CC</sub>. The V<sub>IHCMR</sub> range is referenced to the most positive side of the differential input signal.

| Table 9. AC CHARACTERISTICS | $V_{EE} = -3.0 \text{ V to } -5.5 \text{ V; } V_{CC}$ | $v_{c} = 0 \text{ V or } V_{CC} = 3.0 \text{ V to } 5.5 \text{ V}; \text{ V}_{EE} = 0 \text{ V (Note 14)}$ |

|-----------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|-----------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| –40°C 25°C 85°C |

|-----------------|

|-----------------|

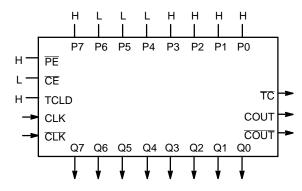

### **APPLICATIONS INFORMATION**

### **Cascading Multiple EP016 Devices**

For applications which call for larger than 8-bit counters multiple EP016s can be tied together to achieve very wide bit width counters. The active low terminal count ( $\overline{TC}$ ) output and count enable input ( $\overline{CE}$ ) greatly facilitate the cascading of EP016 devices. Two EP016s can be cascaded without the need for external gating, however for counters wider than 16 bits external OR gates are necessary for cascade implementations.

Figure 3 below pictorially illustrates the cascading of 4 EP016s to build a 32–bit high frequency counter. Note the EP01 gates used to OR the terminal count outputs of the lower order EP016s to control the counting operation of the higher order bits. When the terminal count of the preceding device (or devices) goes low (the counter reaches an all 1s state)

#### **APPLICATIONS INFORMATION (CONTINUED)**

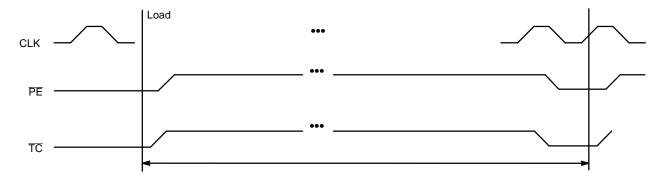

Figure 4. Mod 2 to 256 Programmable Divider

To determine what value to load into the device to accomplish the desired division, the designer simply subtracts the binary equivalent of the desired divide ratio from the binary value for 256. As an example for a divide ratio of 113:

$Pn's = 256 - 113 = 8F_{16} = 1000 \ 1111$  where:

PO = LSB and P7 = MSB

Forcing this input condition as per the setup in Figure 4 will result in the waveforms of Figure 5. Note that the  $\overline{TC}$  output is used as the divide output and the pulse duration is equal to a full clock period. For even divide ratios, twice the desired divide ratio can be loaded into the EP016 and the  $\overline{TC}$  output can feed the clock input of a toggle flip flop to create a signal divided as desired with a 50% duty cycle.

| Divide |    |    | Pr | eset D | ata Inp | outs |    |    |

|--------|----|----|----|--------|---------|------|----|----|

| Ratio  | P7 | P6 | P5 | P4     | P3      | P2   | P1 | P0 |

| 2      | Н  | Н  | Н  | Н      | Н       | Н    | Н  | L  |

| 3      | н  | н  | н  | н      | н       | н    | L  | Н  |

| 4      | н  | н  | н  | н      | н       | н    | L  | L  |

| 5      | н  | н  | н  | н      | н       | L    | н  | н  |

| w      | w  | •  | •  | •      | •       | •    | •  | •  |

| w      | •  | •  | •  | •      | •       | •    | •  | •  |

| 112    | н  | L  | L  | н      | L       | L    | L  | L  |

| 113    | н  | L  | L  | L      | н       | н    | н  | н  |

| 114    | н  | L  | L  | L      | н       | н    | н  | L  |

| •      | •  | •  | •  | •      | •       | •    | •  | •  |

| •      | •  | •  | •  | •      | •       | •    | •  | •  |

| 254    | L  | L  | L  | L      | L       | L    | н  | L  |

| 255    | L  | L  | L  | L      | L       | L    | L  | н  |

| 256    | L  | L  | L  | L      | L       | L    | L  | L  |

A single EP016 can be used to divide by any ratio from 2 to 256 inclusive. If divide ratios of greater than 256 are needed multiple EP016s can be cascaded in a manner similar to that already discussed. When EP016s are cascaded to build larger dividers the TCLD pin will no longer provide a means for loading on terminal count. Because one does not want to reload the counters until all of the devices in the chain have reached terminal count, external gating of the  $\overline{TC}$  pins must be used for multiple EP016 divider chains.

Table 10. PRESET VALUES FOR VARIOUS DIVIDE RATIOS

#### **ORDERING INFORMATION**

| Device         | Package              | Shipping <sup>†</sup> |

|----------------|----------------------|-----------------------|

| MC10EP016FAG   | LQFP-32<br>(Pb-Free) | 250 Units / Tray      |

| MC10EP016FAR2G | LQFP–32<br>(Pb–Free) | 2,000 / Tape & Reel   |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

#### **Resource Reference of Application Notes**

| AN1405/D  | - | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | _ | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | _ | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | _ | Metastability and the ECLinPS Family        |

| AN1568/D  | _ | Interfacing Between LVDS and ECL            |

| AN1672/D  | _ | The ECL Translator Guide                    |

| AND8001/D | _ | Odd Number Counters Design                  |

| AND8002/D | _ | Marking and Date Codes                      |

| AND8020/D | _ | Termination of ECL Logic Devices            |

| AND8066/D | _ | Interfacing with ECLinPS                    |

| AND8090/D | _ | AC Characteristics of ECL Devices           |

ECLinPS is a trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

LQFP-32, 7x7 CASE 561AB ISSUE O

DATE 19 JUN 200

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi