# L W- CMOS O T L

With 5 V–Tolerant Inputs and Outputs (3–State, Non–Inverting)

## MC74LC 373

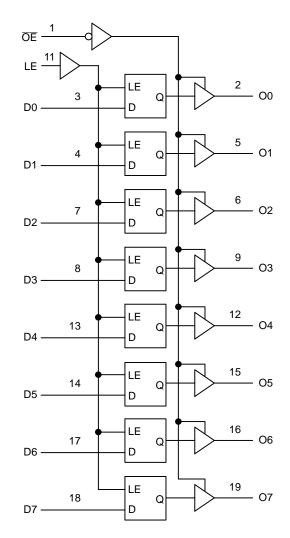

The MC74LCX373 is a high performance, non-inverting octal transparent latch operating from a 2.3 to 3.6 V supply. High impedance TTL compatible inputs significantly reduce current loading to input drivers while TTL compatible outputs offer improved switching noise performance. A V<sub>I</sub> specification of 5.5 V allows MC74LCX373 inputs to be safely driven from 5 V devices.

The MC74LCX373 contains 8 D-type latches with 3-state outputs. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition, the latches are transparent, i.e., a latch output will change state each time its D input changes. When

LE is LOW, the latches store the information th9(sign7(laith eresch)]Dn input-.0087 959 Tw81nput driversgnie p(la1gh)ap(la1gh)setupts D is

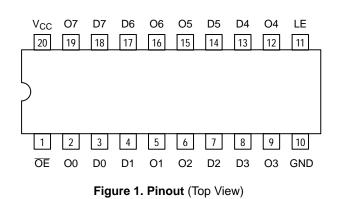

**PIN NAMES**

| PINS  | FUNCTION              |

|-------|-----------------------|

| OE    | Output Enable Input   |

| LE    | Latch Enable Input    |

| D0-D7 | Data Inputs           |

| 00–07 | 3–State Latch Outputs |

| TRUTH TABLE |        |        |         |                                                |  |  |

|-------------|--------|--------|---------|------------------------------------------------|--|--|

|             | INPUTS |        | OUTPUTS |                                                |  |  |

| OE          | LE     | Dn     | On      | OPERATING MODE                                 |  |  |

| L           | H<br>H | H<br>L | H<br>L  | Transparent (Latch Disabled); Read Latch       |  |  |

| L<br>L      | L      | h<br>I | H<br>L  | Latched (Latch Enabled) Read Latch             |  |  |

| L           | L      | Х      | NC      | Hold; Read Latch                               |  |  |

| Н           | L      | Х      | Z       | Hold; Disabled Outputs                         |  |  |

| H<br>H      | H<br>H | H<br>L | Z<br>Z  | Transparent (Latch Disabled); Disabled Outputs |  |  |

| H<br>H      | L      | h<br>I | Z<br>Z  | Latched (Latch Enabled); Disabled Outputs      |  |  |

Н High Voltage Level =

High Voltage Level One Setup Time Prior to the Latch Enable High-to-Low Transition h =

Low Voltage Level L =

= Low Voltage Level One Setup Time Prior to the Latch Enable High-to-Low Transition L

NC = No Change, State Prior to the Latch Enable High-to-Low Transition

Х = High or Low Voltage Level or Transitions are Acceptable

Ζ = High Impedance State

For I<sub>CC</sub> Reasons DO NOT FLOAT Inputs

#### DC ELECTRICAL CHARACTERISTICS

|                 |                                   |                                                            | T, |

|-----------------|-----------------------------------|------------------------------------------------------------|----|

| Symbol          | Characteristic                    | Condition                                                  |    |

| V <sub>IH</sub> | HIGH Level Input Voltage (Note 2) | $2.3~\text{V} \leq \text{V}_{\text{CC}} \leq 2.7~\text{V}$ |    |

|                 |                                   | $2.7~\text{V} \leq \text{V}_{\text{CC}} \leq 3.6~\text{V}$ |    |

| VIL             | LOW Level Input Voltage (Note 2)  | $2.3 V \le V_{CC} V$                                       | •  |

|                 |                                   |                                                            |    |

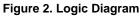

#### **DYNAMIC SWITCHING CHARACTERISTICS**

|                  |                                     |                                                                                                                                                                                                                                                                                                       | T <sub>A</sub> = +25°C |            |        |                        |

|------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|--------|------------------------|

| Symbol           | Characteristic                      | Condition                                                                                                                                                                                                                                                                                             | Min                    | Тур        | Max    | Units                  |

| V <sub>OLP</sub> | Dynamic LOW Peak Voltage (Note 4)   | $ \begin{array}{l} {\sf V}_{CC} = 3.3 \; {\sf V}, \; {\sf C}_{L} = 50 \; {\sf pF}, \; {\sf V}_{IH} = 3.3 \; {\sf V}, \; {\sf V}_{IL} = 0 \; {\sf V} \\ {\sf V}_{CC} = 2.5 \; {\sf V}, \; {\sf C}_{L} = 30 \; {\sf pF}, \; {\sf V}_{IH} = 2.5 \; {\sf V}, \; {\sf V}_{IL} = 0 \; {\sf V} \end{array} $ |                        | 0.8<br>0.6 |        | V                      |

| V <sub>OLV</sub> | Dynamic LOW Valley Voltage (Note 4) | $V_{CC}$ = 3.3 V, $C_L$ = 50 pF, $V_{IH}$ = 3.3 V, $V_{IL}$ = 0 V $V_{CC}$ = 2.5 V, $C_L$ = 30 pF, $V_{IH}$ = 2.5 V, $V_{IL}$ = 0 V V                                                                                                                                                                 | -64.271                | .680–33    | 24.888 | ref426.18 <sup>-</sup> |

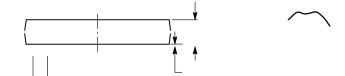

TSSOP-20 WB CASE 948E ISSUE D

DATE 17 FEB 2016

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi