# With 5V-Tolerant Inputs

# MC74L 373

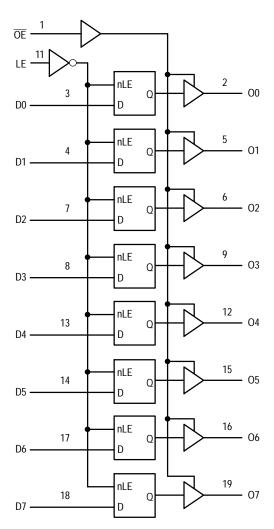

The MC74LVX373 is an advanced high speed CMOS octal latch with 3 state outputs. The inputs tolerate voltages up to 7.0 V, allowing the interface of 5.0 V systems to 3.0 V systems.

This 8 bit D type latch is controlled by a latch enable input and an output enable input. When the output enable input is high, the eight outputs are in a high impedance state.

#### **Features**

High Speed:  $t_{PD} = 5.8 \text{ ns}$  (Typ) at  $V_{CC} = 3.3 \text{ V}$

Low Power Dissipation:  $I_{CC} = 4 \mu A$  (Max) at  $T_A = 25 C$

Power Down Protection Provided on Inputs

**Balanced Propagation Delays**

Low Noise:  $V_{OLP} = 0.8 \text{ V (Max)}$

Pin and Function Compatible with Other Standard Logic Families

Latchup Performance Exceeds 300 mA

**ESD Performance:**

Human Body Model > 2000 V; Machine Model > 200 V

These Devices are Pb Free and are RoHS Compliant

#### **PIN NAMES**

| Pins  | Function              |

|-------|-----------------------|

| OE    | Output Enable Input   |

| LE    | Latch Enable Input    |

| D0-D7 | Data Inputs           |

| O0-O7 | 3–State Latch Outputs |

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

Figure 1. Logic Diagram

| INPUTS |        |        | OUTPUTS |                                                |

|--------|--------|--------|---------|------------------------------------------------|

| ŌĒ     | LE     | Dn     | On      | OPERATING MODE                                 |

| L<br>L | H      | H L    | ΙJ      | Transparent (Latch Disabled); Read Latch       |

| L<br>L | L      | h<br>I | H       | Latched (Latch Enabled) Read Latch             |

| L      | L      | Х      | NC      | Hold; Read Latch                               |

| Н      | L      | Х      | Z       | Hold; Disabled Outputs                         |

| H<br>H | H      | H L    | Z<br>Z  | Transparent (Latch Disabled); Disabled Outputs |

| H<br>H | L<br>L | h<br>I | Z<br>Z  | Latched (Latch Enabled); Disabled Outputs      |

## **MAXIMUM RATINGS**

| Symbol           | Parameter                                       | Value                        | Unit |

|------------------|-------------------------------------------------|------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage                               | -0.5 to +7.0                 | V    |

| V <sub>in</sub>  | DC Input Voltage                                | -0.5 to +7.0                 | V    |

| V <sub>out</sub> | DC Output Voltage                               | -0.5 to V <sub>CC</sub> +0.5 | V    |

| I <sub>IK</sub>  | Input Diode Current                             | -20                          | mA   |

| I <sub>OK</sub>  | Output Diode Current                            | 20                           | mA   |

| l <sub>out</sub> | DC Output Current, per Pin                      | 25                           | mA   |

| I <sub>CC</sub>  | DC Supply Current, V <sub>CC</sub> and GND Pins | 75                           | mA   |

| Pn               | •                                               | •                            | •    |

## AC ELECTRICAL CHARACTERISTICS (Input $t_f = t_f = 3.0 \text{ns}$ )

|        |           |                 | T <sub>A</sub> = 25 C | T <sub>A</sub> = -40 to 85 C |      | Ī |

|--------|-----------|-----------------|-----------------------|------------------------------|------|---|

| Symbol | Parameter | Test Conditions |                       |                              | Unit |   |

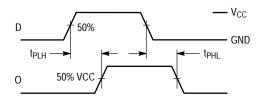

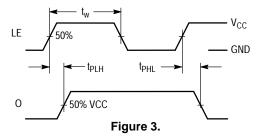

Figure 2.

## TSSOP-20 WB CASE 948E ISSUE D

DATE 17 FEB 2016