# 3-to-8 Line Decoder MC74VHC138

The MC74VHC138 is an advanced high speed CMOS 3 to 8 decoder fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power dissipation.

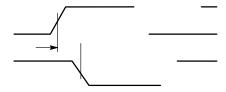

When the device is enabled, three Binary Select inputs (A0 A2) determine which one of the outputs  $(\overline{Y0} \ \overline{Y7})$  will go Low. When enable input E3 is held Low or either  $\overline{E2}$  or  $\overline{E1}$  is held High, decoding function is inhibited and all outputs go high. E3,  $\overline{E2}$ , and  $\overline{E1}$  inputs are provided to ease cascade connection and for use as an address decoder for memory systems.

The internal circuit is composed of three stages, including a buffer output which provides high noise immunity and stable output. The inputs tolerate voltages up to 7V, allowing the interface of 5V systems to 3V systems.

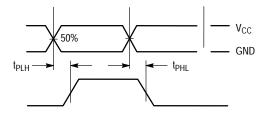

- High Speed:  $t_{PD} = 5.7 \text{ns}$  (Typ) at  $V_{CC} = 5 \text{ V}$

- Low Power Dissipation:  $I_{CC} = 4 \mu A \text{ (Max)}$  at  $T_A = 25 \text{°C}$

- High Noise Immunity:  $V_{NIH} = V_{NIL} = 28\% V_{CC}$

- Power Down Protection Provided on Inputs

- Balanced Propagation Delays

- Designed for 2 V to 5.5 V Operating Range

- Low Noise:  $V_{OLP} = 0.8 \text{ V (Max)}$

•

#### **MAXIMUM RATINGS\***

| Symbol           | Parameter           | Value                          | Unit |

|------------------|---------------------|--------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage   | - 0.5 to + 7.0                 | V    |

| V <sub>in</sub>  | DC Input Voltage    | - 0.5 to + 7.0                 | V    |

| V <sub>out</sub> | DC Output Voltage   | - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| I <sub>IK</sub>  | Input Diode Current | - 20                           |      |

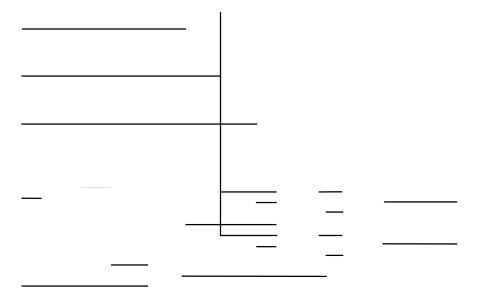

Figure 2.

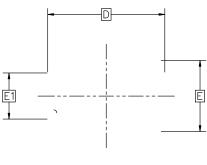

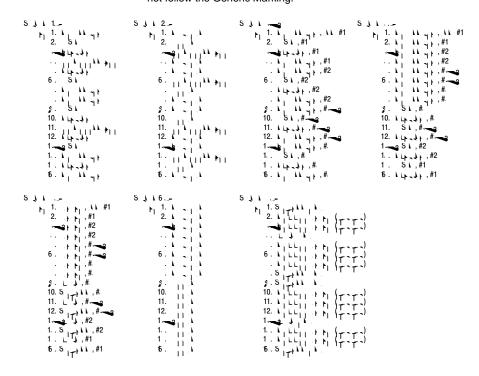

#### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

**DATE 18 OCT 2024**

- 3. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.1

nm TOTAL IN EXCESS OF THE

b DIMENSION AT MAXIMUM MATE

TOP VIEW

**DATE 18 OCT 2024**

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

A = Assembly Location

\*This information is generic. Please refer to device data sheet for actual part marking. Pb Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42566B                         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | PTION: SOIC-16 9.90X3.90X1.37 1.27P |                                                                                                                                                                                     | PAGE 2 OF 2 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### TSSOP-16 WB CASE 948F ISSUE B

**DATE 19 OCT 2006**

SCALE 2:1