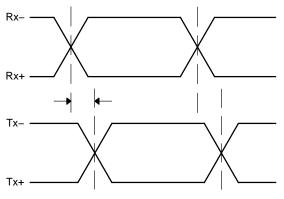

Figure 1. Logic Diagram

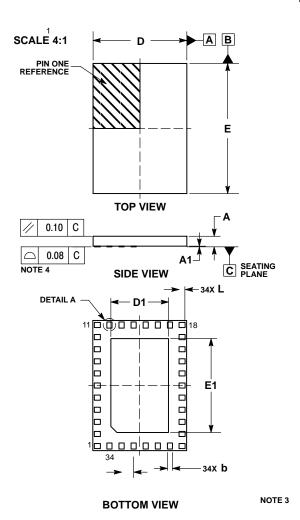

Figure 2. X2QFN34 Package

### Table 1. PIN DESCRIPTION

| Pin Number | Pin Name | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 14         | CTRL_D0  | LVCMOS<br>INPUT | Pin D0 for control of Equalization settings on Channel D having internal 100 k $\Omega$ pull up and 200 pull down. 4 state input: HIGH "H" where pin is connected to V <sub>CC</sub> , LOW "L" where pin is connect to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resister k $\Omega$ connected from pin to Ground. Refer Table 2 for the different settings.                 |  |  |  |  |

| 15         | CTRL_D1  | LVCMOS<br>INPUT | Pin D1 for control of Flat Gain settings on Channel D having internal 100 k $\Omega$ pull up and 200 k $\Omega$ p down. 4 state input: HIGH "H" where pin is connected to V <sub>CC</sub> , LOW "L" where pin is connected to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resistor 68 k $\Omega$ connected from pin to Ground. Refer Table 2 for the different settings.       |  |  |  |  |

| 16, 33     | GND      | GROUND          | Reference Ground. GND pins must be externally connected to ground to guarantee proper opera-<br>tion.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 18         | D_RX+    | DIFF            | Channel D Differential input for 5 / 10 Gbps USB signals. Must be externally AC-coupled.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 19         | D_RX-    | INPUT           |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 20         | C_TX+    | DIFF            | Channel C Differential output for 5 / 10 Gbps USB signals. Must be externally AC-coupled.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 21         | C_TX-    | OUTPUT          |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 23         | CTRL_B0  | LVCMOS<br>INPUT | Pin B0 for control of Flat Gain settings on Channel B having internal 100 k $\Omega$ pull up and 200 k $\Omega$ pull down. 4 state input: HIGH "H" where pin is connected to V <sub>CC</sub> , LOW "L" where pin is connected to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resistor 68 k $\Omega$ connected from pin to Ground. Refer Table 2 for the different settings.    |  |  |  |  |

| 24         | CTRL_B1  | LVCMOS<br>INPUT | Pin B1 for control of Equalization settings on Channel B having internal 100 k $\Omega$ pull up and 200 k $\Omega$ pull down. 4 state input: HIGH "H" where pin is connected to V <sub>CC</sub> , LOW "L" where pin is connected to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resistor 68 k $\Omega$ connected from pin to Ground. Refer Table 2 for the different settings. |  |  |  |  |

| 25         | B_RX+    | DIFF            | Channel B Differential input for 5 / 10 Gbps USB signals. Must be externally AC-coupled.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 26         | B_RX-    | INPUT           |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 27         | A_TX+    | DIFF            | Channel A Differential output for 5 / 10 Gbps USB signals. Must be externally AC-coupled.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 28         | A_TX-    | OUTPUT          |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 31         | CTRL_A0  | LVCMOS<br>INPUT | Pin A0 for control of Equalization settings on Channel A having internal 100 k $\Omega$ pull up and 200 k $\Omega$ pull down. 4 state input: HIGH "H" where pin is connected to V <sub>CC</sub> , LOW "L" where pin is connected to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resistor 68 k $\Omega$ connected from pin to Ground. Refer Table 2 for the different settings. |  |  |  |  |

| 32         | CTRL_A1  | LVCMOS<br>INPUT | Pin A1 for control of Flat Gain settings on Channel A having internal 100 k $\Omega$ pull up and 200 k $\Omega$ down. 4 state input: HIGH "H" where pin is connected to V <sub>CC</sub> , LOW "L" where pin is connected to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resistor (k $\Omega$ connected from pin to Ground. Refer Table 2 for the different settings.           |  |  |  |  |

| EP         | GND      | GROUND          | Exposed pad (EP). EP on the package bottom is thermally connected to the die for improved heat transfer out of the package. The pad is not electrically connected to the die, but is recommended to be soldered to GND on the PC Board.                                                                                                                                                                                   |  |  |  |  |

### **DEVICE CONFIGURATION**

|              | PORT A/B         |                  |                  |                  | PORT C/D         |                  |                  |                  |            |            |

|--------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------|------------|

|              | Channel A        |                  | Channel B        |                  | Channel C        |                  | Channel D        |                  |            |            |

| Settings     | CTRL_A1<br>(FGA) | CTRL_A0<br>(EQA) | CTRL_B1<br>(EQB) | CTRL_B0<br>(FGB) | CTRL_C1<br>(EQC) | CTRL_C0<br>(FGC) | CTRL_D1<br>(FGD) | CTRL_D0<br>(EQD) | EQ<br>(dB) | FG<br>(dB) |

| 1            | L                | L                | L                | L                | L                | L                | L                | L                | 10.9       | -3         |

| 2            | L                | R                | R                | L                | R                | L                | L                | R                | 6.7        | -3         |

| 3            | L                | F                | F                | L                | F                | L                | L                | F                | 8.9        | -3         |

| 4            | L                | Н                | Н                | L                | Н                | L                | L                | Н                | 13.1       | -3         |

| 5            | R                | L                | L                | R                | L                | R                | R                | L                | 10.9       | -1.5       |

| 6            | R                | R                | R                | R                | R                | R                | R                | R                | 6.7        | -1.5       |

| 7            | R                | F                | F                | R                | F                | R                | R                | F                | 8.9        | -1.5       |

| 8            | R                | Н                | Н                | R                | Н                | R                | R                | Н                | 13.1       | -1.5       |

| 9            | F                | L                | L                | F                | L                | F                | F                | L                | 10.9       | 0          |

| 10           | F                | R                | R                | F                | R                | F                | F                | R                | 6.7        | 0          |

| 11 (Default) | F                | F                | F                | F                | F                | F                | F                | F                | 8.9        | 0          |

| 12           | F                | Н                | Н                | F                | Н                | F                | F                | Н                | 13.1       | 0          |

| 13           | Н                | L                | L                | Н                | L                | Н                | Н                | L                | 10.9       | 2          |

| 14           | Н                | R                | R                | Н                | R                | Н                | Н                | R                | 6.7        | 2          |

| 15           | Н                | F                | F                | Н                | F                | Н                | Н                | F                | 8.9        | 2          |

| 16           | Н                | Н                | Н                | Н                | Н                | Н                | Н                | Н                | 13.1       | 2          |

### Table 2. CONTROL PIN EFFECTS (Typical Values)

NOTE: EQ and FG can be set by adjusting the voltage to the control pins. There are 4 specific levels – HIGH "H" where pin is connected to V<sub>CC</sub>, LOW "L" where pin is connected to Ground, FLOAT "F" where the pin is left floating (open) and Rext "R" where an external resistor 68 kΩ connected from pin to Ground. Please refer Table 7 for voltage levels.

#### Table 3. ATTRIBUTES

| Parameter                                                      |                                          |                      |

|----------------------------------------------------------------|------------------------------------------|----------------------|

| ESD Protection                                                 | Human Body Model<br>Charged Device Model | ≤ 2 kV<br>≤ 1.5 kV   |

| Moisture Sensitivity, Indefinite Time Out of Dry pack (Note 1) |                                          | Level 1              |

| Flammability Rating                                            | Oxygen Index: 28 to 34                   | UL 94 V–O @ 0.125 in |

| Transistor Count                                               |                                          | 81,034               |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test        | L                                        |                      |

1. For additional information, see Application Note AND8003/D.

#### Table 4. ABSOLUTE MAXIMUM RATINGS Over operating free-air temperature range (unless otherwise noted)

| Parameter                                                                | Description      | Min  | Max                   | Unit |

|--------------------------------------------------------------------------|------------------|------|-----------------------|------|

| Supply Voltage (Note 2)                                                  | V <sub>CC</sub>  | -0.5 | 4.6                   | V    |

| Voltage range at any input or output terminal                            | Differential I/O | -0.5 | V <sub>CC</sub> + 0.5 | V    |

|                                                                          | LVCMOS inputs    | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Storage Temperature Range, T <sub>SG</sub>                               |                  | -65  | 150                   | °C   |

| Maximum Junction Temperature, T <sub>J</sub>                             |                  |      | 125                   | °C   |

| Operating Ambient Temperature Range, T <sub>A</sub>                      |                  | -40  | 85                    | °C   |

| Junction–to–Ambient Thermal Resistance @ 500 lfm, $\theta_{JA}$ (Note 3) |                  |      | 34                    | °C/W |

| Wave Solder, Pb-Free, T <sub>SOL</sub>                                   |                  |      | 265                   | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the

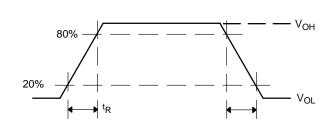

## PARAMETER MEASUREMENT DIAGRAMS

Figure 3. Propagation Delay

Figure 4. Output Rise and Fall Times

### Table 11. DESIGN REQUIREMENTS

**Design Parameter**

Value

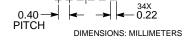

X2QFN34 3.1x4.3, 0.4P CASE 722AL ISSUE O

> ٧ 4

### DATE 02 MAY 2017

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS. 3. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25 MM FROM THE TERMINAL TIP. 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE PLATED TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | NOM  |  |

| Α   | 0.30        | 0.35 |  |

| A1  |             |      |  |

| b   | 0.12        | 0.17 |  |

| D   |             |      |  |

| D1  | 1.80        | 1.90 |  |

| Е   |             |      |  |

| E1  | 3.00        | 3.10 |  |

| е   | 0.40 BSC    |      |  |

|     |             |      |  |

|     |             |      |  |

L 0.20 0.25

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi