# onse 1

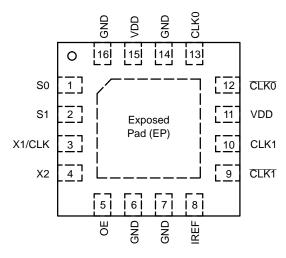

Figure 2. Pin Configuration (Top View)

## **Table 1. PIN DESCRIPTION**

| Pin             | Symbol           | I/O          | Description                                                                                                                                                                                   |  |  |

|-----------------|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1               | S0               | Input        | LVTTL/LVCMOS frequency select input 0. Internal pullup resistor to V <sub>DD</sub> . See output select Table 2 for details.                                                                   |  |  |

| 2               | S1               | Input        | LVTTL/LVCMOS frequency select input 1. Internal pullup resistor to $V_{DD}$ . See output select Table 2 for details.                                                                          |  |  |

| 11, 15          | $V_{DD}$         | Power Supply | Positive supply voltage pins are connected to +3.3 V supply voltage.                                                                                                                          |  |  |

| 3               | X1/CLK           | Input        | Crystal or Clock input. Connect to 25 MHz crystal source or single-ended clock.                                                                                                               |  |  |

| 4               | X2               | Input        | Crystal input. Connect to a 25 MHz crystal or leave unconnected for clock input.                                                                                                              |  |  |

| 5               | OE               | Input        | When floating, the internal pull-up resistor to V <sub>DD</sub> will make OE logic High enabling the Output When connected to GND, logic Low, the outputs are disabled and will go to high-Z. |  |  |

| 6, 7,<br>14, 16 | GND              | Power Supply | Ground 0 V. These pins provide GND return path for the devices.                                                                                                                               |  |  |

| 8               | I <sub>REF</sub> | Output       | Output current reference pin. Precision resistor (typ. 475 $\Omega$ ) is 28 Tc(Z.) 0 TD0et outputs arrent21.                                                                                  |  |  |

**Table 3. ATTRIBUTES**

| Charact                                                | Value                  |                      |  |  |

|--------------------------------------------------------|------------------------|----------------------|--|--|

| ESD Protection Human Body Model                        |                        | > 2 kV               |  |  |

| RPU – OE, S0 and S1 Pull-up Re                         | 100 kΩ                 |                      |  |  |

| Moisture Sensitivity, Indefinite Tin                   | Level 1                |                      |  |  |

| Flammability Rating                                    | Oxygen Index: 28 to 34 | UL 94 V-0 @ 0.125 in |  |  |

| Transistor Count                                       | 7623                   |                      |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test |                        |                      |  |  |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

Table 4. MAXIMUM RATINGS (Note 2)

| Symbol              | Parameter                                | Condition 1        | Condition 2              | Rating                           | Unit         |

|---------------------|------------------------------------------|--------------------|--------------------------|----------------------------------|--------------|

| V <sub>DD</sub>     | Positive Power Supply                    | GND = 0 V          |                          | 4.6                              | V            |

| VI                  | Input Voltage (V <sub>IN</sub> )         | GND = 0 V          | $GND \leq V_I \leq V_DD$ | -0.5 V to V <sub>DD</sub> +0.5 V | V            |

| T <sub>A</sub>      | Operating Temperature Range              |                    |                          | -40 to +105                      | °C           |

| T <sub>stg</sub>    | Storage Temperature Range                |                    |                          | -65 to +150                      | °C           |

| T <sub>J(max)</sub> | Maximum Junction Temperature             |                    |                          | +125                             | °C           |

| $\theta_{\sf JA}$   | Thermal Resistance (Junction-to-Ambient) | 0 lfpm<br>500 lfpm | QFN-16<br>QFN-16         | 42<br>35                         | °C/W<br>°C/W |

| θ <sub>JC</sub>     | Thermal Resistance (Junction-to-Case)    | (Note 3)           | QFN-16                   | 4                                | °C/W         |

| T <sub>sol</sub>    | Wave Solder                              |                    |                          | 265                              | °C           |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Table 5. DC CHARACTERISTICS ( $V_{DD} = 3.3 \text{ V} \pm 10\%$ , GND = 0 V,  $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , Note 4)

| Symbol             | Characteristic                                            | Min       | Тур | Max                   | Unit |

|--------------------|-----------------------------------------------------------|-----------|-----|-----------------------|------|

| VDD                | Power Supply Voltage                                      | 2.97      | 3.3 | 3.63                  | V    |

| I <sub>DD</sub>    | Power Supply Current                                      |           | 120 | 135                   | mA   |

| I <sub>DDOE</sub>  | Power Supply Current when OE is Set Low                   |           |     | 65                    | mA   |

| V <sub>IH</sub>    | Input HIGH Voltage (X/CLK, S0, S1, and OE)                | 2000      |     | V <sub>DD</sub> + 300 | mV   |

| $V_{IL}$           | Input LOW Voltage (X/CLK, S0, S1, and OE)                 | GND – 300 |     | 800                   | mV   |

| V <sub>OH</sub>    | Output HIGH Voltage for HCSL Output (See Figure 5)        | 660       | 700 | 850                   | mV   |

| V <sub>OL</sub>    | Output LOW Voltage for HCSL Output (See Figure 5)         | -150      | 0   | 150                   | mV   |

| V <sub>cross</sub> | Crossing Voltage Magnitude (Absolute) for HCSL Output     | 250       |     | 550                   | mV   |

| $\Delta V_{cross}$ | Change in Magnitude of V <sub>cross</sub> for HCSL Output |           |     | 150                   | mV   |

NOTE: Device will meet the specifications after thermal equilibrium has been established BT8 08e 205.66.753 the specifr516.189 190.715 TT4 9tc/r2 wills break

<sup>2.</sup> Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and not valid simultaneously. If stress limits are exceeded device functional operation is not implied, damage may occur and reliability may be affected.

<sup>3.</sup> JEDEC standard multilayer board – 2S2P (2 signal, 2 power).

# Table 7. ELECTRICAL CHARACTERISTICS – PHASE JITTER PARAMETERS

| Symbol | Parameter |

|--------|-----------|

|--------|-----------|

NE www.

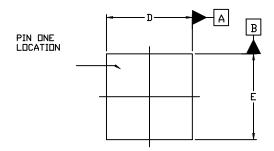

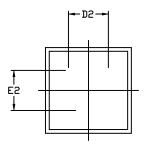

#### QFNW16 3x3, 0.5P CASE 484AN **ISSUE A**

**DATE 22 AUG 2018**

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN.        | N□M. |      |  |

| Α   | 0.80        | 0.90 |      |  |

| A1  |             |      |      |  |

| A၁  |             |      |      |  |

|     |             |      |      |  |

| Ø   |             |      | 0.30 |  |

| D   |             |      |      |  |

| D2  | 1.30        | 1.40 |      |  |

| E   |             | )    | 3.10 |  |

| E2  | 1.30        | 1.40 | 1.50 |  |

| е   | 0.50 BSC    |      |      |  |

|     |             |      |      |  |

| ·   |             |      |      |  |

|     |             |      |      |  |

## **GENERIC MARKING DIAGRAM\***

XXXXX XXXXX ALYW=

XXXXX = Specific Device Code

= Assembly Location Α

L = Wafer Lot = Year

= Work Week W

= Pb-Free Package (Note: Microdot may be in either location) \*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " ■", may or may not be present. Some products may not follow the Generic Marking.