# **12-Bit Low Power SAR ADC**

# NCD98010, NCD98011

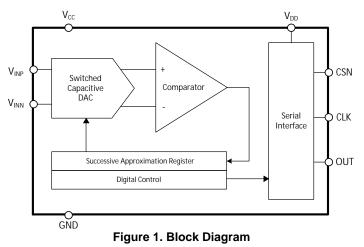

The NCD98010 (unsigned output) and the NCD98011 (signed output) ADC products provide an extremely low power solution for analog to digital conversion applications using a capacitor-based successive-approximation architecture. Optimized for low power and speed, the NCD98010/1 can achieve a sample rate of 2 MSPS while consuming less than 1 mW of power. The device also features a large input voltage range of 1.65 V to 3.3 V for various applications for both analog and digital supplies. The SPI-compatible interface provides a straight-forward data-acquisition method.

### Features

• Nanowatt Power Consumption

**ISe**

- Fully Differential Input

- 2-MSPS Throughput

- Small Package Size

- Pre-Calibrated

- SPI Interface

- These Devices are Pb-Free, Halogen Free/BFR Free and icesces a1T4 0 TD-0042 TG 0006 T e Weara

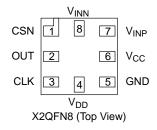

### **PIN CONFIGURATION**

### **ORDERING INFORMATION**

| ГD-0042 Тс 0006 Т е<br><b>Device</b> | Wearable F<br>Package | <sup>itn</sup> Ssipping <sup>†</sup> |  |

|--------------------------------------|-----------------------|--------------------------------------|--|

| NCD98010XMXTAG                       | X2QFN                 | 5000 / Tape &                        |  |

| NCD98011XMXTAG                       |                       | Reel                                 |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

### • Portable Medical Equipment

• Glucose Meters

### **PIN DESCRIPTION**

| X2QFN<br>Pin No. | Name             | Function                                |

|------------------|------------------|-----------------------------------------|

| 1                | CSN              | Chip select (active low)                |

| 2                | OUT              | Data Output (serialized)                |

| 3                | CLK              | Clock                                   |

| 4                | VDD              | Digital I/O supply voltage              |

| 5                | GND              | Common ground for all pins              |

| 6                | VCC              | Analog supply and ADC reference voltage |

| 7                | V <sub>INP</sub> | Analog input, positive signal           |

| 8                | V <sub>INN</sub> | Analog input, negative signal           |

### MAXIMUM RATINGS

Rating

Symbol

| Parameter                                                                 | Conditions                           | Symbol              | Min  | Тур |

|---------------------------------------------------------------------------|--------------------------------------|---------------------|------|-----|

| POWER SUPPLY REQUIREMENTS                                                 | 3                                    |                     |      |     |

| Analog Supply and ADC reference                                           |                                      | V <sub>CC</sub>     | 1.65 | 3   |

| Digital I/O Supply                                                        |                                      | V <sub>DD</sub>     | 1.65 | 3   |

|                                                                           | 2 MSPS for V <sub>CC</sub> = 3.6 V   |                     |      | 100 |

| Analog Supply Current                                                     | 1 MSPS for $V_{CC}$ = 3 V            |                     |      | 50  |

| Analog Supply Current                                                     | 100 kSPS for V <sub>CC</sub> = 3.6 V | - Ivcc              |      |     |

|                                                                           | 1 MSPS for $V_{CC}$ = 1.8 V          |                     |      |     |

|                                                                           | 2 MSPS for V <sub>CC</sub> = 3.6 V   |                     |      |     |

|                                                                           | 1 MSPS for $V_{CC}$ = 3 V            |                     |      | V   |

| Analog Power Dissipation                                                  | 100 kSPS for V <sub>CC</sub> = 3.6 V | Pvcc                |      |     |

|                                                                           | 1 MSPS for $V_{CC}$ = 1.8 V          |                     |      |     |

|                                                                           | 2 MSPS for $V_{DD}$ = 3.6 V          |                     |      |     |

| Digital Supply Current<br>Dependent on SDO loading<br>(tested with ~7 pF) | 1 MSPS for $V_{DD}$ = 3 V            |                     |      |     |

|                                                                           | 100 kSPS for $V_{DD}$ = 3.6 V        | - I <sub>VDD</sub>  |      |     |

|                                                                           | 1 MSPS for $V_{DD}$ = 1.8 V          |                     |      |     |

| Standby current (CSN high)<br>(Note 2)                                    | V <sub>CC</sub> = 3.6 V              | I <sub>STNDBY</sub> |      |     |

### **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C, V<sub>CC</sub> = 3 V, unless otherwise noted)

### **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C, V<sub>CC</sub> = 3 V, unless otherwise noted)

| Parameter                               | Conditions                                       | Symbol | Min | Тур | Max | Unit |

|-----------------------------------------|--------------------------------------------------|--------|-----|-----|-----|------|

| DYNAMIC CHARACTERISTICS                 |                                                  |        |     |     |     |      |

| Total–Harmonic Distortion               | $f_{IN} = 1 \text{ kHz } V_{CC} = 3.3 \text{ V}$ | THD    |     | -80 |     | dB   |

|                                         | $f_{IN} = 1 \text{ kHz } V_{CC} = 1.8 \text{ V}$ |        |     | -80 |     |      |

| Signal-to-Noise and Distortion (Note 4) | $f_{IN} = 1 \text{ kHz } V_{CC} = 3.3 \text{ V}$ | SINAD  | 68  | 69  |     | dB   |

|                                         | $f_{IN} = 1 \text{ kHz } V_{CC} = 1.8 \text{ V}$ |        |     | 62  |     |      |

| Spurious-Free Dynamic Range             | $f_{IN} = 1 \text{ kHz } V_{CC} = 3.3 \text{ V}$ | SFDR   | 69  | 80  |     | dB   |

| (Note 4)                                | $f_{IN} = 1 \text{ kHz } V_{CC} = 1.8 \text{ V}$ | SIDI   |     | 74  |     |      |

### DIGITAL INPUT/OUTPUT

| High-Level Input Voltage  |            | V <sub>IH</sub> | V <sub>DD</sub> *0.7    |                      | V |

|---------------------------|------------|-----------------|-------------------------|----------------------|---|

| Low–Level Input Voltage   |            | V <sub>IL</sub> |                         | V <sub>DD</sub> *0.3 | V |

| High-Level Output Voltage | 2 mA drive | V <sub>OH</sub> | V <sub>DD</sub> – 0.5 V |                      | V |

| Low–Level Output Voltage  | 2 mA drive | V <sub>OL</sub> |                         | GND+0.5              | V |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Standby current includes both digital and analog currents.

3. INL and DNL parameters were verified via bench testing and are not used for production screening.

4. SINAD and SFDR are tested at production and guaranteed by correlation to bench test results.

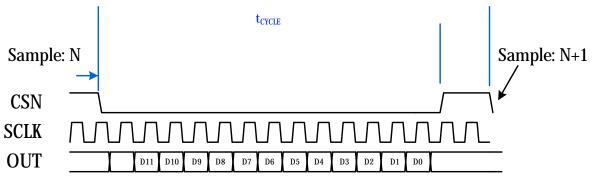

#### TIMING CHARACTERISTICS (T<sub>J</sub> = 25°C unless otherwise specified)

| Parameter             | Conditions | Symbol               | Min   | Тур | Max | Unit  |

|-----------------------|------------|----------------------|-------|-----|-----|-------|

| TIMING SPECIFICATIONS |            |                      |       |     |     |       |

| Throughput            |            | f <sub>THROUGH</sub> |       |     | 2   | MSPS  |

| Cycle Time            |            | fCYCLE               | 0.5   |     |     | μs    |

| Conversion Time       |            | f <sub>CONV</sub>    | 437.5 |     |     | ns    |

| Data Delay            |            |                      |       | 1   |     | cycle |

#### TIMING REQUIREMENTS

| Acquisition Time (CSN high)                      | t <sub>ACQ</sub>                  | 62.5  |       | ns  |

|--------------------------------------------------|-----------------------------------|-------|-------|-----|

| CLK Frequency                                    | fclk                              |       | 32    | MHz |

| CLK Period                                       | t <sub>CLK</sub>                  |       | 31.25 | ns  |

| CSN Falling to 1 <sup>st</sup> SCLK falling edge | <sup>t</sup> CSN_SCLK             | 15.75 |       | ns  |

| Last SCLK falling edge to CSN rising             | <sup>t</sup> SCLK_CSN             | 15.75 |       | ns  |

| Falling SCLK to SDO valid (Note 5) Assumed       | 10 pF Load t <sub>SDO_VALID</sub> |       | 30    | ns  |

5. When SCLK is running at higher frequencies, the t<sub>SDO\_VALID</sub> of 30 ns requires SDO to be sampled on the falling edge of SCLK at the end of the bit width just before SDO changes to the next output. This will ensure acquisition of the correct data. For example, location A shown below would be the best place to sample SDO for the acquisition of bit 9.

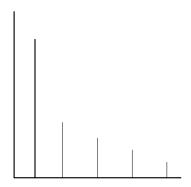

Figure 16. Spurious Free Dynamic Range in the Frequency Domain

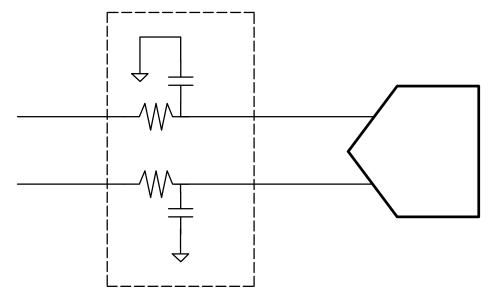

$1 \ \mu$ F. All decoupling capacitors must connect directly to a low impedance ground plane in order to be effective. Short traces or vias are required to minimize additional series inductance. Ceramic capacitors are recommended based on their low ESR and ESL. X7R ceramic capacitors are recommended for applications involving a wide temperature range.

### **Minimal Component Realization**

For applications where minimizing board space trumps ADC performance, the NCD98010/1 connection diagram can be reduced as shown in Figure 21 below. The removal of the input buffering may be an option depending on the nature of the differential analog input source. Removing the anti–aliasing filter would come at the expense of reduced ENOB due to the digitization of aliased signals.

Figure 21. Reduced Component Connection Diagram

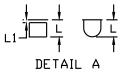

#### X2QFN8, 1.5x1.5, 0.5P CASE 722AM ISSUE O

DATE 20 JUL 2018

TOP VIEW

SIDE VIEW

COPLAN

DETAIL B

7x

BOTTOM VIEW

RΓ

#### GENERIC MARKING DIAGRAM\*

X = Specific Device Code M = Date Code

.

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " ■", may or may not be present. Some products may not follow the Generic Marking.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi