# ONSE Ní

## High Speed 3-Channel Digital Isolator NCID9301, NCID9311

#### Description

The NCID9301 and NCID9311 are galvanically isolated high speed 3 channel digital isolator with output enable. This device supports isolated communications thereby allowing digital signals to communicate between systems without conducting ground loops or hazardous voltages.

It utilizes **onsemi's** patented galvanic off chip capacitor isolation technology and optimized IC design to achieve high insulation and high noise immunity, characterized by high common mode rejection and power supply rejection specifications. The thick ceramic substrate yields capacitors with ~25 times the thickness of thin film on chip capacitors and coreless transformers. The result is a combination of the electrical performance benefits that digital isolators offer with the safety reliability of a >0.5 mm insulator barrier similar to what has historically been offered by optocouplers.

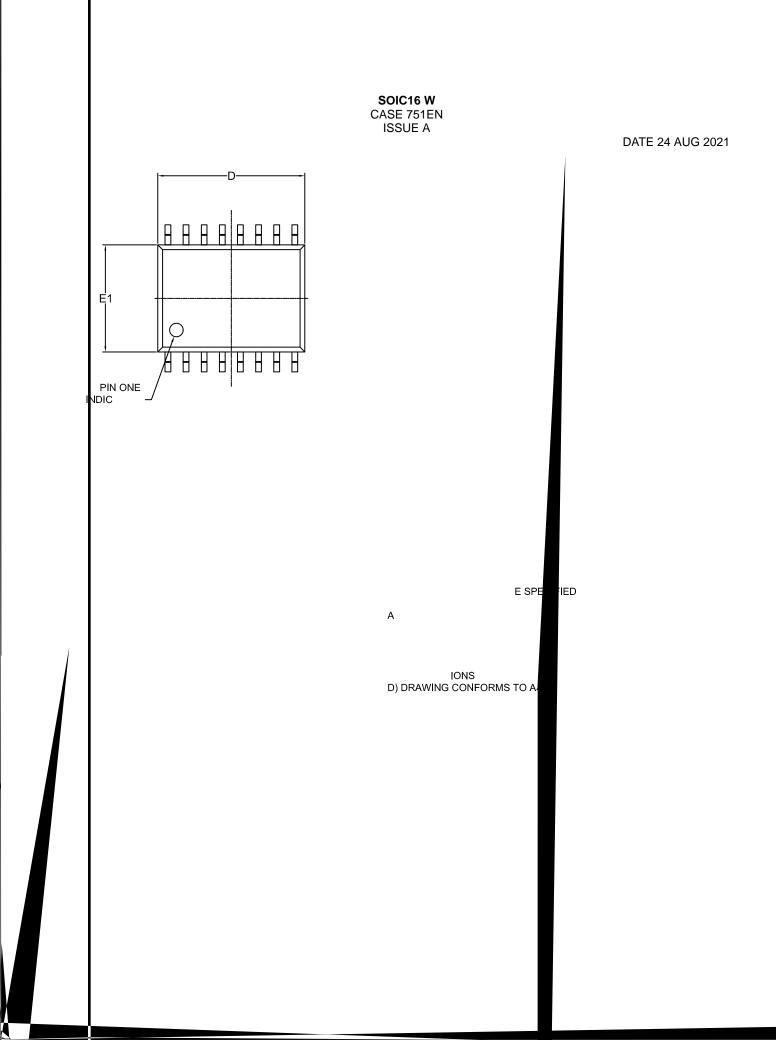

The device is housed in a 16

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 14 of this data sheet.

Microprocessor System Interface (SPI, I<sup>2</sup>C, etc.) Programmable Logic Control Isolated Data Acquisition System Voltage Level Translator

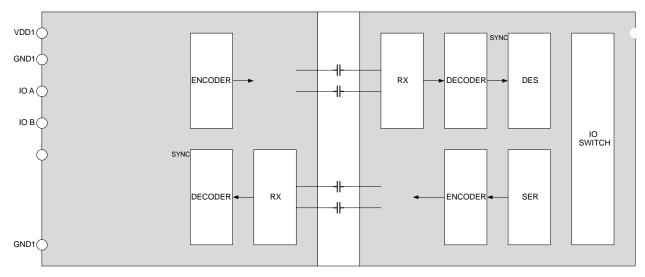

## **BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

## **PIN CONFIGURATION**

|                  | NCID9301 |                 |                  | NCID9311 |                  |

|------------------|----------|-----------------|------------------|----------|------------------|

| V <sub>DD1</sub> |          | $V_{DD2}$       | V <sub>DD1</sub> |          | V <sub>DD2</sub> |

| GND1             |          | GND2            | GND1             |          | GND2             |

| V <sub>INA</sub> |          | V <sub>OA</sub> | V <sub>INA</sub> |          | V <sub>OA</sub>  |

| V <sub>INB</sub> |          | V <sub>OB</sub> | V <sub>INB</sub> |          | V <sub>OB</sub>  |

| V <sub>INC</sub> |          | VIDIC           |                  |          |                  |

| NC               |          | NC              |                  |          |                  |

| NC               |          | EN2             |                  |          |                  |

| GND1             |          | GND2            |                  |          |                  |

### Figure 2. Pin and Channel Configuration

#### SPECIFICATIONS

#### TRUTH TABLE (Note 1)

| V <sub>INX</sub> | ENX  | V <sub>DDI</sub> | V <sub>DDO</sub> | V <sub>ox</sub> | Comment                                                          |

|------------------|------|------------------|------------------|-----------------|------------------------------------------------------------------|

| н                | H/NC | Power Up         | Power Up         | Н               | Normal Operation                                                 |

| L                | H/NC | Power Up         | Power Up         | L               | Normal Operation                                                 |

| NC               | H/NC | Power Up         | Power Up         | L               | Default low                                                      |

| Х                | L    | Power Up         | Power Up         | Hi–Z            |                                                                  |

| х                | H/NC | Power Down       | Power Up         | L               | Default low; $V_{OX}$ return to normal operation when $V_{DDIL}$ |

|    | Unit |

|----|------|

| 0  | С    |

| 25 | С    |

| 0  | С    |

| S  | С    |

|    | V    |

|    | V    |

|    | mA   |

|    | mW   |

eeded, device functionality

| Max                  | Unit |

|----------------------|------|

| +125                 | С    |

| 5.5                  | V    |

| V <sub>DDI</sub>     | V    |

| 0.1 V <sub>DDI</sub> | V    |

| -                    | V    |

| -                    | V    |

| Symbol                |                          |                                                                       |     |     |   |       |    |

|-----------------------|--------------------------|-----------------------------------------------------------------------|-----|-----|---|-------|----|

| V <sub>OH</sub>       |                          |                                                                       |     |     |   |       |    |

| V <sub>OL</sub>       |                          |                                                                       |     |     |   |       |    |

| V <sub>INT+</sub>     | -                        |                                                                       |     |     |   |       |    |

| V <sub>INT-</sub>     | -                        |                                                                       |     |     |   |       |    |

| V <sub>INT(HYS)</sub> |                          |                                                                       |     |     |   |       |    |

| I <sub>INH</sub>      | High Level Input Current | $V_{IH} = V_{DDI}$                                                    | -   | -   | 1 | μΑ    |    |

| I <sub>INL</sub>      | Low Level Input Current  | $V_{IL} = 0 V$                                                        | -1  | -   | - | μΑ    |    |

|                       | Common Mode Transient    | V <sub>I</sub> = V <sub>DDI</sub> or 0 V,<br>V <sub>CM</sub> = 1500 V | 100 | 150 | _ | kV/μs | 16 |

#### SWITCHING CHARACTERISTICS – NCID9311

Apply over all recommended conditions,  $T_A = -40$  C to +125 C unless otherwise specified. All typical values are measured at  $T_A = 25$  C.

| Symbol           | Parameter                                         | Ch   | Conditions                                    | Min | Тур | Max | Unit | Figure |

|------------------|---------------------------------------------------|------|-----------------------------------------------|-----|-----|-----|------|--------|

| t <sub>PHL</sub> | Propagation Delay to Logic<br>Low Output (Note 8) | А, В | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF | -   | 95  | 140 |      |        |

|                  |                                                   |      |                                               |     |     |     |      |        |

#### TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

V<sub>OH</sub> – High Level Output VI

I<sub>OH</sub> – High Level Output Current (mA)

Figure 11. High Level Output Voltage vs. Current

Figure 12. Low Level Output Voltage vs. Current

### **TEST CIRCUITS**

#### **APPLICATION INFORMATION**

#### Theory of Operation

NCID9301 and NCID9311 are 3 channel digital isolators. The chip to chip galvanic isolation are provided by a pair of off chip capacitors. Digital circuits are used for processing signals through the 0.5 mm thick isolation barrier.

Pins are trimmed internally as input or output at IO Switch. Each direction of communication between two isolated circuits are achieved by implementing a pair of Serializer/Deserializer and Manchester Encoder/Decoder functional blocks as shown in Figure 17. The Serializer circuit converts the parallel data from the IO Switch into a serial (one bit) stream and the Manchester Encoder converts this data stream into coded data making it more robust, efficient and accurate for transmission. After encoding, all inputs signals are coded as  $V_IT_X$  and transmitted across the isolation barrier via Transceiver.

The off chip ceramic capacitors that serve both as the isolation barrier and as the medium of transmission for signal switching using On Off keying (OOK) technique, illustrated in the transceiver block diagram in Figure 18

and Figure 19. At

Figure 20. 4–

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi