#

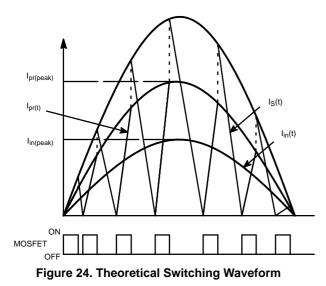

The NCL30000 is a switch mode power supply controller intended for low to medium power single stage power factor (PF) corrected LED Drivers. The device is designed to operate in critical conduction mode (CrM) and is suitable for flyback as well as buck topologies. Constant on time CrM operation is particularly suited for isolated flyback LED applications as the control scheme is straightforward and very high efficiency can be achieved even at low power levels. These are important in LED lighting to comply with regulatory requirements and meet overall system luminous efficacy requirements. In CrM, the switching frequency will vary with line and load and switching losses are low as recovery losses in the output rectifier are negligible since the current goes to zero prior to reactivating the main MOSFET switch.

The device features a programmable on time limiter, zero current detect sense block, gate driver, trans-conductance error amplifier as well as all PWM control circuitry and protection functions required to implement a CrM switch mode power supply. Moreover, for high efficiency, the device features low startup current enabling fast, low loss charging of the  $V_{CC}$  capacitor. The current sense protection threshold has been set at 500 mV to minimize power dissipation in the

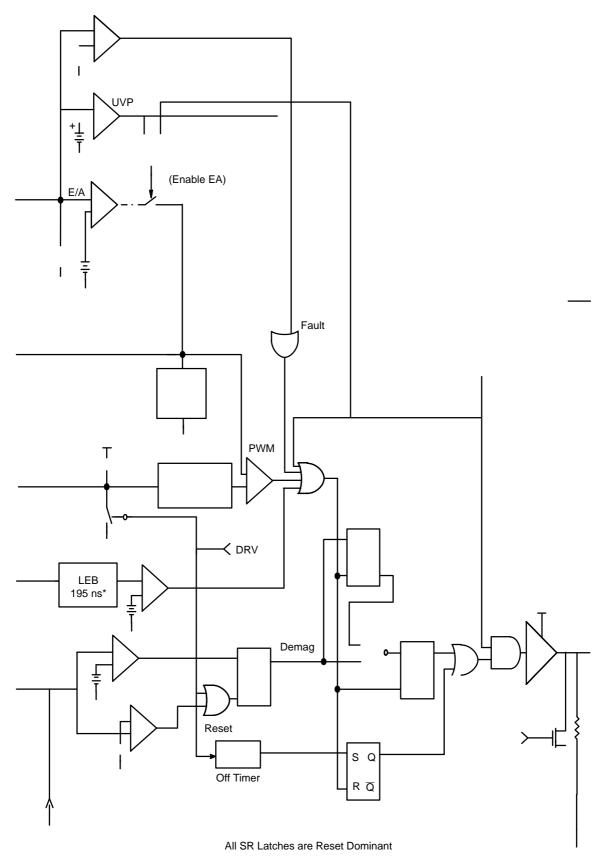

Figure 1. Block Diagram

## Table 1. PIN FUNCTION DESCRIPTION

| Pin | Name            | Function                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MFP             | The multi-function pin is connected to the internal error amplifier. By pulling this pin below the V <sub>uvp</sub> threshold, the controller is disabled. In addition, this pin also has an over voltage comparator which will disable the controller in the event of a fault.                                                                     |

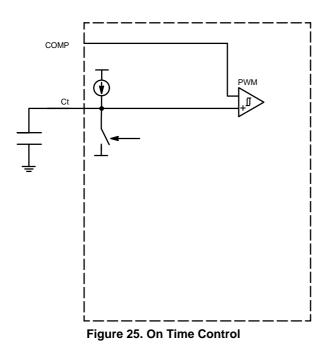

| 2   | COMP            | The COMP pin is the output of the internal error amplifier. A compensation network is connected between this pin and ground to set the loop bandwidth. Normally this bandwidth is set at a low frequency (typically 10 Hz 20 Hz) to achieve high power factor and low total harmonic distortion (THD).                                              |

| 3   | Ct              | The C <sub>t</sub> pin sources a regulated current to charge an external timing capacitor. The PWM circuit controls the power switch on time by comparing the C <sub>t</sub> voltage to an internal voltage derived from V <sub>Control</sub> . The C <sub>T</sub> pin discharges the external timing capacitor at the end of the on time cycle.    |

| 4   | CS              | The CS input is used to sense the instantaneous switch current in the external MOSFET. This signal is filtered by an internal leading edge blanking circuit.                                                                                                                                                                                        |

| 5   | ZCD             | The voltage of an auxiliary zero current detection winding is sensed at this pin. When the ZCD control block circuit detects that the winding has been demagnetized, a control signal is sent to the gate drive block to turn on the external MOSFET.                                                                                               |

| 6   | GND             | This is the analog ground for the device. All bypassing components should be connected to the GND pin with a short trace length.                                                                                                                                                                                                                    |

| 7   | DRV             | The high current capability of the totem pole gate drive (+0.5/ 0.8 A) makes it suitable to effectively drive high gate charge power MOSFETs. The driver stage provides both passive and active pull down circuits that force the output to a voltage less than the turn-on threshold voltage of the power MOSFET when $V_{CC(on)}$ is not reached. |

| 8   | V <sub>CC</sub> | This pin is the positive supply of the controller. The circuit starts to operate when $V_{CC}$ exceeds $V_{CC(on)}$ , nominally 12 V and turns off when $V_{CC}$ goes below $V_{CC(off)}$ , typically 9.5 V. After startup, the operating range is 10.2 V up to 20 V.                                                                               |

#### Overview

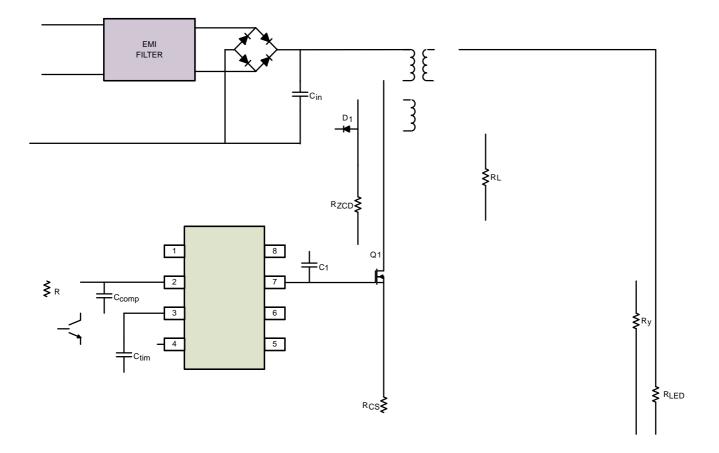

Figure 2 illustrates how the NCL30000 is configured to implement an isolated power factor corrected flyback switch mode power supply. On the secondary side is the NCS1002, a constant voltage, constant current controller which senses the average LED current and the output voltage and provides a feedback control signal to the primary side through an opto-coupler interface. One of the key benefits of active power factor correction is that it makes the load appear like a linear resistance similar to an incandescent bulb. High power factor requires generally sinusoidal line current and minimal phase displacement between the line current and voltage. The NCL30000 operates in a fixed on-time variable frequency mode where

the power switch is on for the same length of time over a half cycle of input power. The current in the primary of the transformer starts at zero each switching cycle and is directly proportional to the applied voltage times the on-time. Therefore with a fixed on-time, the current will follow the applied voltage generating a current of the same shape. Just as in a traditional boost PFC circuit, the control bandwidth is low so that the on-time is constant throughout a single line cycle. The feedback signal from the secondary side is used to modify the average on-time so the current through the LEDs is properly regulated regardless of forward voltage variation of the LED string.

#### **Table 2. MAXIMUM RATINGS**

| Rating                                                                                       | Symbol                   | Value           | Unit |

|----------------------------------------------------------------------------------------------|--------------------------|-----------------|------|

| MFP Voltage                                                                                  | V <sub>MFP</sub>         | 0.3 to 10       | V    |

| MFP Current                                                                                  | I <sub>MFP</sub>         | 10              | mA   |

| COMP Voltage                                                                                 | V <sub>Control</sub>     | 0.3 to 6.5      | V    |

| COMP Current                                                                                 | I <sub>Control</sub>     | 2 to 10         | mA   |

| Ct Voltage                                                                                   | V <sub>Ct</sub>          | 0.3 to 6        | V    |

| Ct Current                                                                                   | I <sub>Ct</sub>          | 10              | mA   |

| CS Voltage                                                                                   | V <sub>CS</sub>          | 0.3 to 6        | V    |

| CS Current                                                                                   | I <sub>CS</sub>          | 10              | mA   |

| ZCD Voltage                                                                                  | V <sub>ZCD</sub>         | 0.3 to 10       | V    |

| ZCD Current                                                                                  | I <sub>ZCD</sub>         | 10              | mA   |

| DRV Voltage                                                                                  | V <sub>DRV</sub>         | 0.3 to $V_{CC}$ | V    |

| DRV Sink Current                                                                             | I <sub>DRV(sink)</sub>   | 800             | mA   |

| DRV Source Current                                                                           | I <sub>DRV(source)</sub> | 500             | mA   |

| Supply Voltage                                                                               | V <sub>CC</sub>          | 0.3 to 20       | V    |

| Supply Current                                                                               | I <sub>CC</sub>          | 20              | mA   |

| Power Dissipation ( $T_A$ = 70 C, 2.0 Oz Cu, 55 mm <sup>2</sup> Printed Circuit Copper Clad) | PD                       | 450             | mW   |

Thermal Resistance Junction-to-Ambient (2.0 Oz Cu, 55 mm<sup>2</sup> Printed Circuit Copper Clad)

**Table 3. ELECTRICAL CHARACTERISTICS** $V_{MFP} = 2.4 \text{ V}, V_{Control} = 4 \text{ V}, Ct = 1 \text{ nF}, V_{CS} = 0 \text{ V}, V_{ZCD} = 0 \text{ V}, C_{DRV} = 1 \text{ nF}, V_{CC} = 12 \text{ V}, unless otherwise specified(For typical values, T_J = 25 C. For min/max values, T_J = 40 C to 125 C, unless otherwise specified)$

| Characteristic                                       | Test Conditions                                       | Symbol                   | Min | Тур  | Max  | Unit |  |

|------------------------------------------------------|-------------------------------------------------------|--------------------------|-----|------|------|------|--|

| STARTUP AND SUPPLY CIRCUITS                          |                                                       |                          |     |      |      |      |  |

| Startup Voltage Threshold                            | V <sub>CC</sub> Increasing                            | V <sub>CC(on)</sub>      | 11  | 12   | 12.5 | V    |  |

| Minimum Operating Voltage V <sub>CC</sub> Decreasing |                                                       | V <sub>CC(off)</sub>     | 8.8 | 9.5  | 10.2 | V    |  |

| Supply Voltage Hysteresis                            |                                                       | H <sub>UVLO</sub>        | 2.2 | 2.5  | 2.8  | V    |  |

| Startup Current Consumption                          | $0 V < V_{CC} < V_{CC(on)}$ 200 mV                    | I <sub>cc(startup)</sub> |     | 24   | 35   | μΑ   |  |

| No Load Switching<br>Current Consumption             | $C_{DRV}$ = Open, 70 kHz Switching,<br>$V_{CS}$ = 2 V | I <sub>cc1</sub>         |     | 1.4  | 1.7  | mA   |  |

| Switching Current Consumption                        | 70 kHz Switching, V <sub>CS</sub> = 2 V               | I <sub>cc2</sub>         |     | 2.1  | 2.6  | mA   |  |

| Fault Condition Current Consumption                  | No Switching, V <sub>MFP</sub> = 0 V                  | I <sub>cc(fault)</sub>   |     | 0.75 | 0.95 | mA   |  |

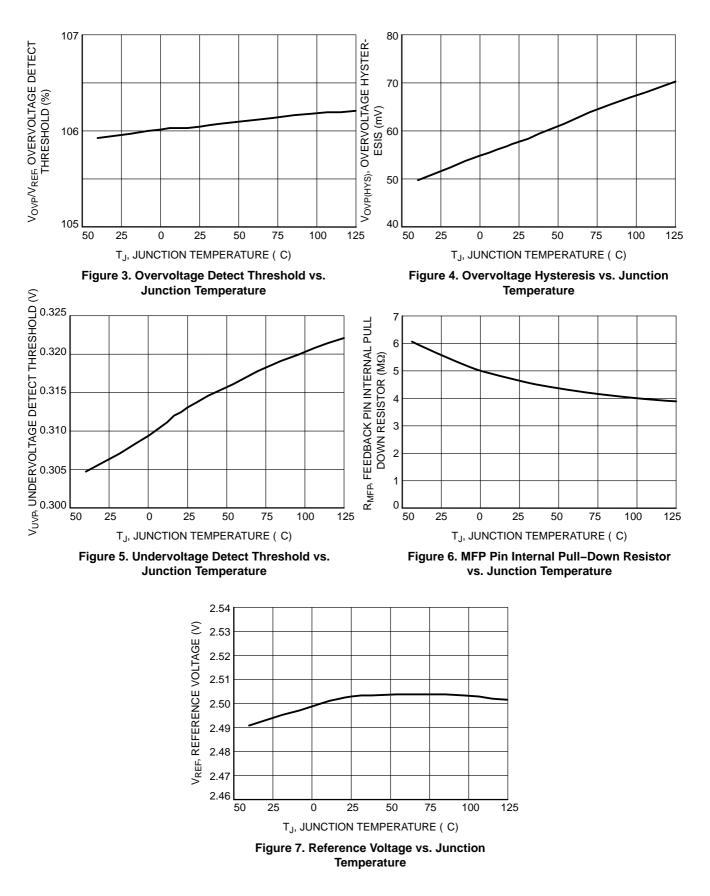

#### OVERVOLTAGE AND UNDERVOLTAGE PROTECTION

| Overvoltage Detect Threshold | V <sub>MFP</sub> = Increasing | V <sub>OVP</sub> /V <sub>REF</sub> | 105 | 106 | 108 | %  |

|------------------------------|-------------------------------|------------------------------------|-----|-----|-----|----|

| Overvoltage Hysteresis       |                               | V <sub>OVP(HYS)</sub>              | 20  | 60  | 100 | mV |

Overvoltage Detect Threshold Propagation Delay

V<sub>MFP</sub> = 2 V to 3 V ramp, C, 613.077 .68036 15.364 ref511 52-94(V)MFP

**Table 3. ELECTRICAL CHARACTERISTICS** (Continued) $V_{MFP} = 2.4 \text{ V}$ ,  $V_{Control} = 4 \text{ V}$ , Ct = 1 nF,  $V_{CS} = 0 \text{ V}$ ,  $V_{ZCD} = 0 \text{ V}$ ,  $C_{DRV} = 1 \text{ nF}$ ,  $V_{CC} = 12 \text{ V}$ , unless otherwise specified(For typical values,  $T_J = 25 \text{ C}$ . For min/max values,  $T_J = 40 \text{ C}$  to 125 C, unless otherwise specified)

| Characteristic                   | Test Conditions                                    | Symbol               | Min   | Тур  | Max   | Unit |

|----------------------------------|----------------------------------------------------|----------------------|-------|------|-------|------|

| RAMP CONTROL                     |                                                    |                      |       |      |       |      |

| Ct Peak Voltage                  | V <sub>COMP</sub> = open                           | V <sub>Ct(MAX)</sub> | 4.775 | 4.93 | 5.025 | V    |

| On Time Capacitor Charge Current | $V_{COMP} = open$<br>$V_{Ct} = 0 V to V_{Ct(MAX)}$ |                      |       | -    | -     |      |

### THEORY OF OPERATION

High power factor requires generally sinusoidal line current and minimal phase displacement between the line current and voltage. Normally this is not the case with a traditional isolated flyback topology so the first step to achieve high power factor is to have minimal capacitance before the switching stage to allow a more sinusoidal input current. A simplified block diagram is illustrated in Figure 23. Since the input bulk capacitor has virtually been eliminated except for a small capacitor, the voltage to the flyback converter now follows a rectified sine shape at twice the line frequency. By employing a critical conduction mode control technique such that the input current is kept to the same shape, high power factor can be achieved. The NCL30000 is a voltage mode, fixed on-time controller specifically intended for such applications.

The LED current is compared to a reference and an error signal is passed to the NCL30000 controller to maintain the desired average level. This error signal adjusts the on-time of the power switch to pass the required energy through the flyback transformer to achieve proper regulation of the LED load. Just like in a traditional PFC boost converter, the loop bandwidth must be low enough to filter out the twice line frequency ripple otherwise the power factor correction element of the circuit will be compromised. In the event of

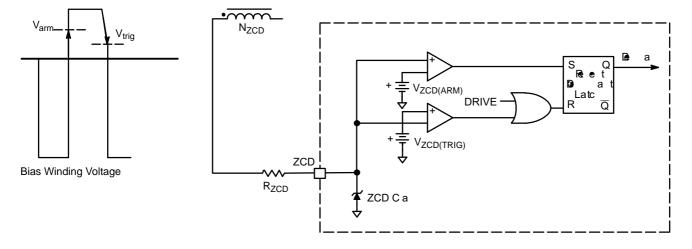

#### **ZCD Detection Block**

A dedicated circuit block is necessary to implement the zero current detection. The NCL30000 provides a separate input pin to signal the controller to turn the power switch back on just after the flyback transformer discharges all the stored energy to the secondary winding. When the output winding current reaches zero the winding voltage will reverse. Since all windings of the transformer reflect the same voltage characteristic this voltage reversal appears on the primary bias winding. Coupling the winding voltage to the ZCD input of the NCL30000 allows the controller to start

the next switching cycle at the precise time. To avoid inadvertent false triggering, the ZCD input has a dual comparator input structure to arm the latch when the ZCD detect voltage rises above 1.4 V (nominal) thus setting the latch. When the voltage on ZCD falls below 0.7 V (nominal) a zero current event is detected and a signal is asserted which initiates the next switching cycle. This is illustrated in Figure 27. The input of the ZCD has an internal circuit which clamps the positive and negative voltage excursions on this pin. The current into or out of the ZCD pin must be limited to 10 mA with an external resistor.

At startup, there is no energy in the ZCD winding and no voltage signal to activate the ZCD comparators. To enable the controller to start under these conditions, an internal watchdog timer is provided which initiates a switching cycle in the event that the output drive has been off for more than 180 µs (nominal).

The timer is deactivated only under an OVP or UVP fault condition which will be discussed in the next section.

#### **Overcurrent Protection (OCP)**

The dedicated CS pin of the NCL30000 senses the current through the MOSFET switch and the primary side of the transformer. This provides an additional level of protection in the event of a fault. If the voltage of the CS pin exceeds  $V_{ILIM}$ , the internal comparator will detect the event and turn off the MOSFET. The peak switch current is calculated using Equation 1:

$$I_{SW(peak)} = \frac{V_{ILIM}}{R_{sense}}$$

(eq. 1)

To avoid the probability of false switching, the

Figure 30. Wide Input Main, 4–15 LED 350 mA Load Schematic

#### Zero Current Detection (ZCD)

The signal controlling the ZCD function is taken from the primary bias winding. Raising the ZCD pin above 1.4 V arms the zero detection circuit. When the pin voltage subsequently falls below 0.7 V, the controller issues the command to turn the power switch back on. The current in or out of the ZCD pin must be limited to 10 mA by an external resistor. For this reference circuit a resistance of 47 k $\Omega$  provides the required voltage thresholds and limits current to less than 10 mA.

#### **Feedback Control**

The secondary feedback signal is routed through an optocoupler to the primary side NCL30000 controller. LED current is measured with a 0.2  $\Omega$  resistor which for 350 mA has a voltage drop of 70 mV.

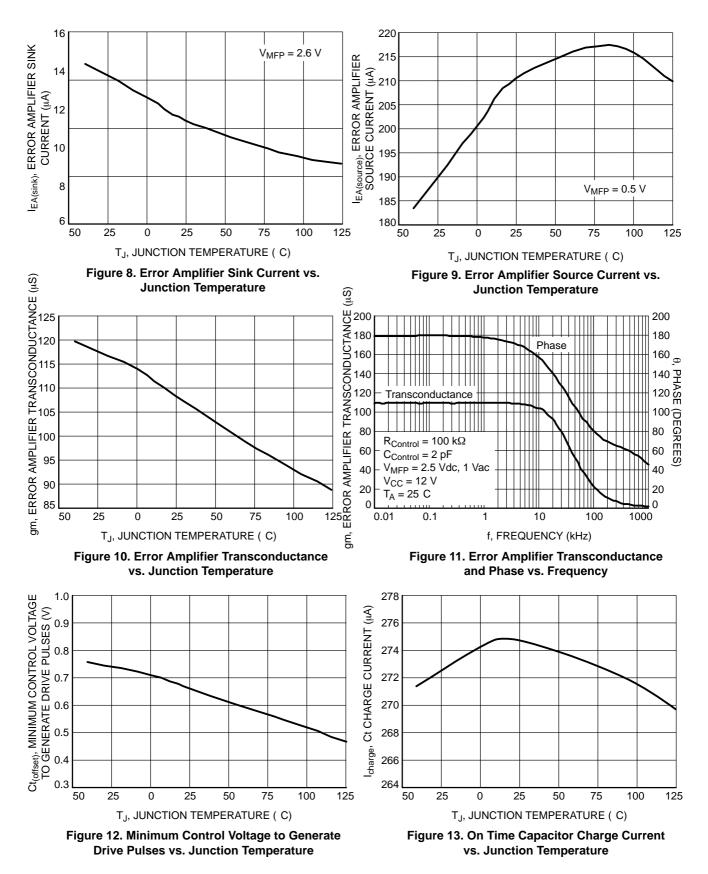

The control loop must be designed to filter out the rectified sine wave ripple component to provide an average feedback level to the pulse width controller. In order to maintain high power factor operation, the compensation components around the error amplifier must be set well below 50/60 Hz. The corner frequency typically falls between 10 and 40 Hz. The low frequency response means the control loop will be slow to compensate for rapidly changing situations. In particular, the slow response can introduce overshoot at turn on.

To compensate for the slow steady state loop this circuit utilizes a second current control loop to minimize overshoot. The second loop is set for higher than nominal operating current with a very fast response loop. This error amp takes control of the feedback loop until the main error amp is able to respond. In this way the maximum current is limited to safe established level.

The current set point of the fast control loop should be set above the peak of the ripple current of normal operation. U4 is a 2.5 V reference which in conjunction with insulated wire is selected for compliance with safety agency isolation requirements.

The primary bias winding must supply 10.2 V to maintain NCL30000 operation. The minimum secondary voltage is 12 V and with 24 turns this means the bias winding needs 20.4 turns. Select 22 turns to meet the minimum.

For maximum primary to secondary coupling, the primary winding will be split in two equal sections with the secondary winding placed in between. The bias winding is wound on top of the second half of the primary winding.

#### **FET Switch**

The NCL30000 controller drives an external power FET controlling the current in the flyback transformer primary. The demonstration board was designed to accept the surface mount DPAK or through-hole TO 220 power packages. The 17.5 W target application in 50 C ambient works well with a DPAK package. The 800 V 2 A rated SPD02N80C3 was chosen.

Maximum primary current was calculated as 1.11 A. The NCL30000 has a 0.5 V over-current protection threshold. To allow for 25% margin, a minimum sense resistor of 0.348  $\Omega$  is required. A standard 0.33  $\Omega$  resistor will be selected. The current sense resistor is placed in the source lead of the power FET and coupled to the controller with a 100  $\Omega$  resistor. This resistance in conjunction with the inherent capacitance of the pin filters high frequency noise. In addition, a

Load

Figure 35 shows output ripple current for 115 Vac input and 36.9 (12 LED) load operating at 350 mA average. Scale factor is 67 mA per division. The low frequency ripple follows the input twice line frequency rectified sine wave characteristic of single stage converters.

#### Figure 35. Output Ripple at 115 Vac and 36.9 V, 350 mA Load

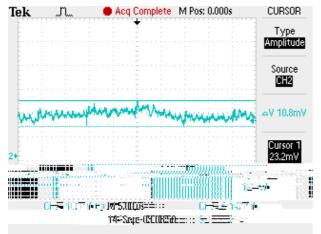

Figure 36 shows output ripple current at the main switching frequency. Scale factor is 33 mA per division. This is the signal superimposed over the rectified sine wave ripple component.

Figure 36. Output Ripple at 115 Vac and 36.9 V, 350 mA Load

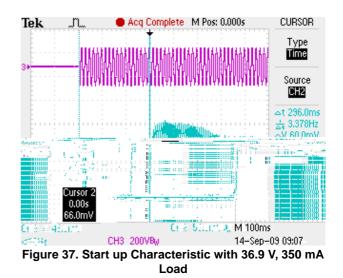

Initial start up characteristic is shown in Figure 37 below. Note the higher current limit controlled by the fast feedback loop and the transition to the main average mode feedback control loop. This shows start up at 115 Vac with 36.9 V, 350 mA load. Trace 2 is LED current at 167 mA per division and trace 3 is applied input voltage at 200 V per division.

Typical voltage stress on power FET with 36.9 V, 350 mA load and 305 Vac input voltage is shown in Figure 38. Scale factor is 100 V per division.

#### Figure 38. Drain to Source Voltage with 36.9 V, 350 mA Load at 305 Vac Input

Note that while the power supply was designed to meet agency requirements, it has not been submitted for compliance. Standard safety practices should be used when this circuit is energized and in particular when connecting test equipment. During evaluation, input power should be sourced through an isolation transformer.

#### Additional Application Information and Tools

An evaluation board is available for this 90 305 Vac design example. Moreover, for applications where it is desired to dim the LEDs via a TRIAC dimmer, please refer to Application Note AND8448 which explains the steps necessary to configure the NCL30000 for TRIAC dimming. In addition there are two additional TRIAC dimmable reference designs which illustrate a complete design for 90 135 Vac or 180 265 Vac operation. There is also an Microsoft EXCEL spreadsheet tool available to aid in the design process and assist in developing target winding requirements for the transformer. SOIC-8 NB CASE 751-07 ISSUE AK

DATE 16 FEB 2011

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. 5. GATE 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 COLLECTOR, DIE #2 3. EMITTER, COMMON 4. 5. EMITTER, COMMON 6. BASE, DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 SOURCE GATE 4. 5. DRAIN 6. 7. DRAIN DRAIN DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT 3. 4. TXE 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C 3. REXT 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2. EMITTER, #1 BASE, #2 3. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 8. EMITTER, #1 STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. 5. SOURCE 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. 3. GROUND 4. 5. GROUND 6. BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. 5. P-DRAIN 6. 7. P-DRAIN N-DRAIN N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 3. SOURCE 2 4. 5. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 6.

STYLE 3: PIN 1. 2. DRAIN, DIE #1 DRAIN, #1 DRAIN, #2 3. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND 3. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 2. GATE 1 SOURCE 2 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON 6. 7. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 8. STYLE 19: SOURCE 1 PIN 1. 2. GATE 1 SOURCE 2 3. 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 3. UVLO 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8. DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE 3. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE 2. SOURCE SOURCE 3. 4. GATE 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. 7. COLLECTOR, DIE #2 COLLECTOR, DIE #1 COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) SOURCE (P) 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER COLLECTOR/ANODE 3 COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC\_OFF 3. DASIC\_SW\_DET 4. GND 5. 6. V MON VBULK 7. VBULK 8. VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |  |

| ON Semiconductor and 💷 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |             |                                                                                                                                                                                     |             |  |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

6. 7.

8

rights of others

COLLECTOR, #1

COLLECTOR, #1