### Features

- Voltage Mode CrM Power Factor Correction Controller

- PFC Open Feedback Loop Protection

- PFC Undervoltage Detector

- PFC Overvoltage Detector

- Half–Bridge Stage with 600 V High Side Gate Drive

- State Machine Ensures Proper Turn-on and Turn-off of Half-Bridge Stage

- Controllers are Properly Sequenced for Fault Fr1€

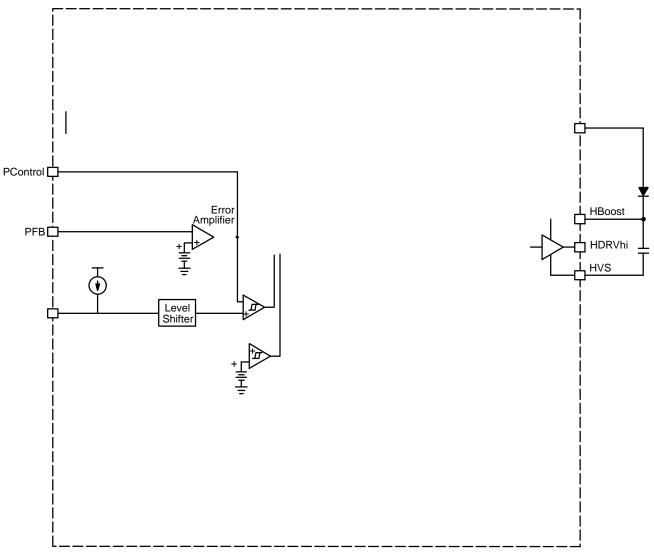

Figure 1. Functional Block Diagram

## Table 2. MAXIMUM RATINGS (Notes 1 and 2)

| Rating                                                                                                                                               | Symbol                      | Value                                     | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|------|

| High Voltage Input Voltage                                                                                                                           | V <sub>HV</sub>             | -0.3 to 600                               | V    |

| High Voltage Input Current                                                                                                                           | I <sub>HV</sub>             | 10                                        | mA   |

| Supply Input Voltage                                                                                                                                 | V <sub>CC</sub>             | -0.3 to 20                                | V    |

| Supply Input Current                                                                                                                                 | ICC                         | 10                                        | mA   |

| Oscillator Input Voltage                                                                                                                             | Vosc                        | –0.3 to V <sub>REF</sub>                  | V    |

| Oscillator Input Current                                                                                                                             | losc                        | 10                                        | mA   |

| Bandgap Reference Decoupling Output Voltage                                                                                                          | V <sub>REF</sub>            | -0.3 to 9                                 | V    |

| Bandgap Reference Decoupling Output Current                                                                                                          | I <sub>REF</sub>            | 10                                        | mA   |

| PFC Feedback Voltage Input Voltage                                                                                                                   | V <sub>PFB</sub>            | -0.3 to 10                                | V    |

| PFC Feedback Voltage Input Current                                                                                                                   | I <sub>PFB</sub>            | 10                                        | mA   |

| PFC Current Sense Input Voltage                                                                                                                      | V <sub>PCS</sub>            | -0.3 to 10                                | V    |

| PFC Current Sense Input Current                                                                                                                      | I <sub>PCS</sub>            | 10                                        | mA   |

| PFC Zero Current Detection Input Voltage                                                                                                             | V <sub>PZCD</sub>           | -0.3 to 10                                | V    |

| PFC Zero Current Detection Input Current                                                                                                             | I <sub>PZCD</sub>           | 10                                        | mA   |

| PFC Control Input Voltage                                                                                                                            | V <sub>PControl</sub>       | –0.3 to V <sub>REF</sub>                  | V    |

| PFC Control Input Current                                                                                                                            | I <sub>PControl</sub>       | 1.2                                       | mA   |

| PFC On Time Control Input Voltage                                                                                                                    | V <sub>PCT</sub>            | –0.3 to V <sub>REF</sub>                  | V    |

| PFC On Time Control Input Current                                                                                                                    | I <sub>PCT</sub>            | 9                                         | mA   |

| PFC Drive Signal Voltage                                                                                                                             | V <sub>PDRV</sub>           | -0.3 to V <sub>CC</sub>                   | V    |

| PFC Drive Signal Current                                                                                                                             | I <sub>PDRV</sub>           | 100                                       | mA   |

| Half-Bridge Low Side Driver Input Voltage                                                                                                            | V <sub>HDRVIo</sub>         | -0.3 to V <sub>CC</sub>                   | V    |

| Half-Bridge Low Side Driver Input Current                                                                                                            | I <sub>HDRVI0</sub>         | 100                                       | mA   |

| Half-Bridge High Side Driver Source Connection Input Voltage                                                                                         | V <sub>HVS</sub>            | -1.0 to 600                               | V    |

| Half-Bridge High Side Driver Source Connection Input Current                                                                                         | I <sub>HVS</sub>            | 100                                       | mA   |

| Half-Bridge High Side Driver Input Voltage                                                                                                           | V <sub>HDRVhi</sub>         | -1.3 to V <sub>HVS</sub> +V <sub>CC</sub> | V    |

| Half-Bridge High Side Driver Input Current                                                                                                           | I <sub>HDRVhi</sub>         | 100                                       | mA   |

| Half-Bridge High Side Driver Charge Pump Input Voltage                                                                                               | V <sub>HBoost</sub>         | –0.3 to V <sub>HVS</sub> +V <sub>CC</sub> | V    |

| Half-Bridge High Side Driver Charge Pump Input Current                                                                                               | I <sub>HBoost</sub>         | 100                                       | mA   |

| High Side Boost Circuit Supply Voltage (between HBoost and HVS pins)                                                                                 | V <sub>HBoost(supply)</sub> | –0.3 to $V_{CC}$                          | V    |

| High Side Boost Circuit Supply Voltage (between HBoost and HVS pins)                                                                                 | I <sub>HBoost(supply)</sub> | 100                                       | mA   |

| Half-Bridge High Side Driver Source Connection Slew Rate                                                                                             | dV <sub>HVS</sub> /dt       | 50                                        | V/ns |

| Junction Temperature (Biased)                                                                                                                        | TJ                          | 150                                       | °C   |

| Storage Temperature Range                                                                                                                            | T <sub>stg</sub>            | -60 to 150                                | °C   |

| Power Dissipation ( $T_A = 25^{\circ}C$ , 1 Oz Cu, 0.155 Sq Inch, Printed Circuit Copper Clad)<br>D Suffix, Plastic Package Case 751B–05 (SOIC–16)   | P <sub>D</sub>              | 0.95                                      | W    |

| Thermal Resistance, Junction to Ambient<br>(1 Oz Cu, 0.155 Sq Inch, Printed Circuit Copper Clad)<br>D Suffix, Plastic Package Case 751B–05 (SOIC–16) | R <sub>θJA</sub>            | 130                                       | °C/W |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.This device(s) contains ESD protection and exceeds the following tests:

Pins 1, 14, 15 and 16 rated to the maximum voltage of the respective pins based on the maximum ratings table. All Other Pins: Human Body Model 1500 V per JEDEC Standard JESD22–A114E. Machine Model 150 V per JEDEC Standard JESD22–A115–A.

This device contains Latch–Up protection and exceeds ± 100 mA per JEDEC Standard JESD78.

| Table 3. ELECTRICAL CHARACTERISTICS (V <sub>HV</sub> = open, V <sub>PFB</sub> = 2.4 V, V <sub>PCS</sub> = 0 V, V <sub>PZCD</sub> = 5 V, V <sub>PControl</sub> = open, V <sub>CC</sub> = 15 V,                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PDRV</sub> = open, V <sub>HDRVI0</sub> = open, V <sub>HVS</sub> = 0 V, V <sub>HDRVhi</sub> = open, V <sub>HBoost</sub> = 15 V, C <sub>OSC</sub> = 2200 pF, C <sub>VREF</sub> = 0.1 μF, C <sub>PCT</sub> = 1000 pF, for typical |

| values $T_J = 25^{\circ}C$ , for min/max values, $T_J$ is $-40^{\circ}C$ to $125^{\circ}C$ , unless otherwise noted)                                                                                                                  |

| Characteristics                                        | Conditions                                           | Symbol                                            | Min   | Тур   | Max   | Unit |

|--------------------------------------------------------|------------------------------------------------------|---------------------------------------------------|-------|-------|-------|------|

| STARTUP AND SUPPLY CIRCUITS                            |                                                      | ·                                                 | •     |       | •     |      |

| Supply Voltage                                         |                                                      |                                                   |       |       |       | V    |

| Startup Threshold                                      | V <sub>CC</sub> Increasing                           | V <sub>CC(on)</sub>                               | 14.3  | 15.3  | 16.3  |      |

| Minimum Enable Threshold                               | V <sub>CC</sub> Decreasing                           | V <sub>CC(enable)</sub>                           | 13.6  | 14.6  | 15.6  |      |

| Minimum Operating Voltage                              | V <sub>CC</sub> Decreasing                           | V <sub>CC(off)</sub>                              | 8.5   | 9.3   | 10.0  |      |

| Supply Current                                         |                                                      |                                                   |       |       |       | mA   |

| Device Disabled/Fault                                  | $V_{PFB} = V_{PUVP(low)}$                            | I <sub>CC1</sub>                                  | 0.8   | 1.4   | 1.8   |      |

| Device Switching                                       | (Note 3)                                             | I <sub>CC2</sub>                                  | 1.8   | 2.4   | 3.0   |      |

| Startup Current                                        | $V_{CC} = V_{CC (on)} - 0.2 V,$<br>$V_{HV} = 50 V$   | <sub>n)</sub> – 0.2 V, I <sub>start</sub><br>50 V |       | 7.5   | 10.5  | mA   |

| Startup Circuit Off-State Leakage Current              | $V_{HV} = 600 V,$<br>$V_{CC} = V_{CC (on)} + 0.2 V$  |                                                   |       | 15    | 50    | μΑ   |

| BANDGAP REFERENCE                                      |                                                      | •                                                 |       |       | •     |      |

| Reference Voltage                                      | C <sub>REF</sub> = 0.1 μF                            | V <sub>REF</sub>                                  | 6.605 | 7.000 | 7.295 | V    |

| OSCILLATOR                                             |                                                      | ·                                                 |       |       | •     |      |

| Half-Bridge Clock Frequency                            | V <sub>HVS</sub> = 50 V                              | f <sub>clock</sub>                                | 13.5  | 15.5  | 16.5  | kHz  |

| Maximum Half-Bridge Clock Frequency                    | C <sub>OSC</sub> = open                              | f <sub>clock(MAX)</sub>                           | 75    | -     | -     | kHz  |

| PFC ERROR AMPLIFIER                                    |                                                      | •                                                 | •     |       | •     |      |

| PFC Feedback Voltage Reference                         |                                                      | V <sub>PREF</sub>                                 |       |       |       | V    |

|                                                        | 0°C < TJ < 125°C                                     |                                                   | 2.42  | 2.50  | 2.58  |      |

|                                                        | –40°C < T <sub>J</sub> < 125°C                       |                                                   | 2.40  | -     | 2.60  |      |

| PFC Feedback Voltage Reference<br>Regulation with Line | V <sub>CC(on)</sub> + 0.2 V < V <sub>CC</sub> < 20 V | V <sub>PREF(line)</sub>                           | -15   | -     | 15    | mV   |

| Error Amplifier Drive Capability                       |                                                      |                                                   |       |       |       | μΑ   |

| Sink                                                   | $V_{PControl} = 4 V, V_{PFB} = 5 V$                  | I <sub>EA(SNK)</sub>                              | 60    | 80    | -     |      |

| Source                                                 | $V_{PControl} = 4 V, V_{PFB} = 0.5 V$                | I <sub>EA(SRC)</sub>                              | -60   | -80   | -     |      |

Open Loop Error Amplifier **of 438/VI 048/68/W132 1572 384558: 522:** 28 **1522:** 28 **1804:08** 30.72 .8 409.68 Tm0 Tc43 ref55[(T 2 T72 15T72 1Tm0 Tc(80)Tj-.2s[(CC()-19.8(o)-18.3(n .72 refBT8)

Table 5. ELECTRICAL CHARACTERISTICS

# DETAILED OPERATING DESCRIPTION

- Low pin-count of controller combines strong feature set

- Low external component count

- ZVS of the second stage FETs without any tuning requirements

- High efficiency facilitates improved thermal performance

- Low EMI and easy filtering due to fixed frequency

- Facilitation of synchronous rectification control design

- Easier design of magnetic components (esp. Resonant transformer and inductor)

While the above listed benefits make this approach a very interesting proposition for many isolated applications

# PFC Output Capacitor - Cbulk

The bulk capacitor is one of the most critical components

## **High Voltage Startup Circuit**

The NCL30051 internal startup regulator eliminates the need for external startup components. In addition, this regulator increases the efficiency of the supply as it uses no power when in the normal mode of operation, but instead uses power supplied by an auxiliary winding. The startup regulator consists of a constant current source that supplies current from the high voltage line (V<sub>in</sub>) to the supply capacitor on the V<sub>CC</sub> pin (C<sub>CC</sub>). The startup current (I<sub>start</sub>) is typically 7.5 mA. The startup circuit is rated at a maximum voltage of 600 V.

Once  $C_{CC}$  is charged to 15.3 V ( $V_{CC(on)}$ ), the startup regulator is disabled and the PFC controller is enabled if the PFB voltage exceeds  $V_{PUVP(high)}$ . The startup regulator remains disabled until the lower supply threshold,  $V_{CC(off)}$ , (typically 9.3 V) is reached. Once reached, the drive outputs are disabled and the startup current source is enabled. Once the outputs are disabled, the bias current of the NCL30051 is reduced, allowing  $V_{CC}$  to charge back up.

The supply capacitor provides power to the controller while operating in the power up or self–bias mode. During the converter power up,  $C_{CC}$  must be sized such that a  $V_{CC}$  voltage greater than  $V_{CC(off)}$  is maintained while the auxiliary supply voltage is building up. Otherwise,  $V_{CC}$  will collapse and the controller will turn off. The IC bias current and gate charge load at the drive outputs must be considered to correctly size  $C_{CC}$ . The increase in current consumption due to external gate charge is calculated using Equation 1.

$$I_{CC(qate charge)} = f \cdot Q_{G}$$

(eq. 1)

where, f is the operating frequency and  $Q_G$  is the gate charge of the external MOSFETs.

#### Main Oscillator

The oscillator frequency is set by the oscillator capacitor,  $C_{OSC}$ , on the OSC pin. The oscillator operates at a fixed 80% duty ratio. A current source charges  $C_{OSC}$  to its peak voltage, typically 5 V. Once the peak voltage is reached, the charge current is disabled and  $C_{OSC}$  is discharged down to 3 V by another current source. The charge and discharge currents are typically 173 and 692  $\mu$ A, respectively. The oscillator frequency vs oscillator capacitance graph is shown in Figure 3.

CC Figure 3. Oscillator Frequency vs. Oscillator Capacitor

## **PFC Regulator**

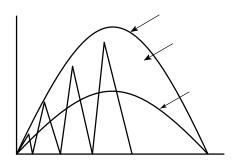

The PFC inductor current,  $I_{L(t)}$ , reaches zero at the end of the switch cycle as shown in Figure 4 and the average input current,  $I_{in(t)}$ , is in phase with the ac line voltage,  $V_{in(t)}$ .

Figure 4. Inductor Current in CrM

## **PFC Startup**

The output of the error amplifier is pulled low with an internal pull down transistor when the supply voltage has not reached  $V_{CC(on)}$  or if there is a PFC undervoltage fault. This ensures a soft–start sequence once the PFC is enabled and eliminates output voltage overshoot during on/off tests. Once the error amplifier is enabled the output of the error amplifier charges quickly to the minimum clamp voltage.

## **Off Time Control**

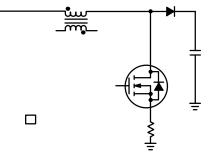

The PFC off time varies with the instantaneous line voltage and it is adjusted every cycle to allow the inductor current to reach zero before the next switch cycle begins. The inductor is demagnetized once its current reaches zero. Once the inductor is demagnetized the drain voltage of the PFC switch begins to drop. The inductor demagnetization is detected by sensing the voltage across the inductor using an auxiliary winding. This winding is commonly known as a zero crossing detector (ZCD) winding. This winding provides a scaled version of the inductor voltage. Figure 6 shows the ZCD winding arrangement.

Figure 6. ZCD Winding Implementation

$V_{PFC} = V_{PREF} \cdot \frac{R_1 + R_2}{R_2} + I_{PFB} \cdot$

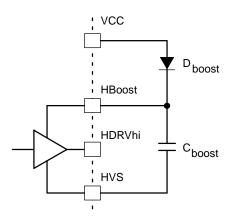

Figure 10. Half-bridge High Side Driver

A boost circuit comprised of  $D_{boost}$  and  $C_{boost}$  generates the supply voltage for the high side driver. Once HDRVlo turns on, the HVS pin is effectively grounded through the external power switch. This allows  $C_{boost}$  to charge to  $V_{CC}$ . Once HDRVlo turns off, HVS floats high and  $D_{boost}$  is reversed biased. An undervoltage detector monitors the HBoost voltage. Once the HBoost voltage is greater than  $V_{Boost(UV)}$ , typically, 6.1 V, the high side driver is enabled. The low side driver generally starts before the high side driver because the boost voltage is generated by the low side driver switch transitions.

The half-bridge low side driver source and sink impedances are typically 75 and 15  $\Omega$ , respectively. The half-bridge high side driver source and sink impedances are typically 75 and 15  $\Omega$ , respectively. Depending on the external MOSFETs gate charge requirements, an external driver may be needed to drive the low and high side power switches.

## Analog and Power Ground

The NCL30051 has an analog ground, GND, and a power ground, PGND, terminal. GND is used for analog connections such as VREF and OSC. PGND is used for high current connections such as the gate drivers. It is recommended to have independent analog and power ground planes and connect them at a single point, preferably at the ground terminal of the system. This will prevent high current flowing on PGND from injecting noise in GND. The PGND connection should be as short and wide as possible to reduce inductance—induced spikes.

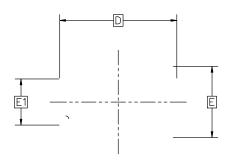

#### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

DATE 18 OCT 2024

- DIMENSIONS D AND E1 DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.1<sup>r</sup>

**b** DIMENSION AT MAXIMUM MATE

nm TOTAL IN EXCESS OF THE

<u>top view</u>

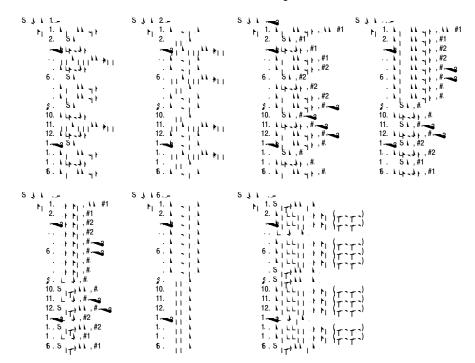

#### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

#### DATE 18 OCT 2024

### GENERIC MARKING DIAGRAM\*

| 16 | A        | - A | - A | - A | - A | A   | A.  | E |

|----|----------|-----|-----|-----|-----|-----|-----|---|

|    |          | XX) | (X) | XX  | XX) | XX) | (X) | G |

|    |          | XX  | XX  | XX) | XX) | XX  | XX  | X |

|    | • AWLYWW |     |     |     |     |     |     |   |

| 1  | Ŧ        | H   | H   | H   | H   | Н   | H   | Ъ |

XXXXX = Specific Device Code

A = Assembly Location

- WL = Wafer Lot

- Y = Year

- WW = Work Week

- G = Pb Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42566B              | 66B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1 | PAGE 2 OF 2                                                                                                                                                                             |  |  |  |  |

|                  |                          |                                                                                                                                                                                         |  |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi