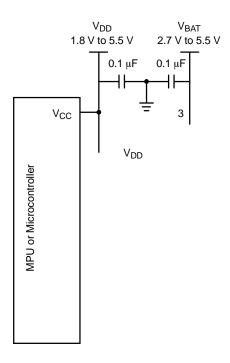

Figure 1. Typical Interface Application

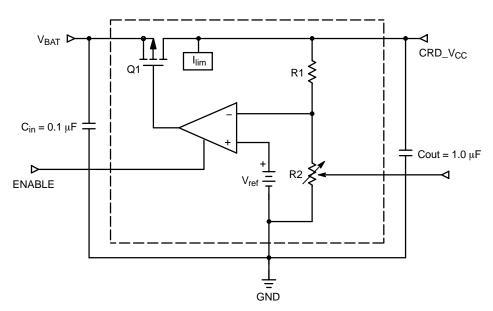

Figure 3. NCN4557 Block Diagram

# **PIN DESCRIPTIONS**

| PIN | Name                  | Туре   | Description                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CRD_V <sub>CC</sub> B | POWER  | This pin is connected to the Card power supply pin (C1) (Card B). The corresponding LDO is programmable using the pins SEL0, SEL1 and ENABLE to provide 1.8 V, 3.0 V or 0 V (disable).                                                                                                                                                                   |

|     | 4                     | .edo-5 | 8CRB _4/ <sub>CC</sub> B can not be active when CRD_V <sub>CC</sub> A is active and conversely.                                                                                                                                                                                                                                                          |

| 2   | $V_{DD}$              | POWER  | This pin is connected to the controller power supply. It configures the level shifter input stage to accept the signal coming from the microcontroller. A 0.1 $\mu$ F capacitor shall be used to bypass the power supply voltage. When $V_{DD}$ is below 1.5 V typical CRD_V <sub>CC</sub> A and B are disabled; the NCN4557 comes into a shutdown mode. |

| 3   | $V_{BAT}$             | POWER  | DC/DC converter power supply input shared by the LDOs A & B. This pin has to be bypassed by a 0.1 µF capacitor.                                                                                                                                                                                                                                          |

| 4   | CRD_V <sub>CC</sub> A | POWER  |                                                                                                                                                                                                                                                                                                                                                          |

# **ATTRIBUTES**

| Characteristics                                        | Values               |

|--------------------------------------------------------|----------------------|

| ESD protection                                         |                      |

| Human Body Model (HBM):                                |                      |

| Card Pins (1, 4, 5, 6, 7, 14, 15, 16 & 17) (Note 1)    | 8 kV                 |

| All Other Pins (Note 1)                                | 2 kV                 |

| Machine Model (MM):                                    |                      |

| Card Pins (1, 4, 5, 6, 7, 14, 15, 16 & 17)             | 600 V                |

| All Other Pins                                         | 200 V                |

| Charged Device Model (CDM):                            |                      |

| Card Pins (1, 4, 5, 6, 7, 14, 15, 16 & 17)             | 2 kV                 |

| All Other Pins                                         | 400 V                |

| Moisture sensitivity (Note 2) QFN-16                   | Level 1              |

| Flammability Rating Oxygen Index: 28 to 34             | UL 94 V-0 @ 0.125 in |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test |                      |

- Human Body Model (HBM): R =1500 Ω, C = 100 pF.

For additional information, see Application Note AND8003/D.

# **MAXIMUM RATINGS**

| Rating                            | Symbol              | Value                                                        | Unit    |

|-----------------------------------|---------------------|--------------------------------------------------------------|---------|

| LDO Power Supply Voltage          | V <sub>BAT</sub>    | -0.5 ≤ V <sub>BAT</sub> ≤ 6                                  | V       |

| Power Supply Microcontroller Side | V <sub>DD</sub>     | $-0.5 \le V_{DD} \le 6$                                      | V       |

| External Card Power Supply        | CRD_V <sub>CC</sub> | -0.5 ≤ CRD_V <sub>CC</sub> ≤ 6                               | V       |

| Digital Input Pins                | V <sub>in</sub>     | $-0.5 \le V_{in} \le V_{DD} + 0.5$<br>but < 6.0<br>±5        | V<br>mA |

| Digital Output Pins               | V <sub>out</sub>    | $-0.5 \le V_{out} \le V_{DD} + 0.5$<br>but < 6.0<br>$\pm 10$ | V<br>mA |

| CRD Output Pins                   | V <sub>out</sub>    |                                                              | •       |

CRD\_I/O & CRD\_RST Pins CRD\_CLK Pin lout

# POWER SUPPLY SECTION (-40°C to +85°C)

| Pin | Symbol            | Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Min | Тур | Max | Unit |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 3   | V <sub>BAT</sub>  | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.7 |     | 5.5 | V    |

| 3   | I <sub>VBAT</sub> | $ \begin{array}{l} \text{Operating current} \\ \text{CRD\_V}_{CC}\text{A} = 3.0 \text{ V, CRD\_V}_{CC}\text{B} = 0 \text{ V, I}_{CC}\text{A \& B} = 0 \text{ mA} \\ \text{CRD\_V}_{CC}\text{A} = 1.8 \text{ V, CRD\_V}_{CC}\text{B} = 0 \text{ V, I}_{CC}\text{A \& B} = 0 \text{ mA} \\ \text{CRD\_V}_{CC}\text{A} = 0 \text{ V, CRD\_V}_{CC}\text{B} = 3.0 \text{ V, I}_{CC}\text{A \& B} = 0 \text{ mA} \\ \text{CRD\_V}_{CC}\text{A} = 0 \text{ V, CRD\_V}_{CC}\text{B} = 1.8 \text{ V, I}_{CC}\text{A \& B} = 0 \text{ mA} \\ \end{array} $ |     |     |     |      |

#### APPLICATION INFORMATION

The NCN4557 is a dual LDO-based DC/DC converter and level shifter able to handle independently 2 smart card interfaces. When one of these interfaces is operating the other one is not active and conversely. Class B (3.0 V) and C (1.8 V) cards can be used.

The Card and the CRD\_V<sub>CC</sub> power supply are selected using the pins SEL0, SEL1 and ENABLE according to Table 1.

Table 1. CARD AND CRD\_V<sub>CC</sub> SELECTION

| ENABLE | SEL1 | SEL0 | Card# / CRD_V <sub>CC</sub> |

|--------|------|------|-----------------------------|

| 1      | 0    | 0    | Card A / 1.8 V              |

| 1      | 0    | 1    | Card A / 3.0 V              |

| 1      | 1    | 0    | Card B / 1.8 V              |

| 1      | 1    | 1    | Card B / 3.0 V              |

| 0      | Х    | Х    | A & B Disabled              |

### **Card Supply Converter**

The built—it NCN4557 DC/DC converters are Low Drop—Out Voltage Regulators capable to supply a current in excess of 50 mA under 1.8 V or 3.0 V. These voltages are selected according to Table 1. Using the Boolean input ENABLE pin the NCN4557 device can be disabled setting the circuit in a shutdown mode for which the power consumption features values typically in the range of a few tens of nA. Figure 9 shows a simplified view of the NCN4557 voltage regulator. The CRD\_V<sub>CC</sub> output is internally current limited and protected against short circuits. The short—circuit current IV<sub>CC</sub> varies with V<sub>BAT</sub> typically in the range of 30 mA to 60 mA.

In order to guarantee a stable and satisfying operating of the LDO the CRD\_V\_CC output will be connected to a 1.0  $\mu F$  bypass ceramic capacitor to the ground. At the input,  $V_{BAT}$  will be bypassed to the ground with a 0.1  $\mu F$  ceramic capacitor.

Figure 9. Simplified Block Diagram of the LDO Voltage Regulator

## **Level Shifters**

The level shifters accommodate the voltage difference

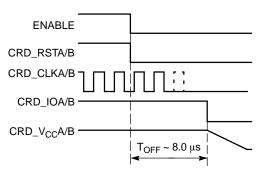

this state or  $8\,\mu s$  after the ENABLE pin is set LOW in the other cases.

- CRD\_I/O is forced to LOW about 8 μs after the ENABLE pin is set LOW.

- Then CRD\_V<sub>CC</sub> Supply Shuts Off

Figure 13. NCN4557 Power Down Sequence

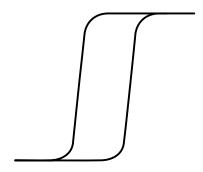

# **Input Schmitt Triggers**

All the logic input pins (excepted I/O and CRD\_I/O, Figure 3) have built—in Schmitt trigger circuits to prevent the NCN4557 against uncontrolled operation. The typical dynamic characteristics of the related pins are depicted in Figure 14.

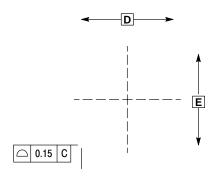

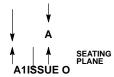

# **QFN16 3\*3\*0.75 MM**, **0.5 P** CASE 488AK ISSUE O

DATE 13 SEP 2004

# SCALE 2:1

L

16X