TSSOP-20 DTB SUFFIX CASE 948E

NCN6000DTB TSSOP-20\* 75 Units / Rail

- - - - -

-

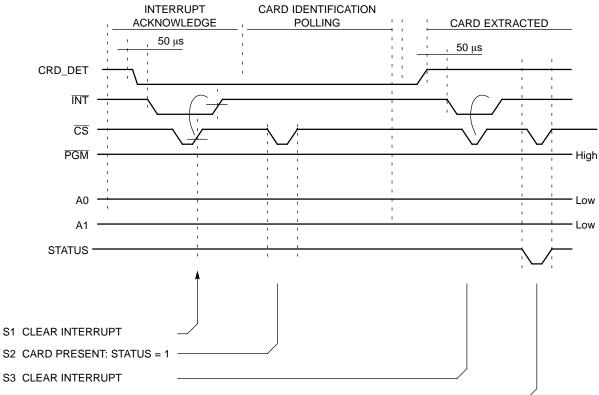

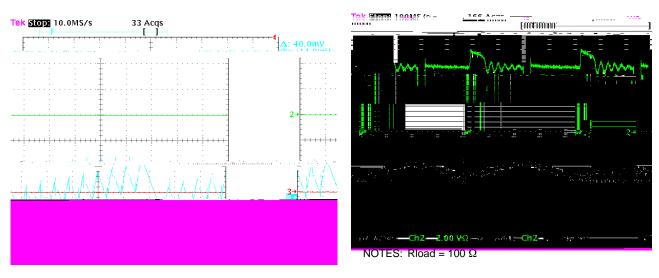

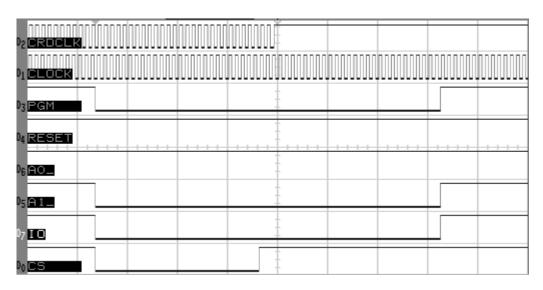

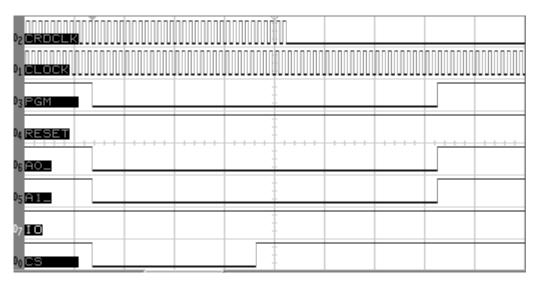

The programming can be achieved with the card powered ON or OFF. The identification of the interrupt is carried out by polling the STATUS pin, the Vbat voltage and the DC–DC results being provided on the same pin as depicted by the table in Figure 4. During the programming mode, the  $\overline{PGM}$  pin can be released to High since the mode is internally latched by the Negative going transition presents on the Chip Select pin.

S4 CARD PRESENT: STATUS = 0TURr1.6 m5 .620560.76 c2 2 595.2 T.51616 584..64 BT8 0 0 8 416.52 631.68 Tm(50 )Tj/F9 1 Tf1.395 0 452 631a.

#### ABBREVIATIONS

| Lout_H  | DC–DC External Inductor                              |

|---------|------------------------------------------------------|

| Lout_L  | DC–DC External Inductor                              |

| Cout    | Output Capacitor                                     |

| VCC     | Card Power Supply Input                              |

| lcc     | Current at CRD_VCC Pin                               |

| Class A | 5.0 V Smart Card                                     |

| Class B | 3.0 V Smart Card                                     |

| CS      | Chip Select (from MPU)                               |

| Z       | High Impedance Logic State<br>(according to ISO7816) |

| CRD_VCC | Interface IC Card Power Supply Output                |

| CRD_CLK | Interface IC Card Clock Output                       |

| CRD_RST | Interface IC Card ResN1kCRD_RST                      |

|         |                                                      |

## PIN FUNCTIONS AND DESCRIPTION (continued)

| Pin | Name | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | I/O  | Input/Output<br>Pull Up | This pin is connected to an external microcontroller interface. A bidirectional level translator adapts the serial I/O signal between the smart card and the microcontroller. The level translator is enabled when $\overline{CS} = L$ . The signal present on this pin is latched when $\overline{CS} = H$ . This pin is also used in programming mode (Tables 1, 2 and 3, Figures 4 and 5). |

| 9   | INT  | OUTPUT<br>Pull Down     | toTJT*0.014 69(Tha logic Tfo6 e mirisg moedg)f eie mrS                                                                                                                                                                                                                                                                                                                                        |

| POWER SUPPLY SECTION | (-25°C to +85°C ambient temperature | , unless otherwise noted.) |

|----------------------|-------------------------------------|----------------------------|

|----------------------|-------------------------------------|----------------------------|

| Rating                                                                                                                                               | Symbol             | Pin | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|-----|------|

| Power Supply                                                                                                                                         | Vbat               | 20  | 2.7 | -   | 6.0 | V    |

| Standby Supply Current Conditions:<br>$PWR_ON = L$ , STATUS = H, CLOCK_IN = H,<br>$\overline{CS} = H$ . All other logic inputs and outputs are open: | lbat <sub>sb</sub> | 20  |     |     |     | μΑ   |

| Vbat = 3.0 V                                                                                                                                         |                    |     | -   | 3.0 | 8.0 |      |

| Vbat = 5.0 V                                                                                                                                         |                    |     | -   | -   | 15  |      |

| DC Operating Current (Figure 19)<br>PWR_ON = H, CLOCK_IN = 0, CS = H, all CRD pins<br>unloaded                                                       | lbat <sub>op</sub> | 20  |     |     |     | mA   |

| @ Vbat = 6.0 V, CRD_VCC = 5.0 V                                                                                                                      |                    |     | -   | 7.0 | -   |      |

| @ Vbat = 3.6 V, CRD_VCC = 5.0 V                                                                                                                      |                    |     | -   | 2.0 | 5.0 |      |

| Vbat Undervoltage Detection <sub>High</sub>                                                                                                          | Vbat <sub>LH</sub> | 20  | 2.1 | -   | 2.7 | -    |

| Vbat Undervoltage DetectionLow                                                                                                                       | Vbat <sub>LL</sub> |     | 2.0 | -   | 2.6 |      |

| Vbat Undervoltage Detection <sub>Hysteresis</sub>                                                                                                    | Vbat <sub>HY</sub> |     | -   | 100 | -   |      |

# DIGITAL PARAMETERS SECTION @ 2.70 V ≤ Vbat ≤ 6.0 V, NORMAL OPERATING MODE (-25°C to +85°C ambient

temperature, unless otherwise noted.) Note: Digital inputs undershoot < -0.30 V to ground, Digital inputs overshoot <0.30 V to Vbat

| Rating                                                                                | Symbol                             | Pin | Min | Тур    | Max        | Unit |

|---------------------------------------------------------------------------------------|------------------------------------|-----|-----|--------|------------|------|

| Input Asynchronous Clock Duty Cycle = 50%<br>@ Vbat = 3.0V over the temperature range | F <sub>CLKIN</sub>                 | 10  | _   | _      | 40         | MHz  |

| 1œlock Rise Time<br>.0Clock Fall Time                                                 | F <sub>tr</sub><br>F <sub>tf</sub> | 10  |     | -<br>- | 5.0<br>5.0 | ns   |

I/O Data Transfer Switching Time,

SMART CARD SECTION (-25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                                           | Symbol              | Pin | Min           | Тур | Мах     | Unit |

|------------------------------------------------------------------|---------------------|-----|---------------|-----|---------|------|

| CRD RST @ CRD VCC = +5.0 V                                       |                     | 12  |               | -   |         |      |

| Output RESET $V_{OH}$ @ lcrd_rst = -20 $\mu$ A                   | V <sub>OH</sub>     |     | CRD_VCC - 0.9 |     | CRD_VCC | V    |

| Output RESET V <sub>OL</sub> @ Icrd_rst = 200 μA                 | VOL                 |     | 0             |     | 0.4     | V    |

| Output RESET Rise Time @ Cout = 30 pF                            | t <sub>R</sub>      |     |               |     | 100     | ns   |

| Output RESET Fall Time @ Cout = 30 pF                            | t <sub>F</sub>      |     |               |     | 100     | ns   |

| CRD_RST @ Vcc = +3.0 V                                           |                     |     |               |     |         |      |

| Output RESET V <sub>OH</sub> @ lcrd_rst = –20 μA                 | V <sub>OH</sub>     |     | CRD_VCC - 0.9 |     | CRD_VCC | V    |

| Output RESET V <sub>OL</sub> @ Icrd_rst = 200 μA                 | VOL                 |     | 0             |     | 0.4     | V    |

| Output RESET Rise Time @ Cout = 30 pF                            | t <sub>R</sub>      |     |               |     | 100     | ns   |

| Output RESET Fall Time @ Cout = 30 pF                            | t <sub>F</sub>      |     |               |     | 100     | ns   |

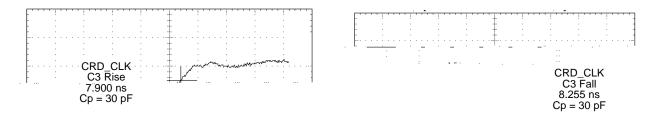

| CRD_CLK @ CRD_VCC = +3.0 V or +5.0 V                             |                     | 13  |               | -   |         |      |

| CRD VCC = +5.0 V                                                 |                     |     |               |     |         |      |

| Output Frequency (See Note 8)                                    | F <sub>CRDCLK</sub> |     |               |     | 5.0     | MHz  |

| Output Duty Cycle @ DC Fin = $50\% \pm 1\%$                      | FCRDDC              |     | 45            |     | 55      | %    |

| Output CRD_CLK Rise Time @ Cout = 30 pF                          | t <sub>R</sub>      |     |               |     | 18      | ns   |

| Output CRD_CLK Fall Time @ Cout = 30 pF                          | t <sub>F</sub>      |     |               |     | 18      | ns   |

| Output V <sub>OH</sub> @ Icrd_clk = –20 μA                       | V <sub>OH</sub>     |     | 3.15          |     | CRD_VCC | V    |

| Output V <sub>OL</sub> @ Icrd_clk = 100 μA                       | V <sub>OL</sub>     |     | 0             |     | +0.5    | V    |

| CRD_VCC = +3.0 V                                                 |                     |     |               |     |         |      |

| Output Frequency (See Note 8)                                    | F <sub>CRDCLK</sub> |     |               |     | 5.0     | MHz  |

| Output Duty Cycle @ DC Fin = $50\% \pm 1\%$                      | F <sub>CRDDC</sub>  |     | 40            |     | 60      | %    |

| Output CRD_CLK Rise Time @ Cout = 30 pF                          | t <sub>R</sub>      |     |               |     | 18      | ns   |

| Output CRD_CLK Fall Time @ Cout = 30 pF                          | t <sub>F</sub>      |     |               |     | 18      | ns   |

| Output V <sub>OH</sub> @ Icrd_clk = $-20 \ \mu A$ @ Cout = 30 pF | V <sub>OH</sub>     |     | 1.85          |     | CRD_VCC | V    |

| Output $V_{OL}$ @ Icrd_clk = 100 $\mu$ A @ Cout = 30 pF          | V <sub>OL</sub>     |     | 0             |     | 0.7     | V    |

$\begin{array}{ll} \mbox{CRD\_I/O} @ \mbox{CRD\_VCC} = +5.0 \ V \\ \mbox{CRD\_I/O} \ Data \ Transfer \ Frequency \\ \mbox{CRD\_I/O} \ Data \ Transfer \ Frequency \\ \mbox{CRD\_I/O} \ Rise \ Time \ @ \ Cout = 30 \ pF \\ \mbox{CRD\_I/O} \ Fall \ Time \ @ \ Cout = 30 \ pF \\ \mbox{Output } V_{OH} \ @ \ Icrd\_i/o = -20 \ \mu A \\ \mbox{Output } V_{OL} \ @ \ Icrd\_i/o = 500 \ \ \mu A, \ V_{IL} = 0 \ V \end{array}$

$\begin{array}{ll} \mbox{CRD\_I/O} @ \mbox{CRD\_VCC} = +3.0 \ V \\ \mbox{CRD\_I/O} \ Data \ Transfer \ Frequency \\ \mbox{CRD\_I/O} \ Data \ Transfer \ Frequency \\ \mbox{CRD\_I/O} \ Rise \ Time \ @ \ Cout = 30 \ pF \\ \mbox{CRD\_I/O} \ Fall \ Time \ @ \ Cout = 30 \ pF \\ \mbox{Output } V_{OH} \ @ \ Icrd\_i/o = -20 \ \mu A \\ \mbox{Output } V_{OL} \ @ \ Icrd\_i/o = 500 \ \mu A, \ V_{IL} = 0 \ V \end{array}$

## **Programming and Status Functions**

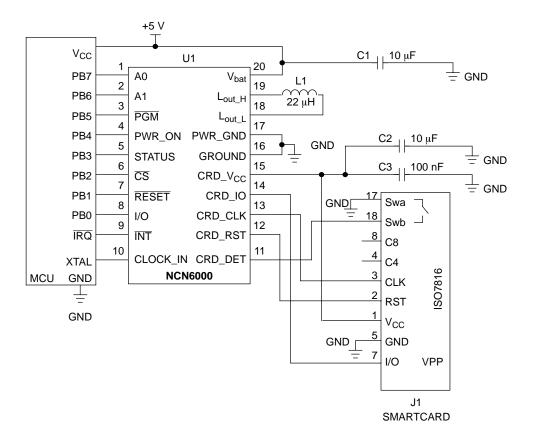

The NCN6000 features a programming interface and a status interface. Figure 4 illustrates the programming mode.

Table 1. Programming and Status Functions Pinout Logic

| Pins | Name   | CRD_VCC<br>Prg. 3.0 V/5.0 V | CLOCK_IN<br>Divide Ratio | CRD_DET                 | CLOCK STOP<br>AND START | Poll Card<br>Status | DC-DC<br>Status | Vbat<br>Status | CRD_VCC<br>Status |

|------|--------|-----------------------------|--------------------------|-------------------------|-------------------------|---------------------|-----------------|----------------|-------------------|

| 5    | STATUS | Not Affected                | Not Affected             | Not Affected            | Not Affected            | READ                | READ            | READ           | READ              |

| 6    | CS     | Latch On<br>Rising Edge     | Latch On<br>Rising Edge  | Latch On<br>Rising Edge | Latch On<br>Rising Edge | 0                   | 0               | 0              | 0                 |

| 3    | PGM    | 0                           | 0                        | 0                       | 0                       | 1                   | 1               | 1              | 1                 |

# Card VCC, Card CLOCK and Card Detection Polarity Programming

The CRD\_VCC and CLOCK\_IN programming options allows matching the system frequency with the card clock frequency, and to select 3.0 V or 5.0 V CRD\_VCC supply. The CRD\_DET programming option allows the usage of either Normally Open or Normally Close detection switch. Table 3 highlights the A0, A1, PGM and I/O logic states for the possible options. **The default power up reset condition**  is state 1: asynchronous clock, ratio 1/1, CRD\_CLK active, CRD\_DET = Normally Open, CRD\_VCC = 3.0 V. All states are latched for each output variable in programming mode at the positive going slope of Chip Select [ $\overline{CS}$ ] signal. It is the system designer's responsibility to set up the options needed to match the chip with the peripherals. In particular, when using Normally Close switch, the CRD\_DET polarity must s9he A0,

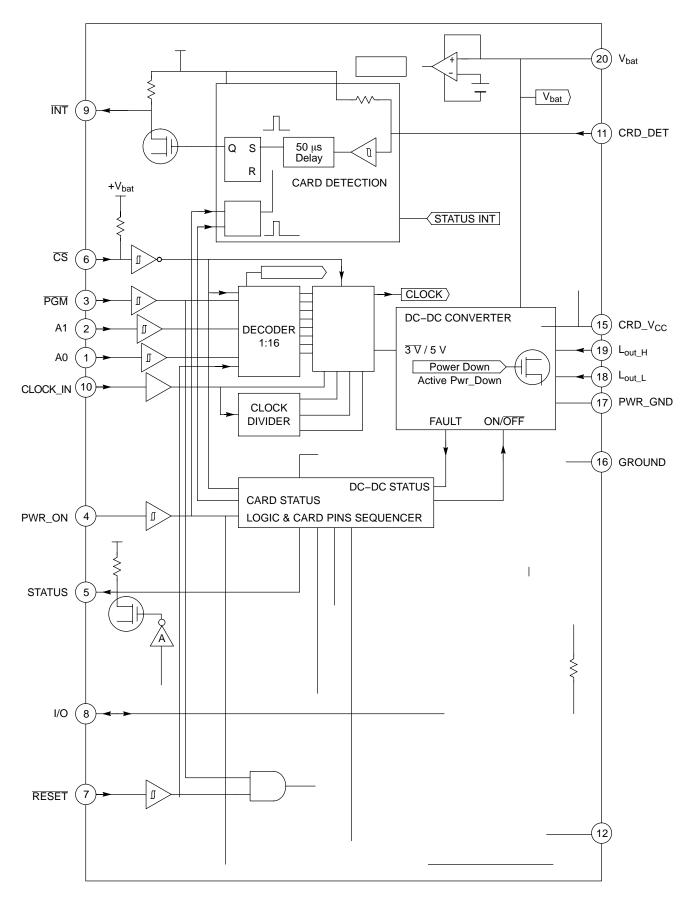

#### **DC–DC Converter and Card Detector Status**

The NCN6000 status can be polled when  $\overline{CS} = L$ . Please consult Figures 4 and 5 for a description of input and output signals. The status message is described in Table 4.

Note: in order to cope with a start up under low battery condition, the Vbat OK message uses a negative logic as depicted here below.

| PGM  | A1 | A0 | STATUS | Message                       |

|------|----|----|--------|-------------------------------|

| HIGH | L  | L  | LOW    | No Card                       |

| HIGH | L  | L  | HIGH   | Card Present                  |

| HIGH | L  | Н  | LOW    | DC–DC Converter<br>Overloaded |

| HIGH | L  | Н  | HIGH   | DC–DC Converter OK            |

| HIGH | Н  | L  | LOW    | Vbat OK                       |

| HIGH | Н  | L  | HIGH   | Vbat Undervoltage             |

|      |    |    |        |                               |

HIGH

LOW

CRD\_VCC OK

CRD\_VCC Undervoltage

#### Table 4. Card and DC-DC Status Output

HIGH

HIGH

Н

н

н

н

The STATUS pin provides a feedback related to the detection of the card, the state of the DC–DC converter, the Vbat undervoltage and CRD\_VCC undervoltage situations. When  $\overline{PGM} = H$ , the STATUS pin returns a High if a card is

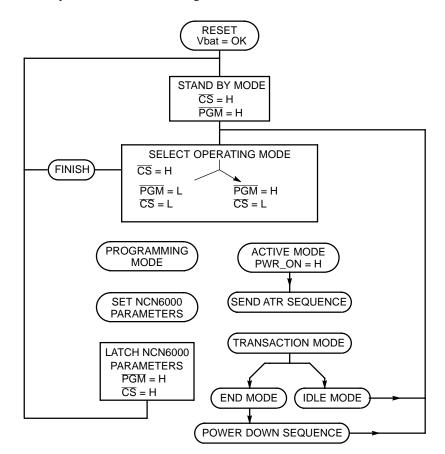

#### **Basic Operating Modes Flow Chart**

The NCN6000 brings all the functions necessary to handle data communication between a host computer and the smart card. The built–in Chip Select pin provides a simple way to share the same MPU bus with several card interface. On top of that, the logic control are derived from specific pins, avoiding the risk of mixing up the operation when the interface is controlled by a low end microcontroller.

During the transaction operation, the external MPU takes care of whatever is necessary to he data on the single bidirectional I/O line. Leaving aside the DC–DC control and associated failures, the NCN6000 does not take any further responsibility in the data transaction.

When the chip operates in the programming mode, the NCN6000 provide a flexible access to set up the CRD\_VCC voltage, the CRD\_CLK and the CRD\_DET smart card signals.

The external microcontroller takes care of the smart card transaction and shall handle the interface accordingly.

Figure 7. Operating Modes Flow Chart

#### **Programming Mode**

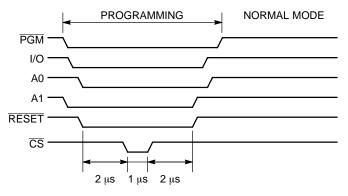

The programming mode allows the configuration of the card power supply, card clock and Card Detection input logic polarity. These signals (CRD\_VCC, CRD\_CLK and CRD\_DET) are described in the pin description paragraph associated with Tables 1 and 3 and Figures 4 and 8.

| Programming N<br>Logic Conditior                                                                                                                                                                                                                                       |                                                       |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|

| $\begin{array}{ll} \overline{\text{CS}} &= \text{L} \\ \text{PWR}_{\text{ON}} &= \text{L} \\ \text{A0} &= \text{H/L} \\ \text{A1} &= \text{H/L} \\ \overline{\text{PGM}} &= \text{L} \\ \text{I/O} &= \text{L/H} \\ \overline{\text{RESET}} &= \text{L/H} \end{array}$ | CRD_IO = H/L dependi<br>the previous<br>l logic state | • • |

The I/O and  $\overline{\text{RESET}}$  pins are not connected to the smart card and become logic inputs to control the NCN6000 programming sequence. The programmed values are latched upon transition of  $\overline{\text{CS}}$  from Low to High,  $\overline{\text{PGM}}$  being Low during the transition.

When a programming mode is validated by a Chip Select negative going transient, the mode is latched and  $\overline{PGM}$  can be released to High. This latch is automatically reset when  $\overline{CS}$  returns to High.

The logic input signals can be set simultaneously, or one bit a time (using either a STAA or a BSET function), the key point being the minimum delay between the shorter bit and the Chip Select pulse. The programmed value is latched into the NCN6000 register on the  $\overline{CS}$  positive going edge.

Figure 8. Minimum Programming Timings

#### Active Mode

In the active mode, the NCN6000 is selected by the external MPU and the STATUS pin can be polled to get the status of either the DC–DC converter or the presence of the card (inserted or not valid). The power is not connected to the card:  $CRD_VCC = 0$  V.

| Active Mode<br>Logic Conditions:                                                                                                                                                                  | Card Output:                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{ll} \overline{CS} &= L \\ PWR_ON &= L \\ A0 &= L \\ A1 &= L \\ \overline{PGM} &= H \\ I/O &= Z \\ \overline{RESET} &= Z \\ STATUS &= L/H \text{ is Card} \\ Inserted? \end{array}$ | CRD_VCC = 0 V<br>CRD_CLK = L<br>CRD_RST = L<br>CRD_IO = H/L depending upon<br>the previous I/O pin<br>logic state |

The Chip Select pulse  $[\overline{CS}]$  will automatically clear the previously asserted  $\overline{INT}$  signal upon the positive going transition.

If a card is present, the MPU shall activate the DC–DC converter by asserting PWR\_ON = H. The NCN6000 will automatically run a power up sequence when the CRD\_VCC reaches the undervoltage level (either  $V_{C5H}$  or  $V_{C3H}$ , depending upon the CRD\_VCC voltage supply programmed). The CRD\_IO, CRD\_RST and CRD\_CLK pins are validated, according to the ISO7816–3 sequence. The interface is now in transaction mode and the system is ready for data exchange through the I/O and RESET lines. At any time, the microcontroller can change the CRD\_CLK frequency and mode, or the CRD\_VCC value as determined by the card being in use.

#### **Transaction Mode**

During the transaction mode, the NCN6000 maintains power supply and clock signal to the card. All the signal levels related with the card are translated as necessary to cope with the MPU and the card.

The DC–DC converter status and the Vbat state can be monitored on the STATUS by using the A0 and A1 logic inputs as depicted in Tables 3 and 4.

| Transactio |                                   | Card Output:                              |

|------------|-----------------------------------|-------------------------------------------|

|            | = L                               | $CRD_VCC = 3.0 \text{ or } 5.0 \text{ V}$ |

| PWR_ON     |                                   | CRD_CLK = CLOCK                           |

| A0         | = H                               | $CRD_RST = H/L$                           |

| A1         | = H                               | CRD_IO = DATA                             |

| PGM        | = H                               | TRANSFER                                  |

| I/O        | = DATA                            |                                           |

|            | TRANSFER                          |                                           |

| RESET      | = H/L                             |                                           |

| STATUS     | = L/H DC–DC<br>status: Fail/Pass? |                                           |

To make sure the data are not polluted by power losses, it

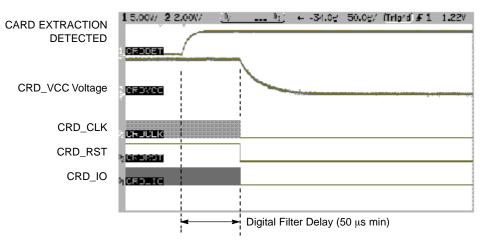

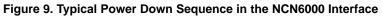

Figure 10. Power Down Sequence Details

#### **Card Detection**

The card detector circuit provides a 500 k $\Omega$  pull up resistor to bias the CRD\_DET pin, yielding a logic High when the pin is left open (assuming a NO switch). The internal logic associated with pin 11 provides an automatic selection of the slope card detection, depending upon the polarity set by the external MPU. At start up, the CRD\_DET is preset to cope with Normally Open switch. When a Normally Close switch is used in the card socket, it is mandatory to program the NCN6000 chip during the initialization sequence, otherwise the system will not start if a card was previously inserted. Table 3 gives the programming code for such a function. The next lines provide a typical assembler source to handle this CRD\_DET

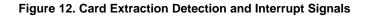

When the card is extracted, the CRD\_DET signal generates an interrupt, assuming the positive pulse width is longer than the digital filter. The oscillogram, Figure 12, depicts the behavior for a Normally Open switch.

Note: since the internal pull up resistor is relatively high (500 k $\Omega$  typical), one must use a 10 M $\Omega$  input impedance probe to read this signal.

The interrupt signal, provided pin 9, is cleared by a positive going Chip Select signal as depicted by the oscillogram, Figure 13. The  $\overline{CS}$  pulse width is irrelevant, as long as it is larger than 2.0  $\mu$ s, to activate a different sequence. Leaving the interrupt signal Low has no influence

on the internal behavior of the NCN6000, but will be automatically cleared when the DC–DC will be activated by the MPU ( $\overline{CS}$ =L, PWR\_ON = Positive High transition)

#### **Power Management**

The purpose of the power management is to activate the circuit functions needed to run a given mode of operation, yielding a minimum current consumption on the Vbat supply. In the Standby mode (PWR\_ON = L), the power management provides energy to the card detection circuit only. All the card interface pins are forced to ground potential.

In the event of a power up request coming from the external MPU (PWR\_ON = H,  $\overline{CS}$  = L), the power manager starts the DC–DC converter.

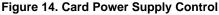

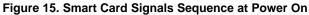

When the CRD\_VCC voltage reaches the programmed value (3.0 V or 5.0 V), the circuit activates the card signals according to the following sequence:

$\begin{array}{l} CRD\_VCC \\ \Rightarrow CRD\_IO \\ \Rightarrow CRD\_CLK \\ \Rightarrow CRD\_RST \end{array}$

The logic level of the data lines are asserted High or Low, depending upon the state forced by the external MPU, when the start up sequence is completed. Under no situation the NCN6000 shall launch automatically a smart card ATR sequence. Assuming PWR\_ON = H, the CRD\_VCC voltage is maintained whatever be the logic level presents on Chip Select, pin 6.

At the end of the transaction, asserted by the MPU (PWR\_ON = L,  $\overline{CS}$  = L), or under a card extraction, the ISO7816–3 power down sequence takes place:

$$\begin{array}{l} CRD\_RST \\ \Rightarrow CRD\_CLK \\ \Rightarrow CRD\_IO \\ \Rightarrow CRD\_VCC \end{array}$$

When  $\overline{\text{CS}} = \text{H}$ , the bi-directional I/O line (pins 8 and 15) is forced into the High impedance mode to avoid signal collision with any data coming from the external MPU.

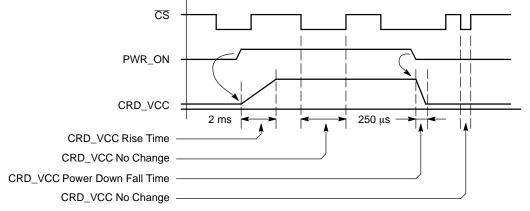

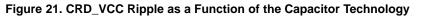

The CRD\_VCC voltage is controlled by means of  $\overline{CS}$  and PWR\_ON logic signal as depicted in Figure 14. The PWR\_ON logic level define the CRD\_VCC voltage status, the amplitude being the one pre programmed into the chip.

In order to avoid uncontrolled command applied to the smart card, the NCN6000 internal logic circuit, together with the Vbat monitoring, clamps the card outputs until the CRD\_VCC voltage reaches the minimum value. During the CRD\_VCC slope, all the card outputs are kept Low and no spikes can be write to the smart card. The oscillogram on the right hand side is a magnification of the curves given on the opposite side.

## Vbat Supply Voltage Monitoring

The built–in comparator, associated with the band gap reference, continuously monitors the +Vbat input. During the start up, all the NCN6000 functions are deactivated and

When the input voltage Vbat is lower than the programmed CRD\_VCC, the system operates under the boost mode, providing the voltage regulation and current

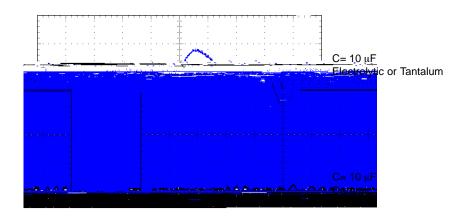

Based on the experiments carried out during the NCN6000 characterization, the best comprise, at time of printing this document, is to use two 6.8  $\mu$ F/10 V/Ceramic/X7R capacitor in parallel to achieve the CRD\_VCC filtering. The ESR will not extend 50 m $\Omega$  over the temperature range and the combination of standard parts provide an acceptable –20% to +20% tolerance,

Table 5. Ceramic/Electrolytic Capacitors Comparison

together with a low cost. Obviously, the capacitor must be SMD type to achieve the extremely low ESR and ESL necessary for this application. Figure 21 illustrates the CRD\_VCC ripple observed in the NCN6000 demo board depending upon the type of capacitor used to filter the output voltage.

| Manufacturers | Type/Series           | Format | Max Value   | Tolerance | Typ. Z @ 500 kHz     |

|---------------|-----------------------|--------|-------------|-----------|----------------------|

| MURATA        | CERAMIC/GRM225        | 0805   | 10 μF/6.3 V | +80%/-20% | $30 \text{ m}\Omega$ |

| VISHAY        | Tantalum/594C/593C    |        | 10 μF/16 V  |           | 450 mΩ               |

| VISHAY        | Electrolytic/94SV     |        | 10 μF/10 V  | -20%/+20% | 400 mΩ               |

|               | Electrolytic Low Cost |        | 10 μF/10 V  | -35%/+50% | 2.0 Ω                |

Top Trace = Electrolytic or Tantalum 10  $\mu$ F Bottom Trace = X7R 10  $\mu$ F ceramic The high ripple pulse across CRD\_VCC is the consequence of the large ESR of the electrolytic capacitor.

#### **Clock Divider**

The main purpose of the built-in clock generator is threefold:

- 1. Adapts the voltage level shifter to cope with the different voltages that might exist between the MPU and the Smart Card.

- 2. Provides a frequency division to adapt the Smart Card operating frequency from the external clock source.

- 3. Controls the clock state according to the smart card specification.

In addition, the NCN6000 adjusts the signal coming from the microprocessor to get the Duty Cycle window as defined by the ISO7816–3 specification.

The logic input pins A0, A1,  $\overline{PGM}$ , I/O and  $\overline{RESET}$  fulfill the programming functions when both  $\overline{PGM}$  and  $\overline{CS}$  are

Low. The clock input stage (CLOCK\_IN) can handle a 40 MHz frequency maximum, the divider being capable to provide a 1:8 ratio. Of course, the ratio must be defined by the engineer to cope with the Smart Card considered in a

The example given by the oscillogram here above highlights the delay coming from the internal clock duty cycle resynchronization. In this example, the clock is internally divided by 2 prior to be applied to the CRD\_CLK pin. Since the clock signal is asynchronous, it is up to the programmer to make sure the next card transaction is not activated before the CRD\_CLK signal has been updated. Generally speaking, such a delay can be derived from the maximum clock frequency provided to the interface, keeping in mind the maximum delay is eight incoming clock pulses.

Figure 25. Clock Programming Examples

The clock can be re-programmed without halting the rest of the circuit, whatever be the new clock divider ratio. In

particular, the CRD\_VCC can be applied to the card while the clock is re–programmed.

Figure 26. Command Stop Clock HIGH

The CRD\_CLK signal is halted in the High logic state, following the Chip Select positive going transition. Logic Input conditions:

$\begin{array}{ll} A0 & = Low \\ A1 & = Low \\ \overline{CS} & = Low \mbox{ pulsed} \end{array}$

Figure 27. Command Stop Clock LOW

The CRD\_CLK signal is halted in the Low logic state, following the Chip Select positive going transition. Logic Input conditions:

| PGM   | =Low   | A |

|-------|--------|---|

| RESET | =Low   | A |

| I/O   | = High | Ō |

A0 = LowA1 = Low

$\overline{CS} = Low, pulsed$

#### Figure 28. Command Resume Clock Normal Operation

The CRD\_CLK signal is resumed in the normal operation, following the Chip Select positive going transition. The previous halted state is irrelevant and the clock signal is synchronized with the internal clock divider to avoid non CRD\_CLK 50% duty cycle.

| PGM   | = Low  | A0 | = Low         |

|-------|--------|----|---------------|

| RESET | = High | A1 | = Low         |

| I/O   | = Low  | CS | = Low, pulsed |

#### Figure 29. Card Clock Rise and Fall Time

Since the CRD\_CLK signal can generate very fast transient (i.e. tr = 2.5 ns @ Cp = 10 pF), adapting the design to cope with the EMV noise specification might be necessary at final check out. Using an external RC network is a way to reduce the dv/dt, hence the EMI noise.

Typically, the external series resistor is 10  $\Omega$ , the total capacitance being 30 pF to 50 pF

Input Schmitt Triggers

# Printed Circuit Board Layout

Since the NCN6000 carries high speed currents together with

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7 XIRQ

TSSOP-20 WB CASE 948E ISSUE D

DATE 17 FEB 2016

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi