# e '

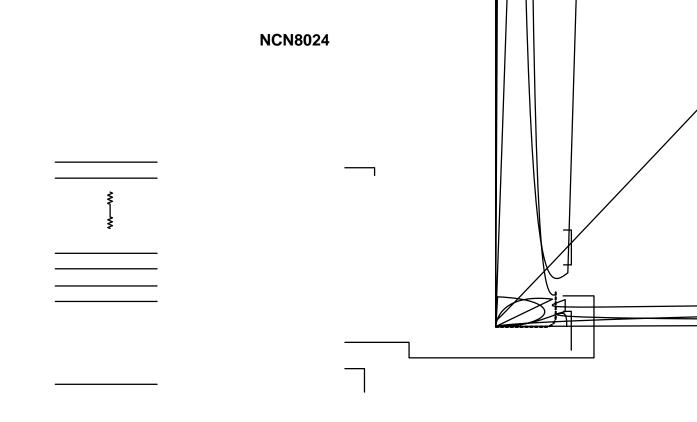

Figure 1. Typical Smart Card Interface Application

## PIN FUNCTION AND DESCRIPTION

| Pin # | Name     | Туре             | Description                                                                                                                                                                                                                                                                                                                   |

|-------|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11    | CRD_I/O  | Input/<br>Output | This pin handles the connection to the serial I/O (C7) of the card connector. A bi directional level translator adapts the serial I/O signal between the card and the micro controller. An 11 k $\Omega$ (typical) pullup resistor to CRD_V <sub>CC</sub> provides a High impedance state for the smart card I/O link.        |

| 12    | CRD_AUX2 | Input/<br>Output | This pin handles the connection to the chip card's serial auxiliary AUX2 I/O pin (C8). A bi directional level translator adapts the serial I/O signal between the card and the micro controller. An 11 k $\Omega$ (typical) pullup resistor to CRD_V <sub>CC</sub> provides a High impedance state for the smart card C8 pin. |

| 13    | CRD_AUX1 | Input/<br>Output | This pin handles the connection to the chip card's serial auxiliary AUX1 I/O pin (C4). A bi directional level translator adapts the serial I/O signal between the card and the micro controller. An 11 k $\Omega$ (typical) pullup resistor to CRD_V <sub>CC</sub> provides a High impedance state for the smart card C4 pin. |

| 14    | CRD_GND  | GND              | Card Ground                                                                                                                                                                                                                                                                                                                   |

| 15    | CRD_CLK  | Output           | This pin is connected to the CLOCK card connector's pin (Chip card's pin C3). The Clock signal comes from the CLKIN input through clock dividers and level shifter.                                                                                                                                                           |

| 16    | CRD_RST  | Output           | This pin is connected to the chip card's RESET pin (C2) through the card connector. A level translator adapts the external Reset (RSTIN) signal to the smart card.                                                                                                                                                            |

| 17    | CRD_VCC  | Power            | This pin is connected to the smart card power supply pin. An internal DC/DC converter is programmable using the pin $5V/3V$ to supply either 5 V or 3 V output voltage. An external distributed                                                                                                                               |

#### **ATTRIBUTES**

| Characteristics                                                                                                                                                                             | Values                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| ESD protection<br>Human Body Model (HBM) (Note 1)<br>Card Pins (Card Interface Pins 9 17)<br>All Other Pins<br>Machine Model (MM)<br>Card Pins (Card Interface Pins 9 17)<br>All Other Pins | 8 kV<br>2 kV<br>400 V<br>150 V |

| Moisture sensitivity (Note 2) SOIC 28 and TSSOP 28                                                                                                                                          | Level 3                        |

| Flammability Rating Oxygen Index: 28 to 34                                                                                                                                                  | UL 94 V 0 @ 0.125 in           |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch up Test                                                                                                                                     | •                              |

Human Body Model (HBM), R = 1500 Ω, C = 100 pF.

For additional information, see Application Note AND8003/D.

## MAXIMUM RATINGS (Note 3)

| Rating                                 | Symbol           | Value                        | Unit |

|----------------------------------------|------------------|------------------------------|------|

| DC/DC Converter Power Supply Voltage   | V <sub>DDP</sub> | $0.3 \le V_{DDP} \le 5.5$    | V    |

| Power Supply from Microcontroller Side | V <sub>DD</sub>  | $0.3 \le V_{DD} \le 5.5$     | V    |

| External Card Power Supply             | $CRD_V_{CC}$     | $0.3 \le CRD_V_{CC} \le 5.5$ | V    |

| Charge Pump Output                     | V <sub>UP</sub>  | $0.3 \le V_{UP} \le 5.5$     |      |

| Digital Input Pins                     | V                |                              | -    |

## **POWER SUPPLY SECTION** ( $V_{DD}$ = 3.3 V; $V_{DDP}$ = 5 V; $T_{amb}$ = 25 C; $F_{CLKIN}$ = 10 MHz)

| Pin | Symbol | Rating | Min | Тур |

|-----|--------|--------|-----|-----|

|     | •      | •      |     |     |

| Pin  | Symbol                  | Rating                                                                                                                                                                                                                                                                                   | Min          | Тур          | Max          | Unit   |

|------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------|

| C/DC | CONVERTER               |                                                                                                                                                                                                                                                                                          |              |              |              |        |

| 17   | CRD_V <sub>CC</sub>     | $ \begin{array}{l} \mbox{Output Card Supply Voltage @ 3.6 V \leq V_{DDP} \leq 5.5 V \mbox{ with }  I_{CC}  \leq 65 \mbox{ mA load transient from 100 Hz to 200 MHz (including ripple)} \\ \mbox{(Note 4)} \\ \mbox{CRD}_V_{CC} = 3.0 \ V \\ \mbox{CRD}_V_{CC} = 5.0 \ V \\ \end{array} $ | 2.76<br>4.65 | 3.00<br>5.00 | 3.20<br>5.25 | V<br>V |

| 17   | CRD_V <sub>CC</sub>     | Output Card Supply Voltage @ $4.5 \text{ V} < \text{V}_{\text{DDP}} < 5.5 \text{ V}$ with Current<br>Load Pulses of 40 nAs/t < 400 ns and $ I_{CC}  < 200 \text{ mA Peak Current}$<br>(Including Ripple) (Note 4)<br>$CRD_V_{CC} = 3.0 \text{ V}$<br>$CRD_V_{CC} = 5.0 \text{ V}$        | 2.76<br>4.65 | 3.00<br>5.00 | 3.20<br>5.25 | V<br>V |

| 17   | ICRD_VCC                | Card Supply Current<br>@ CRD_V <sub>CC</sub> = 3.0 V<br>@ CRD_V <sub>CC</sub> = 5.0 V                                                                                                                                                                                                    |              |              | 75<br>75     | mA     |

| 17   | I <sub>CRD_VCC_SC</sub> | Short Circuit Current CRD_V <sub>CC</sub> Shorted to Ground                                                                                                                                                                                                                              |              | 110          | 150          | mA     |

| 17   | $\Delta V_{CRD_VCC}$    | Output Card Supply Voltage Ripple Peak to Peak $f_{ripple} = 100 \text{ Hz to}$                                                                                                                                                                                                          |              | -            | -            | -      |

# **POWER SUPPLY SECTION** (V<sub>DD</sub> = 3.3 V; V<sub>DDP</sub> = 5 V; T<sub>amb</sub> = 25 C; F<sub>CLKIN</sub> = 10 MHz)

| Pin        | Symbol             | Rating                                                                                                                                                                                                                                     | Min                                             | Тур | Мах                                            | Unit   |

|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|------------------------------------------------|--------|

| 26, 27, 28 | V <sub>OH</sub>    | $\begin{array}{ll} \mbox{I/Ouc, AUX1uc, AUX2uc data channels, } @ Cs \leq 30 \ \mbox{pF} \\ \mbox{High Level Output Voltage (CRD_I/O = CRD_AUX1 = CRD_AUX2 = CRD_V_{CC}) & I_{OH} = 0 \\ I_{OH} = \ \ \mbox{40 } \mu \mbox{A} \end{array}$ | 0.9 x V <sub>DD</sub><br>0.75 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.1<br>V <sub>DD</sub> + 0.1 | V<br>V |

|            | V <sub>OL</sub>    | Low Level Output Voltage (C_I/O= CRD_AUX1 = CRD_AUX2 = 0 V)<br>$I_{OL}$ = +1 mA                                                                                                                                                            | 0                                               |     | 0.3                                            | v      |

|            | t <sub>Ri/Fi</sub> | Input Rising/Falling Times (Note 6)                                                                                                                                                                                                        |                                                 |     | 1.2                                            | μs     |

|            | t <sub>Ro/Fo</sub> | Output Rising/Falling Times (Note 6)                                                                                                                                                                                                       |                                                 |     | 0.1                                            | μS     |

| 26, 27, 28 | F <sub>bidi</sub>  | Maximum Frequency through Bidirectional I/O, AUX1 and AUX2<br>Channels (Note 6)                                                                                                                                                            |                                                 |     | 1                                              | MHz    |

| 26, 27, 28 | R <sub>pu</sub>    | I/0uc, AUX1uc, AUX2uc Pullup Resistor                                                                                                                                                                                                      | 8.0                                             | 11  | 16                                             | kΩ     |

| 23         | V <sub>OH</sub>    | Output High Voltage<br>INT @ I <sub>OH</sub> = 15 μA (Source)                                                                                                                                                                              | 0.75 x V <sub>DD</sub>                          |     |                                                | V      |

| 23         | V <sub>OL</sub>    | Output Low Voltage<br>INT @ I <sub>OL</sub> = 2 mA (Sink)                                                                                                                                                                                  | 0                                               |     | 0.30                                           | V      |

| 23         | R <sub>INT</sub>   | INT Pullup Resistor                                                                                                                                                                                                                        | 14                                              | 20  | 26                                             | kΩ     |

DIGITAL INPUT/OUTPUT SECTION CLKIN, RSTIN, I/Ouc, AUX1uc, AUX2uc, CLKDIV1, CLKDIV2,  $\overline{CMDVCC}$ ,  $5V/\overline{3V}$ (V<sub>DD</sub> = 3.3 V; V<sub>DDP</sub> = 5 V; T<sub>amb</sub> = 25 C; F<sub>CLKIN</sub> = 10 MHz)

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

6. Guaranteed by design and characterization

| Pin               | Symbol                                | Rating                                                                                                                                                                                                | Min | Тур | Max                | Unit |

|-------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------|

| 9, 10             | 1 <sub>14</sub>  <br> 1 <sub>16</sub> | CRD_PRES, $\overline{CRD_PRES}$<br>High level input leakage current, $V_{IH} = V_{DD}$<br>CRD_PRES<br>CRD_PRES<br>Low level input leakage current, $V_{IL} = 0 V$<br>CRD_PRES<br>CRD_PRES<br>CRD_PRES |     | 5   | 10<br>1<br>1<br>10 | μΑ   |

| 9, 10             | T <sub>debounce</sub>                 | Debounce Time CRD_PRES and CRD_PRES (Note 7)                                                                                                                                                          | 5   | 8   | 11                 | ms   |

| 11, 12,<br>13, 16 | I <sub>CRD_IO</sub>                   | CRD_IO, CRD_AUX1, CRD_AUX2 Current Limitation                                                                                                                                                         |     |     | 15                 | mA   |

| 15                | I <sub>CRD_CLK</sub>                  | CRD_CLK Current Limitation                                                                                                                                                                            |     |     | 70                 | mA   |

| 16                | I <sub>CRD_RST</sub>                  | CRD_RST Current Limitation                                                                                                                                                                            |     |     | 20                 | mA   |

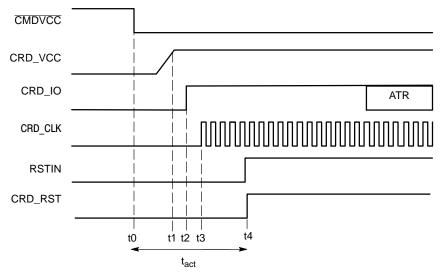

|                   | t <sub>act</sub>                      | Activation Time (Note 7)                                                                                                                                                                              | 30  |     | 100                | μs   |

|                   | t <sub>deact</sub>                    | Deactivation Time (Note 7)                                                                                                                                                                            | 30  |     | 250                | μs   |

|                   | Temp <sub>SD</sub>                    | Shutdown Temperature                                                                                                                                                                                  |     | 160 |                    | С    |

| SMART CARD INTERFACE SECTION, CRD_IO, CRD_AUX1, CRD_AUX2, CRD_CLK, CRD_RST,                                             | CRD_PRES, |

|-------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>CRD_PRES</b> (V <sub>DD</sub> = 3.3 V; V <sub>DDP</sub> = 5 V; T <sub>amb</sub> = 25 C; F <sub>CLKIN</sub> = 10 MHz) |           |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

7. Guaranteed by design and characterization

## POWER SUPPLY

The NCN8024 smart card interface has two power supplies:  $V_{DD}$  and  $V_{DDP}$ .

$V_{DD}$  is usually common to the system controller and the interface. The applied  $V_{DD}$  ranges from 2.7 V up to 5.5 V. If  $V_{DD}$  goes below 2.35 V typical (UVLO<sub>VDD</sub>) a power down sequence is automatically performed. In that case the interrupt ( $\overline{INT}$ ) pin is set Low.

A built in charge pump based DC/DC converter followed by a Low Drop Out (LDO) regulator is used to provide the 3 V or 5 V power supply voltage (CRD\_V<sub>CC</sub>) to the card. V<sub>DDP</sub> is the converter's input voltage. VUP is the charge pump converter's output. It is connected to the LDO input. A reservoir capacitor of 100 nF is connected to VUP. CRD  $V_{CC}$  is the LDO output. Even if the converter can operate with a single output reservoir capacitor as low as 100 nF at CRD\_V<sub>CC</sub>, it is recommended to use a capacitor of at least 320 nF in order to satisfy the datasheet specifications. The best recommended combination guaranteeing optimal performances consists in a distributed set of capacitors 220 nF + 330 nF (in particular recommended for optimally satisfying the NDS standard). To minimize dI/dt effects, the fly capacitor (100 nF) and the reservoir capacitors VUP and CRD\_V<sub>CC</sub> have to be connected as close as possible to the corresponding device's pin and feature very low ESR values (lower than 50 m $\Omega$ ). The fly capacitor is connected between C1 and C2. The decoupling capacitors on V<sub>DD</sub> and V<sub>DDP</sub> respectively 100 nF and 10  $\mu$ F have also to be connected close to the respective IC pins.

The CRD\_VCC pin can source up to 75 mA continuously over the  $V_{DDP}$  range (from 3.3 V to 5.5 V), the absondr combination1 5098966 35fBT8 09.19c4 0pin

and fa10.3(e)verte

PORADJ pin is used to modify the UVLO threshold according to the below relationship considering an external resistor divider R1 / R2 (see block diagram Figure 1):

$$UVLO = \frac{R1 + R2}{R2} V_{POR}$$

If PORADJ is connected to Ground the V<sub>DD</sub> UVLO threshold (V<sub>DD</sub> falling) is typically 2.35 V. In some cases it can be interesting to adjust this threshold at a higher value and by the way increase the V<sub>DD</sub> supply dropout detection level which enables a deactivation sequence if the V<sub>DD</sub> voltage is too low.

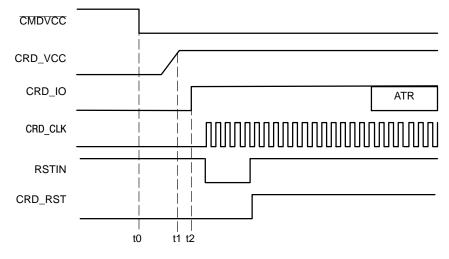

The clock can also be applied to the card using a RSTIN mode allowing controlling the clock starting by setting RSTIN Low (Figure 4). Before running the activation sequence, that is before setting Low CMDVCC RSTIN is set High. In these initial conditions CRD\_CLK starts when RSTIN is pulled Low. This allows a precise count of clock pulses before toggling CRD\_RST High for ATR (Answer To Reset) request.

The internal activation sequence activates the different channels according to a specific hardware built it sequencing internally defined but at the end the actual activation sequencing is the responsibility of the application software and can be redefined by the micro controller to comply with the different standards and the different ways the standards manage this activation (for example light differences exist between the EMV and the ISO7816 standards).

Figure 4. Activation Sequence – RSTIN mode (RSTIN Starting High)

#### POWER-DOWN

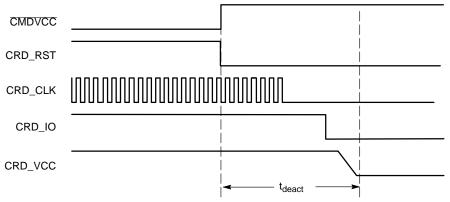

When the communication session is completed the NCN8024 runs a deactivation sequence by setting High CMDVCC. The below power down sequence is executed:

CRD\_RST is forced to Low

CRD\_CLK is set Low 12  $\mu$ s after CRD\_RST. CRD\_IO, CRD\_AUX1 and CRD\_AUX2 are pulled Low Finally CRD\_V<sub>CC</sub> supply can be shut off.

Figure 6. Deactivation Sequence

#### FAULT DETECTION

In order to protect both the interface and the external smart card, the NCN8024 provides security features to prevent failures or damages as depicted here after.

Card extraction detection

V<sub>DD</sub> under voltage detection

Short circuit or overload on CRD\_V<sub>CC</sub>

Card pin current limitation: in the case of a short circuit to ground. No feedback is provided to the external MPU. DC/DC operation: the internal circuit continuously senses the  $CRD_V_{CC}$  voltage (in the case of either over or under voltage situation).

DC/DC operation: under voltage detection on  $V_{DDP}$  or overload on VUP Overheating

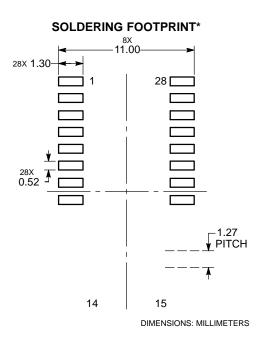

SOIC-28 WB CASE 751F ISSUE J

DATE 23 SEP 2015

TSSOP28 CASE 948AA ISSUE A

DATE 26 OCT 2011

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi