### MARKING DIAGRAMS

/

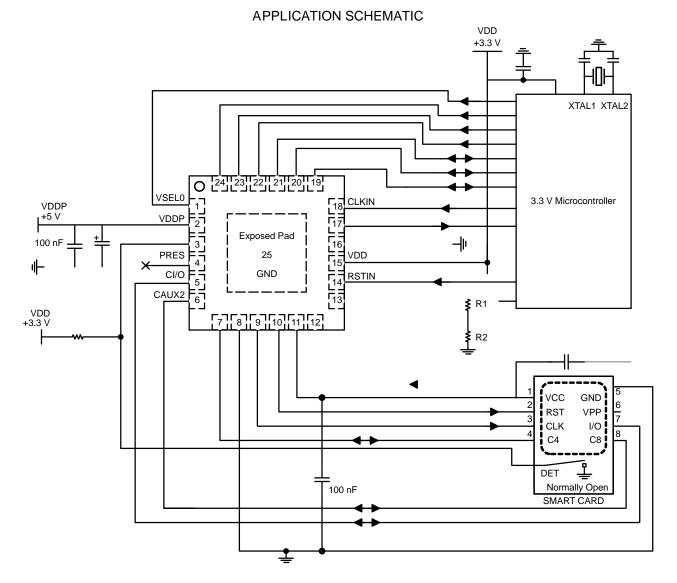

The NCN8025 / NCN8025A is a compact and cost effective single smart card interface IC. It is dedicated for 1.8 V / 3.0 V / 5.0 V smart card reader/writer applications. The card V<sub>CC</sub> supply is provided by a built in very low drop out and low noise LDO.

The device is fully compatible with the ISO 7816 3, EMV 4.3, UICC and related standards including NDS and other STB standards (Nagravision, Irdeto...). It satisfies the requirements specifying conditional access into Set Top Boxes (STB) or Conditional Access Modules (CAM and CAS).

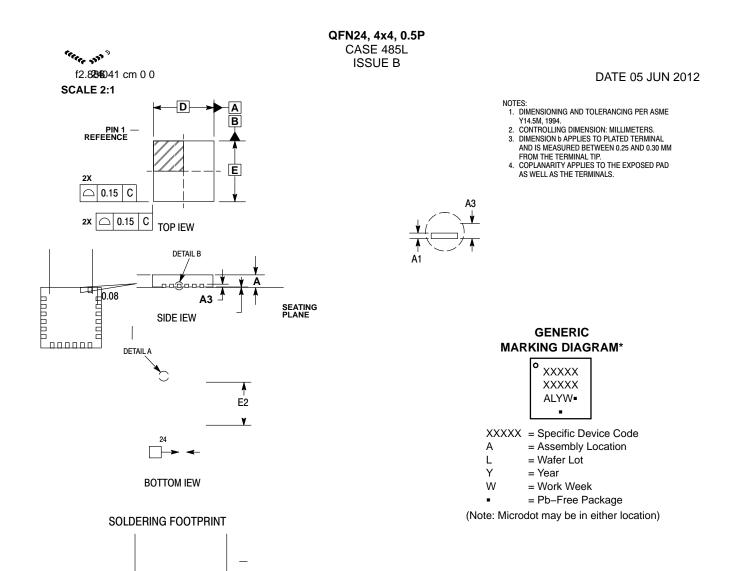

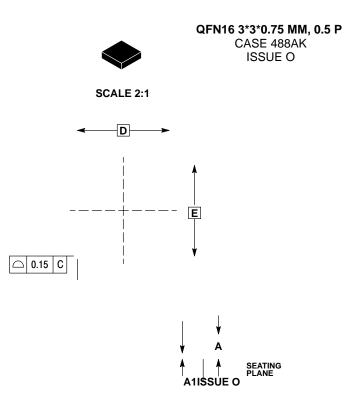

This smart card interface IC is available in a QFN 24 package (NCN8025A) providing all of the industry standard features usually required for STB smart card interface. It is also offered in a very compact package profile, QFN 16 (NCN8025), satisfying the requirements of cost efficiency and space saving requested by CAM and SIM applications.

For details regarding device implementation refer to application note AND8003/D, available upon request (please contact your local **onsemi** sales office or representative).

#### Features

Single IC Card Interface

Fully Compatible with ISO 7816 3, EMV 4.3, UICC and Related Standards Including NDS and Other STB Standards (Nagravision, Irdeto...) 3 Bid rectional Buffered I/O Level Shifters (C4, C7 and

C8) (QFN 24) 1 Bidirectional I/O Level Shifter for

the QFN 16 compact version 1.8 V, 3.0 V or 5.0 V  $\pm$  5 % Regulated Card Power

Supply Generation such as ICC  $\leq$  70 mA

Regulator Power Supply:  $V_{DDP} = 2.7 \text{ V}$  to 5.5 V (@ 1.8 V).

3.0 V to 5.5 V (@ 3.0 V) & 4.85 V to 5.5 V (@ 5.0 V)

Independent Power Supply range on Controller

Interface such as  $V_{DD} = 2.7$  V to 5.5 V

Handles Class A, B and C Smart Cards

Short Circuit Protection on all Card Pins

Support up to 27 MHz input Clock with Internal

Division Ratio 1/1, 1/2, 1/4 and 1/8 through CLKDIV1 and CLKDIV2

ESD Protection on Card Pins up to +8 kV (Human Body Model)

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 13 of this data sheet.

Activation / Deactivation Sequences (ISO7816 Sequencer)

Fault Protection Mechanisms Enabling Automatic Device Deactivation in Case of Overload, Overheating, Card Take off or Power Supply Drop out (OCP, OTP, UVP)

Interrupt Signal INT for Card Presence and Faults External Under Voltage Lockout Threshold Adjustment on VDD (PORADJ Pin) (Except QFN 16) Available in 2 Package Formats: QFN 24 (NCN8025A) and QFN 16 (NCN8025) These are Pb Free Devices

Typical Application

Pay TV, Set Top Box Decoder with Conditional Access and Pay per View

Conditional Access Module (CAM / CAS)

SIM card interface applications (UICC / USIM)

Point Of Sales and Transaction Terminals

Electronic Payment and Identification

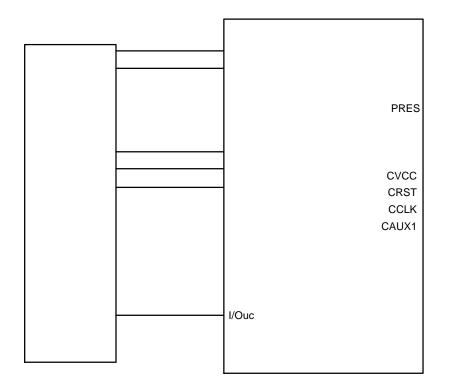

### PIN FUNCTION AND DESCRIPTION

| Pin<br>(QFN24) | Pin<br>(QFN16) | Name  | Туре | Description |

|----------------|----------------|-------|------|-------------|

| 6              | -              | CAUX2 |      |             |

|                |                |       |      |             |

|                |                |       |      |             |

### ATTRIBUTES

| Characteristics                                                                                                                                                                             | Values                         |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| ESD protection<br>Human Body Model (HBM) (Note 1)<br>Card Pins (card interface pins 3–11)<br>All Other Pins<br>Machine Model (MM)<br>Card Pins (card interface pins 3–11)<br>All Other Pins | 8 kV<br>2 kV<br>400 V<br>150 V |  |  |  |

| Moisture sensitivity (Note 2) QFN-24 and QFN-16                                                                                                                                             | Level 1                        |  |  |  |

| Flammability Rating Oxygen Index: 28 to 34                                                                                                                                                  | UL 94 V–0 @ 0.125 in           |  |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test                                                                                                                                     |                                |  |  |  |

1. Human Body Model (HBM), R =  $1500 \Omega$ , C = 100 pF. 2. For additional information, see Application Note AND8003/D.

### MAXIMUM RATINGS (Note 3)

| Rating                                           |                  | Symbol                   | Value                                 | Unit |

|--------------------------------------------------|------------------|--------------------------|---------------------------------------|------|

| Regulator Power Supply Voltage                   |                  | V <sub>DDP</sub>         | –0.3 V <sub>DDP</sub> 5.5             | V    |

| Power Supply from Microcontroller Side           | V <sub>DD</sub>  | –0.3 V <sub>DD</sub> 5.5 | V                                     |      |

| External Card Power Supply                       | CVCC             | -0.3 CVCC 5.5            | V                                     |      |

| Digital Input Pins                               |                  | V <sub>in</sub>          | –0.3 V <sub>in</sub> V <sub>DD</sub>  | V    |

| Digital Output Pins (I/Ouc, AUX1uc, AUX2uc, INT) |                  | Vout                     | –0.3 V <sub>out</sub> V <sub>DD</sub> | V    |

| Smart card Output Pins                           |                  | Vout                     | –0.3 V <sub>out</sub> CVCC            | V    |

| Thermal Resistance Junction-to-Air (Note 4)      | QFN–24<br>QFN–16 | $R_{\thetaJA}$           | 37<br>48                              | C/W  |

| Operating Ambient Temperature Range              |                  | T <sub>A</sub>           | -40 to +85                            | С    |

| Operating Junction Temperature Range             | Τ <sub>J</sub>   | -40 to +125              | •                                     |      |

| Symbol             | Parameter                                                                                                                                                                                                                        | Min                    | Тур | Max                   | Unit |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|------|

| F <sub>CLKIN</sub> | Clock frequency on pin CLKIN (Note 7)                                                                                                                                                                                            | -                      | -   | 27                    | MHz  |

| V <sub>IL</sub>    | Input Voltage level Low: CLKIN, RSTIN, CLKDIV1, CLKDIV2, CMDVCC, VSEL0, VSEL1                                                                                                                                                    |                        | -   | 0.3 x V <sub>DD</sub> | V    |

| V <sub>IH</sub>    | Input Voltage level High: CLKIN, RSTIN, CLKDIV1, CLKDIV2, CMDVCC, VSEL0, VSEL1                                                                                                                                                   | 0.7 x V <sub>DD</sub>  | -   | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IL</sub>    | CLKDIV1, CLKDIV2, $\overline{\text{CMDVCC}}$ , RSTIN, CLKIN, VSEL0, VSEL1 Low Level Input Leakage Current, V <sub>IL</sub> = 0 V                                                                                                 | -                      | -   | 1                     | μΑ   |

| I <sub>IH</sub>    | CLKDIV1, CLKDIV2, $\overline{CMDVCC}$ , RSTIN, CLKIN, VSEL0, VSEL1 Low Level Input Leakage Current, V <sub>IH</sub> = V <sub>DD</sub>                                                                                            | -                      | _   | 1                     | μΑ   |

| V <sub>IL</sub>    | Input Voltage level Low: I/Ouc, AUX1uc, AUX2uc                                                                                                                                                                                   | -0.3                   |     | 0.5                   | V    |

| V <sub>IH</sub>    | Input Voltage level High: I/Ouc, AUX1uc, AUX2uc                                                                                                                                                                                  | 0.7 x V <sub>DD</sub>  |     | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IL</sub>    | I/Ouc, AUX1uc, AUX2uc Low level input leakage current, $V_{IL} = 0 V$                                                                                                                                                            | -                      | -   | 600                   | μA   |

| I <sub>IH</sub>    | I/Ouc, AUX1uc, AUX2uc High level input leakage current, $V_{IH} = V_{DD}$                                                                                                                                                        | -                      | -   | 10                    | μA   |

| V <sub>OH</sub>    | I/Ouc, AUX1uc, AUX2uc data channels, @ Cs $\leq$ 30 pF<br>High Level Output Voltage (CRD_I/O = CAUX1 = CAUX2 = CVCC)<br>$I_{OH} = -40 \ \mu A \text{ for } V_{DD} > 2 \ V (I_{OH} = -20 \ \mu A \text{ for } V_{DD} \leq 2 \ V)$ | 0.75 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.1 | v    |

| V <sub>OL</sub>    | Low Level Output Voltage (CRD_I/O = CAUX1 = CAUX2 = 0 V)<br>$I_{OL}$ = + 1 mA                                                                                                                                                    | 0                      | -   | 0.3                   | V    |

| t <sub>Ri/Fi</sub> | Input Rising/Falling times (Note 7)                                                                                                                                                                                              | -                      | -   | 1.2                   | μs   |

| t <sub>Ro/Fo</sub> | Output Rising/Falling times (Note 7)                                                                                                                                                                                             | -                      | -   | 0.1                   | μs   |

| R <sub>pu</sub>    | I/0uc, AUX1uc, AUX2uc Pull Up Resistor                                                                                                                                                                                           | 8                      | 11  | 16                    | kΩ   |

| V <sub>OH</sub>    | Output High Voltage<br>$\overline{INT} @ I_{OH} = -15 \ \mu A \text{ (source)}$                                                                                                                                                  | 0.75 x V <sub>DD</sub> | -   | _                     | V    |

| V <sub>OL</sub>    | Output Low Voltage<br>INT @ I <sub>OL</sub> = 2 mA (sink)                                                                                                                                                                        | 0                      | _   | 0.30                  | V    |

60

$k\Omega$

40

50

HOST INTERFACE SECTION CLKIN, RSTIN, I/Ouc, AUX1uc, AUX2uc, CLKDIV1, CLKDIV2, CMDVCC, VSEL0, VSEL1 (VDD =

R<sub>INT</sub>

Guaranteed by design and characterization.

Option available under request (metal change). The current option is an inverter–like output.

TNT Pull Up Resistor (open-drain output configuration option) (Note 8)

| Symbol                                               | Parameter                                                                                                                                                                                                                 | Min                      | Тур         | Max                                    | Unit           |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|----------------------------------------|----------------|

| V <sub>OH</sub><br>V <sub>OL</sub>                   | CRST @ CVCC = 1.8 V, 3.0 V, 5.0 V<br>Output RESET V <sub>OH</sub> @ I <sub>rst</sub> = -200 μA<br>Output RESET V <sub>OL</sub> @ I <sub>rst</sub> = 200 μA                                                                | 0.9 x CVCC<br>0          | -           | CVCC<br>0.20                           | V<br>V         |

| t <sub>R</sub><br>t <sub>F</sub><br>t <sub>R/F</sub> | t <sub>F</sub> Output RESET Fall time @ C <sub>out</sub> = 100 pF (Note 9)                                                                                                                                                |                          | -<br>-<br>- | 100<br>100<br>200                      | ns<br>ns<br>ns |

| td                                                   | RSTIN to CRST delay – Reset enabled (Note 9)                                                                                                                                                                              | -                        | -           | 2                                      | μs             |

|                                                      | CCLK @ CVCC = 1.8 V, 3.0 V or 5.0 V                                                                                                                                                                                       |                          |             |                                        |                |

| F <sub>CRDCLK</sub>                                  | Output Frequency (Note 9)                                                                                                                                                                                                 | -                        | -           | 27                                     | MHz            |

| V <sub>OH</sub><br>V <sub>OL</sub>                   | Output CCLK V <sub>OH</sub> @ $I_{clk} = -200 \ \mu A$<br>Output CCLK V <sub>OL</sub> @ $I_{clk} = 200 \ \mu A$                                                                                                           | 0.9 x CVCC<br>0          | -<br>-      | CVCC<br>+0.2                           | V<br>V         |

| F <sub>DC</sub>                                      | Output Duty Cycle (Note 9)                                                                                                                                                                                                | 45                       | -           | 55                                     | %              |

| t <sub>rills</sub><br>t <sub>ulsa</sub>              | Rise & Fall time<br>Output CCLK Rise time @ C <sub>out</sub> = 33 pF (Note 9)<br>Output CCLK Fall time @ C <sub>out</sub> = 33 pF (Note 9)                                                                                | -<br>-                   | -<br>-      | 16<br>16                               | ns<br>ns       |

| SR                                                   | Slew Rate @ C <sub>out</sub> = 33 pF (CVCC = 3.0 V or 5.0 V) (Note 9)                                                                                                                                                     | 0.2                      | -           | -                                      | V/ns           |

|                                                      | CAUX1, CAUX2, CI/O @ CVCC = 1.8 V, 3.0 V, 5.0 V                                                                                                                                                                           |                          |             |                                        |                |

| V <sub>IH</sub>                                      | Input Voltage High Level<br>1.8 V Mode<br>3.0 V Mode<br>5.0 V Mode                                                                                                                                                        | 1.0<br>1.6<br>2.3        | -<br>-<br>- | CVCC + 0.3<br>CVCC + 0.3<br>CVCC + 0.3 | V<br>V<br>V    |

| V <sub>IL</sub>                                      | Input Voltage Low Level<br>1.8 V mode<br>3.0 V mode<br>5.0 V mode                                                                                                                                                         | -0.30<br>-0.30<br>-0.30  | -<br>-<br>- | 0.50<br>0.80<br>1.00                   | V<br>V<br>V    |

| I <sub>IL</sub>  <br> I <sub>IH</sub>                |                                                                                                                                                                                                                           |                          |             | 600<br>10                              | μA<br>μA       |

| V <sub>OH</sub>                                      | Output V <sub>OH</sub><br>@ I <sub>OH</sub> = -40 μA for CVCC = 3.0 V and 5.0 V<br>@ I <sub>OH</sub> = -20 μA for CVCC = 1.8 V                                                                                            | 0.8 x CVCC<br>0.8 x CVCC | -<br>-      | CVCC + 0.1<br>CVCC + 0.1               | V<br>V         |

| V <sub>OL</sub>                                      | Output V <sub>OL</sub><br>@ $I_{OL} = 1 \text{ mA}, V_{IL} = 0 \text{ V} \text{ for CVCC} = 1.8 \text{ V}$<br>@ $I_{OL} = 1 \text{ mA}, V_{IL} = 0 \text{ V} \text{ for CVCC} = 3.0 \text{ V} \text{ and } 5.0 \text{ V}$ | 0<br>0                   | -<br>-      | 0.27<br>0.30                           | V<br>V         |

| t <sub>Ri / Fi</sub>                                 | Input Rising/Falling times (Note 9)                                                                                                                                                                                       | -                        | -           | 1.2                                    | μs             |

| t <sub>Ro / Fo</sub>                                 | Output Rising/Falling times / C <sub>out</sub> = 80 pF (Note 9)                                                                                                                                                           | -                        | -           | 0.1                                    | μs             |

| F <sub>bidi</sub>                                    | Maximum data rate through bidirectional I/O, AUX1 & AUX2 channels (Note 9)                                                                                                                                                | -                        | -           | 1                                      | MHz            |

| R <sub>PU</sub>                                      | CAUX1, CAUX2, CI/O Pull– Up Resistor                                                                                                                                                                                      | 8                        | 11          | 16                                     | kΩ             |

| SMART CARD INTERFACE SECTION CI/O, CAUX1, CAUX2, CCLK, CRST, PRES, PRES (VDD = 3.3 V; VDDP = 5 V; Tamb = 25 C | ; |

|---------------------------------------------------------------------------------------------------------------|---|

| F <sub>CLKIN</sub> = 10 MHz)                                                                                  |   |

can be interesting to adjust this threshold at a higher value and by the way increase the  $V_{DD}$  supply dropout detection level which enables a deactivation sequence if the  $V_{DD}$  voltage is too low.

For example, there are microcontrollers for which the minimum supply voltage insuring a correct operating is higher than 2.6 V; increasing UVLO<sub>VDD</sub> (V<sub>DD</sub> falling) is consequently necessary. Considering for instance a resistor bridge with R1 = 56 k $\Omega$ , R2 = 42 k $\Omega$  and V<sub>POR</sub> = 1.27 V typical the V<sub>DD</sub> dropout detection level can be increased up to:

$$UVLO = \frac{56k + 42k}{42k} V_{POR-} = 2.96 \text{ V} \qquad (\text{eq. 2})$$

CLOCK DIVIDER:

The input clock can be divided by 1/1, 1/2, 1/4, or 1/8, depending upon the specific application, prior to be applied to the smart card driver. These division ratios are programmed using pins CLKDIV1 and CLKDIV2 (see Table 2). The input clock is provided externally to pin CLKIN.

Table 2. CLOCK FREQUENCY PROGRAMMING

| CLKDIV1 | CLKDIV2 | F <sub>CCLK</sub> |

|---------|---------|-------------------|

| 0       | 0       | CLKIN / 8         |

| 0       | 1       | CKLKIN / 4        |

| 1 0     |         | CLKIN             |

| 1 1     |         | CLKIN / 2         |

The clock input stage (CLKIN) can handle a 27 MHz maximum frequency signal. Of course, the ratio must be defined by the user to cope with Smart Card considered in a given application

In order to avoid any duty cycle out of the 45% / 55% range specification, the divider is synchronized by the last flip flop, thus yielding a constant 50% duty cycle, whatever be the divider ratio 1/2, 1/4 or 1/8. On the other hand, the output signal Duty Cycle cannot be guaranteed 50% if the division ratio is 1 and if the input Duty Cycle signal is not within the 46% - 56% range at the CLKIN input.

When the signal applied to CLKIN is coming from the external controller, the clock will be applied to the card under the control of the microcontroller or similar device after the activation sequence has been completed.

#### DATA I/O, AUX1 and AUX2 LEVEL SHIFTERS

The three bidirectional level shifters I/O, AUX1 and AUX2 adapt the voltage difference that might exist between the micro controller and the smart card. These three channels are identical. The first side of the bidirectional level

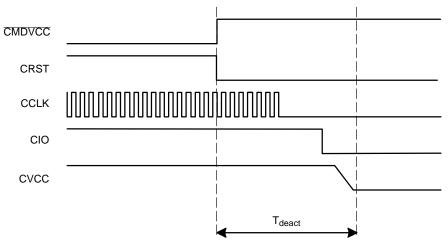

### POWER-DOWN

When the communication session is completed the NCN8025 / NCN8025A runs a deactivation sequence by setting High CMDVCC. The below power down sequence is executed:

CRST is forced to Low CCLK is set Low 12 µs after CRST. CI/O, CAUX1 and CAUX2 are pulled Low Finally CVCC supply can be shut off.

Figure 7. Deactivation Sequence

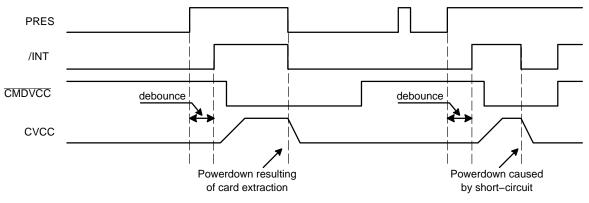

### FAULT DETECTION

In order to protect both the interface and the external smart card, the NCN8025 / NCN8025A provides security features to prevent failures or damages as depicted here after.

Card extraction detection

V<sub>DD</sub> under voltage detection

Short circuit or overload on CVCC

DC/DC operation: the internal circuit continuously senses the CVCC voltage (in the case of either over or under voltage situation).

DC/DC operation: under voltage detection on  $V_{\ensuremath{\text{DDP}}}$  Overheating

Card pin current limitation: in the case of a short circuit to ground. No feedback is provided to the external MPU.

Figure 8. Fault Detection and Interrupt Management

Interrupt Pin Management:

A card session is opened by toggling CMDVCC High to Low.

Before a card session,  $\overline{\text{CMDVCC}}$  is supposed to be in a High position.  $\overline{\text{INT}}$  is Low if no card is present in the card connector (Normally open or normally closed type).  $\overline{\text{INT}}$  is High if a card is present. If a card is inserted ( $\overline{\text{INT}}$  = Highv N1oc Tm 20T As illustrated by Figure 8 the device has a debounce timer of 8 ms typical duration. When a card is inserted, output  $\overline{INT}$  goes High only at the end of the debounce time. When the card is removed a deactivation sequence is automatically and immediately performed and  $\overline{INT}$  goes Low.

### ESD PROTECTION

The NCN8025 / NCN8025A includes devices to protect the pins against the ESD spike voltages. To cope with the different ESD voltages developed across these pins, the built in structures have been designed to handle either 2 kV, when related to the micro controller side, or 8 kV when connected with the external contacts (HBM model). Practically, the CRST, CCLK, CI/O, CAUX1, CAUX2, PRES and PRES pins can sustain 8 kV. The CVCC pin has the same ESD protection and can source up to 70 mA continuously, the absolute maximum current being internally limited with a max at 150 mA. The CVCC current limit depends on  $V_{DDP}$  and CVCC.

2.90

DIMENSIONS: MILLIMETERS

L

16X

DATE 13 SEP 2004

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi