# onse i

R18

#### Figure 1. Typical Application Example

#### PIN FUNCTION DESCRIPTION

.

| Pin # | Pin Name | Function                   | Pin Description                                                                                                 |

|-------|----------|----------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1     | CSS(dis) | Soft                       | Soft acitor discharge pin. Connect to the soft acitor to reset it before startup or during overload conditions. |

| 2     | Fmax     | Maximum frequency<br>clamp | A resistor sets the maximum frequency excursion                                                                 |

| 3     | Ctimer   | Timer duration             | Sets the timer duration in presence of a fault                                                                  |

| 4     | Rt       | Minimum frequency<br>clamp | Connecting a resistor to this pin, sets the minimum oscillator frequency reached for $V_{FB} = 1 \text{ V}.$    |

| 5     | BO       |                            |                                                                                                                 |

Figure 2. Internal Circuit Architecture (NCP1397A)

#### MAXIMUM RATINGS

| Rating                                                           | Symbol                   | Value                                         | Unit |

|------------------------------------------------------------------|--------------------------|-----------------------------------------------|------|

| High Voltage bridge pin, pin 14                                  | V <sub>BRIDGE</sub>      |                                               | V    |

| Floating supply voltage, ground referenced                       | V <sub>BOOT</sub>        | 0 to 20                                       | V    |

| High side output voltage                                         | V <sub>DRV(HI)</sub>     | V <sub>BRIDGE</sub><br>V <sub>BOOT</sub> +0.3 | V    |

| Low side output voltage                                          | V <sub>DRV(LO)</sub>     | c+0.3                                         | V    |

| Allowable output slew rate                                       | dV <sub>BRIDGE</sub> /dt | 50                                            | V/ns |

| Power Supply voltage, pin 12                                     | V <sub>CC</sub>          | 20                                            | V    |

| Maximum voltage, all pins (except pin 11 and 10)                 |                          |                                               | V    |

| Thermal Resistance Junction                                      | R <sub>θJA</sub>         | 130                                           | C/W  |

| Storage Temperature Range                                        |                          | 50                                            | С    |

| ESD Capability, Human Body Model (HBM) (All pins except HV pins) |                          | 2                                             | kV   |

| ESD Capability, Machine Model (MM)                               |                          | 200                                           | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. This device(s) contains ESD protection and exceeds the following tests: Human Body Model 2000 V per JEDEC Standard JESD22

Machine Model 200 V per JEDEC Standard JESD22

2. This device meets latchup tests defined by JEDEC Standard JESD78.

#### **ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25$  C, for min/max values  $T_J = 125$  C, Max  $T_J = 150$  C,  $V_{CC} = 12$  V unless otherwise noted)

Symbol

**ELECTRICAL CHARACTERISTICS** (continued) (For typical values  $T_J = 25$  C, for min/max values  $T_J =$

Figure 25. The Simplified VCO Architecture

This techniques allows us to detect a fault on the converter in case the FB pin cannot rise above 0.3 V (to actually close the loop) in less than a duration imposed by the programmable timer. Please refer to the fault section for detailed operation of this mode.

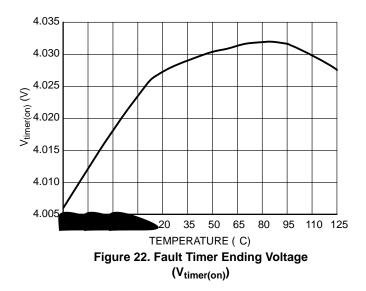

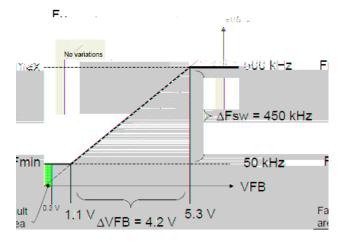

As shown on Figure 26, the internal dynamics of the VCO control voltage will be constrained between 0.5 V and 2.3 V, whereas the feedback loop will drive Pin 6 (FB) between 1.1 V and 5.3 V. If we take the default FB pin excursion numbers, 1.1 V = 50 kHz, 5.3 V = 500 kHz, then the VCO maximum slope will be:

$$\frac{500 \text{ k} - 50 \text{ k}}{4.2} = 107 \text{ kHz/V}$$

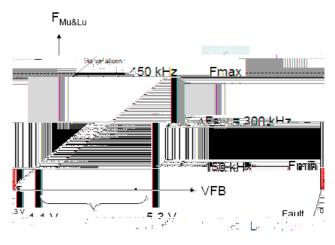

Figures 27 and 28 portray the frequency evolution depending on the feedback pin voltage level in a different frequency clamp combination.

Figure 27. Maximal Default Excursion, Rt = 41 k $\Omega$  on Pin 4 and R<sub>F(max)</sub> = 1.9 k $\Omega$  on Pin 2

Figure 28. Here a Different Minimum Frequency was Programmed as well as a Maximum Frequency Excursion

Please note that the previous small–signal VCO slope has now been reduced to 300k / 4.1 = 71 kHz / V on M<sub>upper</sub> and M<sub>lower</sub> outputs. This offers a mean to magnify the feedback excursion on systems where the load range does not generate a wide switching frequency excursion. Due to this option, we will see how it becomes possible to observe the feedback level and implement skip cycle at light loads. It is important to note that the frequency evolution does not have a real linear relationship with the feedback voltage. This is due to the deadtime presence which stays constant as the switching period changes.

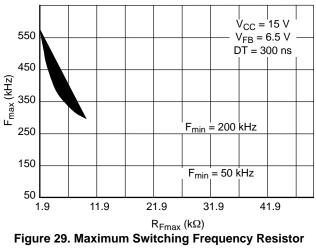

The selection of the three setting resistors ( $F_{max}$ ,  $F_{min}$  and deadtime) requires the usage of the selection charts displayed below:

| =        |      |      |      |      |  |

|----------|------|------|------|------|--|

| 1        |      |      |      |      |  |

| <u> </u> |      |      |      |      |  |

| <u> </u> |      |      |      |      |  |

| <u> </u> |      |      |      |      |  |

| <u> </u> |      |      |      | <br> |  |

| <u> </u> |      |      |      |      |  |

|          |      |      |      |      |  |

|          | <br> |      |      | <br> |  |

| Ξ        | <br> | <br> | <br> | <br> |  |

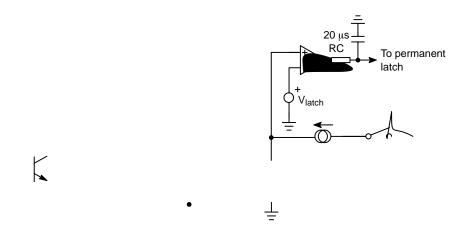

Figure 42. Adding a Comparator on the BO Pin Offers a way to Latch-off the Controller

Figure 44. Fault Input Logic for NCP1397B

Figure 45. A Resistor Can Easily Program the Capacitor Discharge Time

Figure 47. At Power On, Output A is First Activated and the Frequency Slowly Decreases Based on the Soft–Start Capacitor Voltage

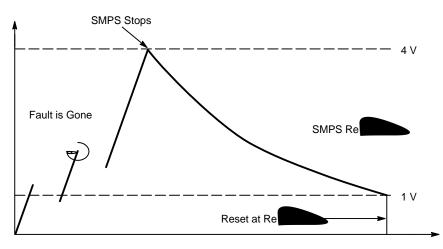

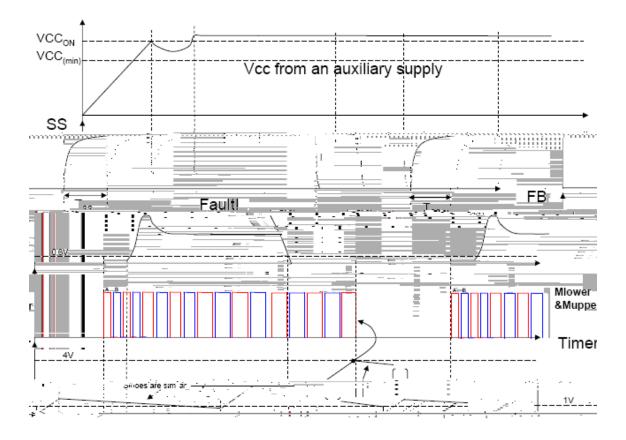

Figure 47 depicts an auto–recovery situation, where the timer has triggered the end of output pulses. In that case, the  $V_{CC}$  level was given by an auxiliary power supply, hence its stability during the hiccup. A similar situation can arise if the user selects a more traditional startup method, with an auxiliary winding. In that case, the  $V_{CC(min)}$

The device incorporates an upper UVLO circuitry that makes sure enough  $V_{gs}$  is available for the upper side MOSFET. The B and A outputs are delivered by the internal logic, as Figure 43 testifies. A delay is inserted in the lower rail to ensure good matching between these propagating signals.

As stated in the maximum rating section, the floating portion can go up to 600 VDC and makes the IC perfectly suitable for offline applications featuring a 400 V PFC front-end stage.

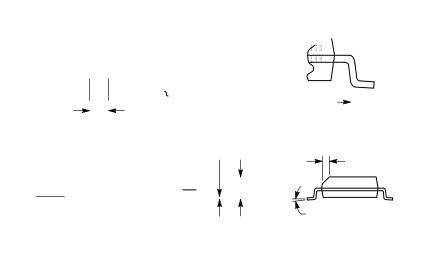

#### **ORDERING INFORMATION**

| Device        | Package     | Shipping†          |  |

|---------------|-------------|--------------------|--|

| NCP1397ADR2G  |             |                    |  |

| NCV1397ADR2G* | SOIC Pin 13 |                    |  |

| NCP1397BDR2G  | (Pb         | 2500 / Tape & Reel |  |

| NCV1397BDR2G* |             |                    |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC and PPAP Capable.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi