The NCP/NCV51198 is a simple, cost–effective, high–speed linear regulator designed to generate the  $V_{TT}$  termination voltage rail for DDR–I, DDR–II and DDR–III memory. The regulator is capable of actively sourcing or sinking up to  $\pm 1.5$  A for DDR–I, or up to  $\pm 0.5$  A for DDR–II /–III while regulating the output voltage to within  $\pm 30$  mV.

The output termination voltage is tightly regulated to track  $V_{TT} = (V_{DDO}/2)$  over the entire current range.

The NCP/NCV51198 incorporates a high–speed differential amplifier to provide ultra–fast response to line and load transients. Other features include extremely low initial offset voltage, excellent load regulation, source/sink soft–start and on–chip thermal shut–down protection.

The NCP/NCV51198 features the power–saving Suspend To Ram (STR) function which will tri–state the regulator output and lower the quiescent current drawn when the /SS pin is pulled low.

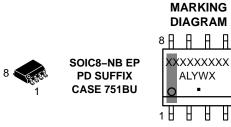

The NCP/NCV51198 is available in a SOIC-8 Exposed Pad package.

#### **Features**

- Generate DDR Memory Termination Voltage (V<sub>TT</sub>)

- For DDR-I, DDR-II, DDR-III Source / Sink Currents

- Supports DDR-I to  $\pm 1.5$  A, DDR-II to  $\pm 0.5$  A (peak)

- Integrated Power MOSFETs with Thermal Protection

- Stable with 10 μF Ceramic V<sub>TT</sub> Capacitor

- High Accuracy Output Voltage at Full-Load

- Minimal External Component Count

- Shutdown for Standby or Suspend to RAM (STR) mode

- Built-in Soft Start

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb–Free Devices

## **Appications**

- Desktop PC's, Notebooks, and Workstations

- Graphics Card DDR Memory Termination

- Set Top Boxes, Digital TV's, Printers

- Embedded Systems

- Active Bus Termination

XXXXX = Specific Device Code A = Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ Pb-Free Package

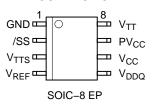

### **PIN CONNECTION**

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information in the package dimensions section on page 8 of this data sheet.

# 1.5 A, DDR-I /-II /-III TERMINATION REGULATOR

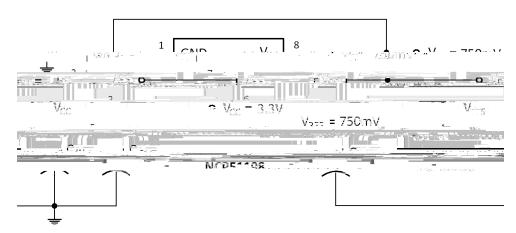

Figure 1. Typical Application Schematic

## **PIN FUNCTION DESCRIPTION – NCP51198**

| Pin Number<br>SO8-EP | Pin Name         | Pin Function                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | GND              | Common Ground.                                                                                                                                                                                                                                                                                                                                                                                    |

| 2                    | /SS              | Suspend Shutdown supports Suspend To RAM function. CMOS compatible input sets V <sub>TT</sub> output to high impedance state. Logic HI = Enable, Logic LO = Shutdown.                                                                                                                                                                                                                             |

| 3                    | V <sub>TTS</sub> | V <sub>TTS</sub> is the V <sub>TT</sub> sense input.                                                                                                                                                                                                                                                                                                                                              |

| 4                    | $V_{REF}$        | $V_{REF}$ is an output pin that provides the buffered output of the internal reference voltage equal to half of $V_{DDQ}$ . Two resistors dividing down the $V_{DDQ}$ voltage on the pin to create the regulated output voltage.                                                                                                                                                                  |

| 5                    | $V_{ m DDQ}$     | The $V_{DDQ}$ pin is an input pin for creating the internal reference voltage to regulate $V_{TT}$ . The $V_{DDQ}$ voltage is connected to an internal resistor divider. The central tap of resistor divider ( $V_{DDQ}$ /2) is connected to the internal voltage buffer, which output is connected to $V_{REF}$ pin and the non–inverting input of the error amplifier as the reference voltage. |

| 6                    | Vcc              | Power for the analog control circuitry.                                                                                                                                                                                                                                                                                                                                                           |

| 7                    | PVcc             | The PV <sub>CC</sub> pin provides the rail voltage from where the V <sub>TT</sub> pin draws load curren TD0019 Tc(pin S-0C2                                                                                                                                                                                                                                                                       |

|                                                                     | N .                |   |             |

|---------------------------------------------------------------------|--------------------|---|-------------|

| TE MAXIMUM RATING                                                   |                    |   |             |

| Ra                                                                  |                    | 1 | Value       |

| / <sub>CC</sub> ,V <sub>DDQ</sub> , /SS to GND (Note 1)             |                    |   | -0.3 to +6  |

| e Temperature                                                       |                    |   | -65 to +150 |

| ng Junction Temperature Range                                       |                    |   | -40 to +125 |

| al Characteristics, SO8-EP Thermorer Rating at 25°C ambient = 2.3 W | e, Junction–to–Air |   | 43          |

| apability, Human Body Model (Not                                    |                    |   | 2000        |

| apability, Machine Model (Note 2)                                   |                    |   | 150         |

table may damage the device. ity may be affected. RACTERISTICS and APPLICA

CTÉRISTICS and APPLICA RMATION for Safe Operating Area.

V

°C

°C

°C/W

V

se limits are exceeded, device functionality

## RECOMMENDED OPERATING CONDITIONS

exceeding those listed in the Maxir ot be assumed, damage may occu n to exceed V<sub>CC</sub>. Refer to ELECTR

| Rating              | Symbol           | Value | Unit |

|---------------------|------------------|-------|------|

| Bias Supply Voltage | V <sub>CCï</sub> |       |      |

## **ELECTRICAL CHARACTERISTICS**

$-40^{\circ}C \leq T_{J} \leq 125^{\circ}C; \ V_{CC} = PV_{CC} = V_{DDQ} = 2.5 \ V; \ unless otherwise noted. \ Typical values are at \ T_{J} = +25^{\circ}C$

| Parameter                                  | Condition                                                                                                                                                              | Symbol         | Min                          | Тур                          | Max                          | Unit |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|------------------------------|------------------------------|------|

| V <sub>TT</sub> Output Voltage<br>(DDR-II) | I <sub>OUT</sub> = 0 A<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.7 V<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.8 V<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.9 V    | Vπ<br>(DDR-II) | -<br>0.816<br>0.866<br>0.916 | -<br>0.850<br>0.900<br>0.950 | -<br>0.881<br>0.931<br>0.981 |      |

|                                            | I <sub>OUT</sub> = +0.5 A<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.7 V<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.8 V<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.9 V | Vπ<br>(DDR-II) | -<br>0.815<br>0.863<br>0.914 | -<br>0.851<br>0.900<br>0.950 | -<br>0.885<br>0.933<br>0.984 | V    |

|                                            | I <sub>OUT</sub> = -0.5 A<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.7 V<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.8 V<br>PV <sub>CC</sub> = V <sub>DDQ</sub> = 1.9 V | Vπ<br>(DDR-II) | -<br>0.814<br>0.862<br>0.913 | -<br>0.850<br>0.900<br>0.950 | -<br>0.884<br>0.932<br>0.983 |      |

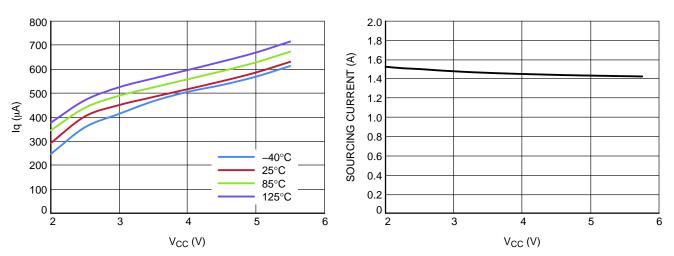

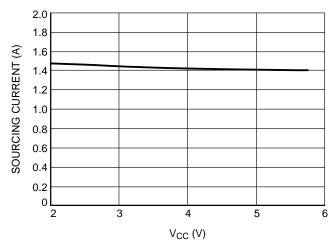

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 8. Iq vs.  $V_{CC}$  over Temperature

Figure 9. Maximum Sourcing Current vs.  $V_{CC}$  ( $V_{DDQ} = PV_{CC} = 1.8 \text{ V}$ )

Figure 10. Maximum Sourcing Current vs.  $V_{CC}$ ( $V_{DDQ} = 2.5 \text{ V}, PV_{CC} = 1.8 \text{ V}$

## **APPLICATIONS INFORMATION**

## General

The NCP/NCV51198 is a bus termination, linear regulator designed to meet the JEDEC requirements for DDR–I, DDR–II and DDR–III memory termination. The NCP/NCV51198 is capable of sourcing and sinking current while accurately tracking and regulating the  $V_{TT}$  output voltage equal to  $(V_{DDQ}\ /\ 2).$  The output stage has been designed to maintain excellent load regulation and preventing shoot–through. The NCP/NCV51198 uses two

### **Table 1. ORDERING INFORMATION**

| Device         | Marking | Package   | Shipping <sup>†</sup> |

|----------------|---------|-----------|-----------------------|

| NCP51198PDR2G  | 51198   | SOIC-8    | 2500 / Tape & Reel    |

| NCV51198PDR2G* | V51198  | (Pb-Free) | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP

Capable.

**DATE 01 APR 2015**

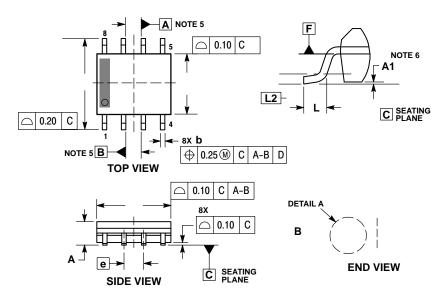

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10mm IN EXCESS OF MAXIMUM MATERIAL

- BE 0.10mm IN EXCESS OF MAXIMUM MATERIAL CONDITION.

4. DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. DIMENSION E DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

5. DIMENSIONS A AND B ARE TO BE DETERMINED AT DATUM F.

6. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

7. TAB CONTOUR MAY VARY MINIMALLY TO INCLUDE TOOLING FEATURES.

- TOOLING FEATURES.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 1.35        | 1.75 |  |

| A1  | 0.00        | 0.10 |  |

| b   | 0.31        | 0.51 |  |

| b1  | 0.28        | 0.48 |  |

| е                  | 1.27 BSC           |      |  |  |  |  |

|--------------------|--------------------|------|--|--|--|--|

| G                  | <b>G</b> 1.55 2.39 |      |  |  |  |  |

| h                  | 0.25               | 0.50 |  |  |  |  |

| <b>L2</b> 0.25 BSC |                    |      |  |  |  |  |

## **GENERIC MARKING DIAGRAM\***

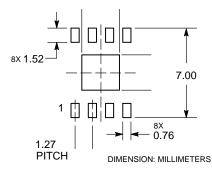

## **RECOMMENDED SOLDERING FOOTPRINT\***

NOTE 7

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.