The NCP51403 is a source/sink Double Data Rate (DDR) termination regulator specifically designed for low input voltage and low-noise systems where space is a key consideration.

The NCP51403 maintains a fast transient response and only requires a minimum output capacitance of 20  $\mu$ F. The NCP51403 supports a remote sensing function and all power requirements for DDR V<sub>TT</sub> bus termination. The NCP51403 can also be used in low–power chipsets and graphics processor cores that require dynamically adjustable output voltages.

The NCP51403 is available in the thermally–efficient DFN10 Exposed Pad package, and is rated both Green and Pb–free.

#### **Features**

- Input Voltage Rails: Supports 2.5 V, 3.3 V and 5 V Rails

- PV<sub>CC</sub> Voltage Range: 1.1 to 3.5 V

- Integrated Power MOSFETs

- Phase Margin >45° with Recommended 20 μF V<sub>TT</sub> Capacitance

- P<sub>GOOD</sub> Logic output pin to Monitor V<sub>TT</sub> Regulation

- EN Logic input pin for Shutdown mode

- V<sub>RI</sub> Reference Input Allows for Flexible Input Tracking Either Directly or Through Resistor Divider

- Remote Sensing (V<sub>TTS</sub>)

- Built-in Under Voltage Lockout and Over Current Limit

- Thermal Shutdown

- Small, Low-Profile 10-pin, 3x3 DFN Package

- These Devices are Pb-Free and are RoHS Compliant

#### **Applications**

- DDR Memory Termination

- Desktop PC's, Notebooks, and Workstations

- Servers and Networking equipment

- Telecom/Datacom, GSM Base Station

- Graphics Processor Core Supplies

- Set Top Boxes, LCD-TV/PDP-TV, Copier/Printers

- Chipset/RAM Supplies as Low as 0.5 V

- Active Bus Termination

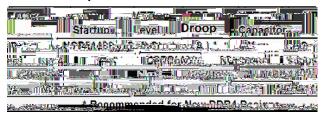

#### DDR3/DDR4 SELECTOR GUIDE

(see notes on page 7)

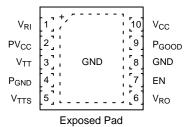

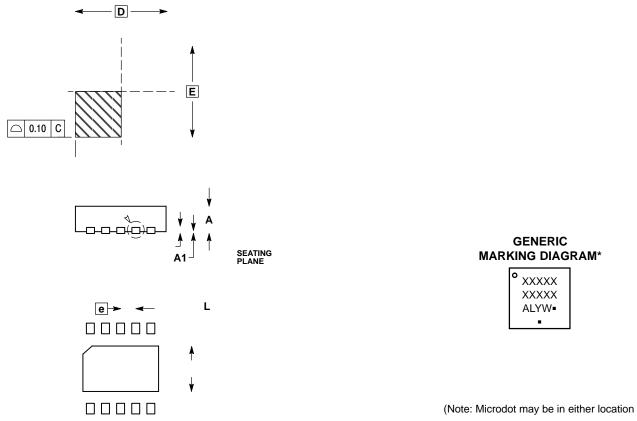

DFN10, 3x3, 0.5P CASE 506CL

#### **MARKING DIAGRAM**

51403 = Specific Device Code A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

#### **PIN CONNECTION**

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP51403MNTXG | DFN10<br>(Pb-Free) | 3000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### PIN FUNCTION DESCRIPTION

| Pin Number | Pin Name         | Pin Function                                                                                                                                                       |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>RI</sub>  | V <sub>TT</sub> External Reference Input ( set to V <sub>DDQ</sub> / 2 thru resistor network ).                                                                    |

| 2          | PV <sub>CC</sub> | Power input. Internally connected to the output source MOSFET.                                                                                                     |

| 3          | $V_{TT}$         | Power Output of the Linear Regulator.                                                                                                                              |

| 4          | $P_{GND}$        | Power Ground. Internally connected to the output sink MOSFET.                                                                                                      |

| 5          | V <sub>TTS</sub> | $V_{TT}$ Sense Input. The $V_{TTS}$ pin provides accurate remote feedback sensing of $V_{TT}$ . Connect $V_{TTS}$ to the remote DDR termination bypass capacitors. |

| 6          | $V_{RO}$         | Independent Buffered V <sub>TT</sub> Reference Output. Sources and sinks over 5 mA. Connect to GND thru 0.1 µF ceramic capacitor.                                  |

| 7          | EN               | Shutdown Control Input. CMOS compatible input. Logic high = enable, logic low = shutdown. Connect to $V_{DDQ}$ for normal operation.                               |

| 8          | GND              | Common Ground.                                                                                                                                                     |

| 9          | r                | ·                                                                                                                                                                  |

### **ELECTRICAL CHARACTERISTICS**

$-40^{\circ}C \leq T_{A} \leq 125^{\circ}C; \ V_{CC} = 3.3 \ V; \ PV_{CC} = 1.8 \ V; \ V_{RI} = V_{TTS} = 0.9 \ V; \ EN = V_{CC}; \ C_{OUT} = 3 \ x \ 10 \ \mu F \ (Ceramic); \ unless \ otherwise \ noted.$

| Parameter                        | Conditions                                  | Symbol           | Min | Тур | Max | Units |

|----------------------------------|---------------------------------------------|------------------|-----|-----|-----|-------|

| SUPPLY CURRENT                   |                                             |                  |     |     |     |       |

| V <sub>CC</sub> Supply Current   | T <sub>A</sub> = +25°C, EN = 3.3 V, No Load | I <sub>VCC</sub> |     | 0.7 | 1   | mA    |

| V <sub>CC</sub> Shutdown Current | T <sub>A</sub> = +25°                       | •                | •   | •   | •   | •     |

|                                  |                                             |                  |     |     |     |       |

## **ELECTRICAL CHARACTERISTICS**

$-40^{\circ}C \leq T_{A} \leq 125^{\circ}C; \ V_{CC} = 3.3 \ V; \ PV_{CC} = 1.8 \ V; \ V_{RI} = V_{TTS} = 0.9 \ V; \ EN = V_{CC}; \ C_{OUT} = 3 \ x \ 10 \ \mu F \ (Ceramic); \ unless \ otherwise \ noted.$

| Parameter             | Conditions                     | Symbol             | Min | Тур | Max | Units |

|-----------------------|--------------------------------|--------------------|-----|-----|-----|-------|

| EN - ENABLE LOGIC     |                                |                    |     |     |     |       |

| Logic Input Threshold | EN Logic high                  | V <sub>IH</sub>    | 1.7 |     |     | V     |

|                       | EN Logic low                   | V <sub>IL</sub>    |     |     | 0.3 | 1     |

| Hysteresis Voltage    | EN pin                         | V <sub>ENHYS</sub> |     | 0.5 |     | V     |

| Logic Leakage Current | EN pin, T <sub>A</sub> = +25°C | •                  |     |     |     |       |

#### General

The NCP51403 is a sink/source tracking termination regulator specifically designed for low input voltage and low external component count systems where space is a key application parameter. The NCP51403 integrates a high–performance, low–dropout (LDO) linear regulator that is capable of both sourcing and sinking current. The LDO regulator employs a fast feedback loop so that small ceramic capacitors can be used to support the fast load transient response. To achieve tight regulation with minimum effect of trace resistance, a remote sensing terminal,  $V_{\rm TTS}$

### DDR3/DDR4 SELECTOR GUIDE

**VTT Startup Time**

SCALE 2:1 **DATE 02 APR 2013**

10X

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " •", may or may not be present.