### 1, NCP81391A

| Description                                                    |

|----------------------------------------------------------------|

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

| ins 28, 29, 30 and 31 must be connected together on the PCB.   |

| ins 28, 29, 30 and 31 must be connected together on the PCB.   |

| 28, 29, 30 and 31 must be connected together on the PCB.       |

| 28, 29, 30 and 31 must be connected together on the PCB.       |

|                                                                |

|                                                                |

| not connect to PCB. See Recommended PCB Footprint for details. |

nation – all signals referenced to PGND unless noted otherwise)

| VMIN | VMAX | Unit |

|------|------|------|

| -0.3 | 13.2 | V    |

| _    | 15   | V    |

| -0.3 | 30   | V    |

| -0.3 | 35   | V    |

| -0.3 | 40   | V    |

| -0.3 | 13.2 | V    |

| -0.3 | 30   | V    |

40 9MA**X**

Propagation Delay, PWM Falling

Table 5. ELECTRICAL CHARACTERISTICS  $(V_{VCC} = V_{VCCD} = 12 \text{ V}, V_{VIN} = 12 \text{ V}, V_{EN} = 5.0 \text{ V}, C_{VCCD} = C_{VCC} = 0.1 \text{ μF unless specified otherwise}) \text{ Min/Max values are valid for the temperature range } -40^{\circ}\text{C} \leq T_{A} \leq 100^{\circ}\text{C} \text{ unless noted otherwise, and are guaranteed by test, design or statistical correlation.})$

|                  |                     |            |     |     | •   |      |

|------------------|---------------------|------------|-----|-----|-----|------|

| Parameter        | Symbol              | Conditions | Min | Тур | Max | Unit |

| PWM INPUT        |                     |            |     |     |     |      |

| Input Leakage    | I <sub>PWM_LK</sub> |            | -   | -   | 5   | μΑ   |

| HIGH SIDE DRIVER |                     |            | •   | •   |     |      |

| Table 5. ELECTRICAL CHARACTERISTICS (V |  |

|----------------------------------------|--|

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

|                                        |  |

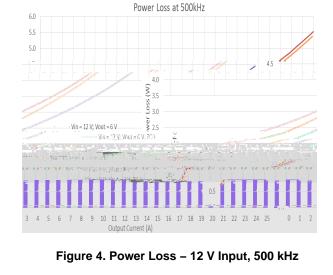

#### **TYPICAL CHARACTERISTICS**

Figure 3. Efficiency - 12 V Input, 500 kHz

Figure 5. Efficiency - 12 V Input, 250 kHz

Figure 6. Power Loss – 12 V Input, 250 kHz

Figure 7. Output Current Derating  $f_{SW}$  = 250 kHz;  $V_{IN}$  = 12 V;  $V_{CC}$  =  $V_{CCD}$  = 12 V;  $V_{OUT}$  = 6 V; L = 720 nH

#### **APPLICATIONS INFORMATION**

#### **Theory of Operation**

#### Low-Side Driver

The low–side driver drives a ground–referenced low– $R_{DS(on)}\,N$ –Channel MOSFET. The voltage rail for the low–side driver is internally connected to VCCD and CGND.

The GLD pin connects directly to the output of the low–side driver. The GLF pins connects directly to the gate of the low–side MOSFET. See Figure 2. GLD and GLF are not connected inside the package. For proper operation, these pins must be connected together on the PCB.

#### **High-Side Driver**

The high–side driver drives a floating low– $R_{DS(on)}$   $N\!\!-\!\!$  channel

#### **Power Supply Decoupling**

The NCP81391/A sources relatively large currents into the MOSFET gates. In order to maintain a constant and stable input supply voltage, low–ESR capacitors should be

DATE 27 JUL 2017