# **Octal Low-Side Relay**

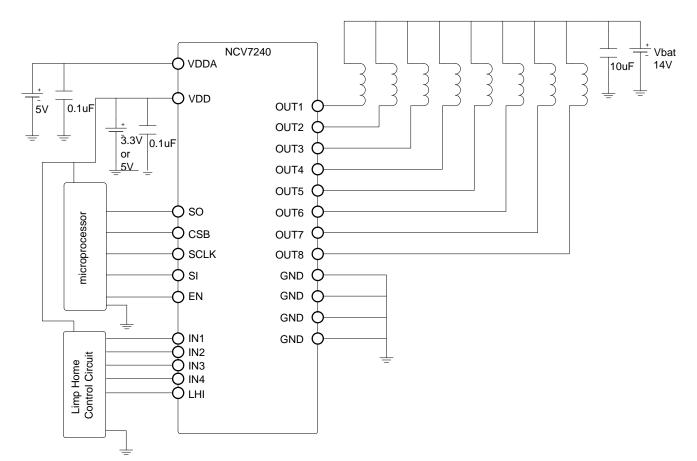

#### Figure 2. Application Diagram (relay loads)

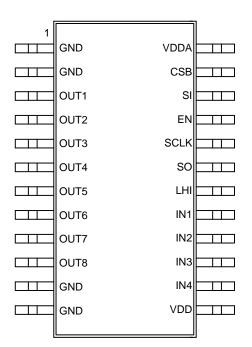

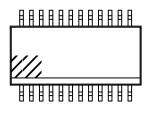

Figure 3. Pinout

#### PACKAGE PIN DESCRIPTION

| SSOP-24 | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1       | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 2       | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 3       | OUT1   | Channel 1 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 4       | OUT2   | Channel 2 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 5       | OUT3   | Channel 3 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 6       | OUT4   | Channel 4 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 7       | OUT5   | Channel 5 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 8       | OUT6   | Channel 6 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 9       | OUT7   | Channel 7 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 10      | OUT8   | Channel 8 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 11      | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 12      | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 13      | VDD    | Digital Power Supply for SO output (3.3 V or 5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 14      | IN4    | Parallel control of OUT4 and OUT8<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 15      | IN3    | Parallel control of OUT3 and OUT7<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull–down will hold the input low.<br>(120 kΩ pull down resistor).                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 16      | IN2    | Parallel control of OUT2 and OUT6.<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 17      | IN1    | Parallel control of OUT1 and OUT5.<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 18      | LHI    | Limp Home Input. Active High.<br>A high on this pin powers up the device and activates the respective output drive INx designator while<br>disabling outputs OUT5–OUT8.<br>Input SPI commands are ignored, but the output register reports faults.<br>(Read capability only. No write capability.)<br>All registers are reset coming out of LHI mode.<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull–down resistor (120 kΩ) will hold the input low. |  |  |  |  |  |  |  |

| 19      | SO     | SPI serial data output. Output high voltage level referenced to pin VDD.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 20      | SCLK   | SPI clock (120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 21      | EN     | Global Enable (active high). (120 kΩ pull down resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 22      | SI     | SPI serial data input (120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 23      | CSB    | SPI Chip Select "Bar" (120 k $\Omega$ pull up resistor to VDD).                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 24      | VDDA   | Analog Power Supply Input voltage (5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

#### MAXIMUM RATINGS

| Parameter                                                                         | Min          | Max                          | Unit |

|-----------------------------------------------------------------------------------|--------------|------------------------------|------|

| Supply Input Voltage (VDDA, VDD)<br>DC                                            | -0.3         | 5.5                          | V    |

| Digital I/O pin voltage<br>(EN, LHI, Inx, CSB, SCLK, SI)<br>(SO)                  | -0.3<br>-0.3 | 5.5<br>V <sub>DD</sub> + 0.3 | V    |

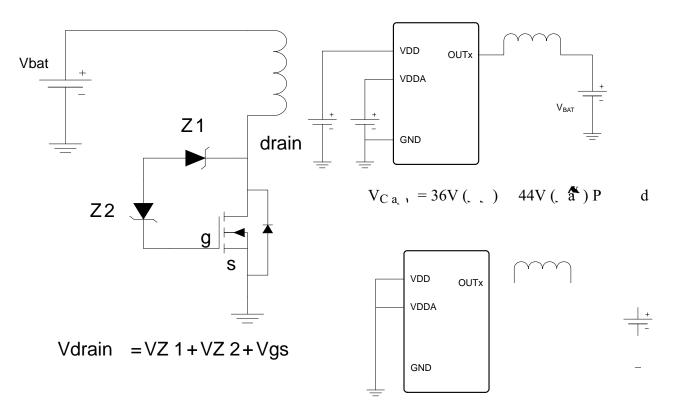

| High Voltage Pins (OUTx)<br>DC<br>Peak Transient                                  | -0.3         | 36<br>44 (Note 1)            | V    |

| Output Current (OUTx)                                                             | –1           | 1.3                          | A    |

| Clamping Energy<br>Maximum (single pulse)<br>Repetitive (multiple pulse) (Note 2) |              | 75<br>-                      | mJ   |

| Operating Junction Temperature Range                                              | -40          | 150                          | •    |

**ELECTRICAL CHARACTERISTICS** (3.0 V < VDD < VDDA, 4.5 V < VDDA (Note 7) < 5.5 V, -40 C  $\leq$  T<sub>J</sub>  $\leq$  150 C, EN = VDD, LHI = 0 V unless otherwise specified).

| Symbol                                     | Characteristic                                           | Conditions                                                                      | Min         | Тур         | Max            | Unit |

|--------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|-------------|-------------|----------------|------|

| GENERAL                                    |                                                          |                                                                                 |             |             |                |      |

| I <sub>VDDA_ON</sub>                       | Operating Current (VDDA)<br>ON Mode<br>(All Channels On) |                                                                                 | -           | 3           | 5              | mA   |

|                                            | Quiescent Current (VDDA)<br>Global Standby Mode          | SI = SCLK = $0 V, CSB = VDD$<br>T <sub>1</sub> = 25 0                           |             |             | 32             |      |

| IVDDA_GS_25<br>IVDDA_GS_85<br>IVDDA_GS_150 | (All Channels Off)                                       | $T_{\rm J} = 85 \text{ C}$<br>$T_{\rm J} = 150 \text{ C}$                       |             |             | 35<br>40       |      |

| Ivdda_lo_25<br>Ivdda_lo_85<br>Ivdda_lo_150 | Quiescent Current (VDDA)<br>Low lq Mode                  | $SI = SCLK = EN = 0 V, CSB = VDD$ $T_{J} = 25 C$ $T_{J} = 85 C$ $T_{J} = 150 C$ | _<br>_<br>_ | _<br>_<br>_ | 10<br>10<br>20 | μ    |

| I <sub>VDD_ON</sub>                        | Operating Current (VDD)<br>ON Mode<br>(All Channels On)  | EN=high, SCLK = Inx = 0 V,<br>CSB = VDD = VDDA                                  | _           | 0.3         | 0.5            | mA   |

I<sub>VDD\_GS\_25</sub> I<sub>VDD\_GS\_85</sub>

**ELECTRICAL CHARACTERISTICS** (3.0 V < VDD < VDDA, 4.5 V < VDDA (Note 7) < 5.5 V, -40 C  $\leq$  T<sub>J</sub>  $\leq$  150 C, EN = VDD, LHI = 0 V unless otherwise specified).

| Symbol        | Characteristic | Conditions | Min | Тур | Max | Unit |

|---------------|----------------|------------|-----|-----|-----|------|

| OUTPUT TIMING | SPECIFICATIONS |            |     |     |     |      |

t<sub>WU</sub>

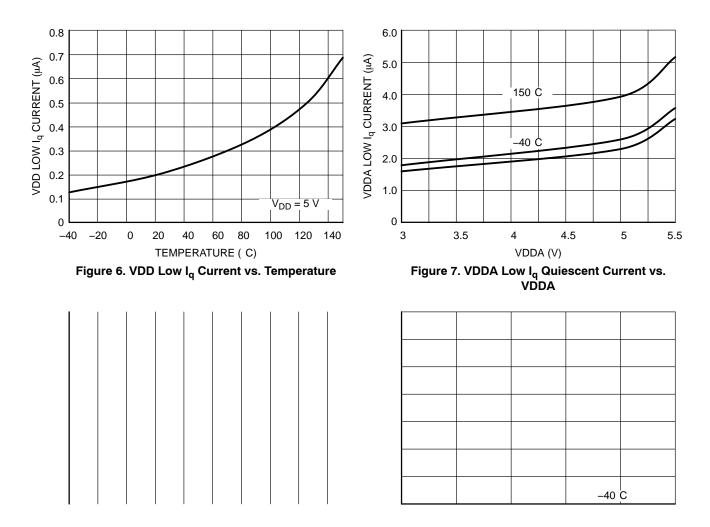

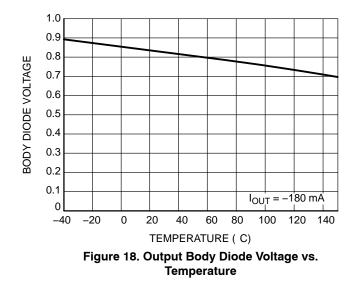

#### **TYPICAL PERFORMANCE GRAPHS**

#### **TYPICAL PERFORMANCE GRAPHS**

Figure 12. Output R

#### **TYPICAL PERFORMANCE GRAPHS**

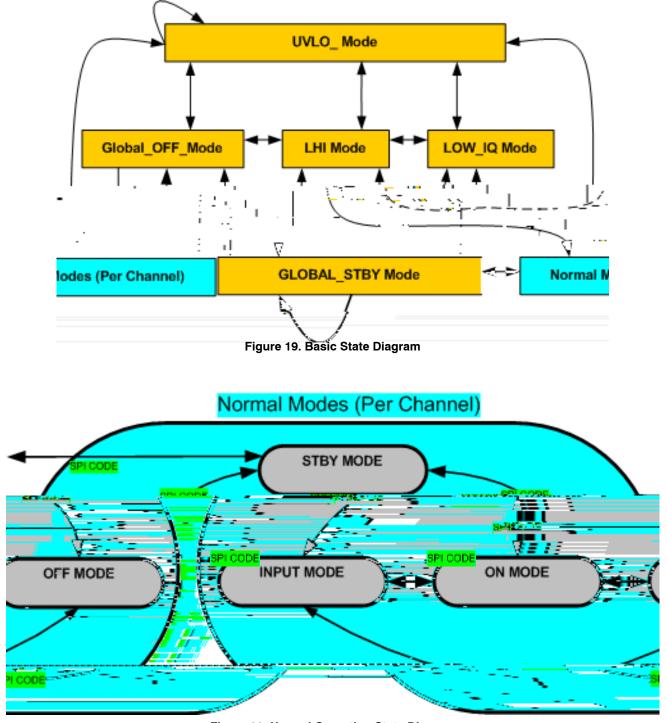

Figure 20. Normal Operation State Diagram

Figure 21. Detailed State Diagram

Limp Home and PWM operation (INx control)

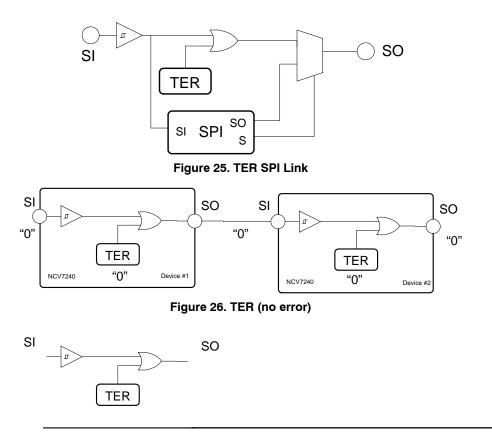

#### **TER Information Retrieval**

TER information retrieval is as simple as bringing CSB high to low. No clock signals are required.

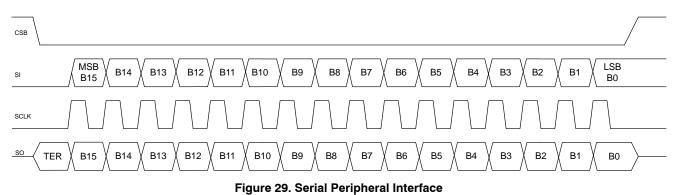

The timing diagram highlighted in Figure 29 shows the SPI interface communication. Note:

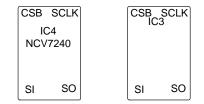

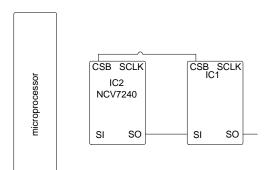

#### DAISY CHAIN SETUP

#### **Serial Connection**

Daisy chain setups are possible with the NCV7240. The serial setup shown in Figure 31 highlights the NCV7240 along with any 16 bit device using a similar SPI protocol. Particular attention should be focused on the fact that the first 16 bits which are clocked out of the SO pin when the CSB pin transitions from a high to a low will be the Diagnostic Output Data from the Fault Output Register. These are the bits representing the status of the IC. Additional programming bits should be clocked in which follow the Diagnostic Output bits. The timing diagram shows a typical transfer of data from the microprocessor to the SPI connected IC's.

#### 8-bit Devices

The NCV7240 is also compatible with 8 bit devices due to the features of the frame detection circuitry. The internal bit counter of the NCV7240 starts counting clock pulses when CSB goes low. The 1st valid word consists of 16 bits and each subsequent word must be comprised of just 8 bits (reference the Frame Detection Section).

#### **Stepper Motor Operation**

The NCV7240 device is capable of driving stepper motors. Each stepper motor requires 4 low side drive outputs. Consequently, each NCV7240 device is capable of driving two stepper motors. Figure 36 below illustrates a Unipolar stepper motor setup. For proper operation, the code listed in Table 3 should be used (and repeated) for one way operation (clockwise). For reverse direction, simply reverse the code and repeat (counterclockwise). Outputs 1 4 are utilized for one stepper usage. For a 2<sup>nd</sup> stepper motor, repeat the code used for outputs 1 4 to outputs 5 8. During operation waveforms similar to Figure 37 can be expected on the OUTx pins.

Figure 36. Stepper Motor Operation Setup

SI SPI Inp t t (1 - t t t t ) The 16 bit data received (SI) is decoded into instructions for each channel per the table below. After a power on reset, all register bits are set to a 1.

#### Table 4. SPI INPUT DATA

| Channe | Channel 8 Channel 7 |     | nel 7 | Channel 6 Channel 5 |     | Channel 4 Channel 3 |    | nel 3 | Channel 2 |    | Channel 1 |    |    |    |    |

|--------|---------------------|-----|-------|---------------------|-----|---------------------|----|-------|-----------|----|-----------|----|----|----|----|

| MSE    | 3                   |     |       |                     |     |                     |    |       |           |    |           |    |    | LS | в  |

| B15    | B14                 | B13 | B12   | B11                 | B10 | B9                  | B8 | B7    | B6        | B5 | B4        | B3 | B2 | B1 | B0 |

#### INPUT DATA REGISTER

| Field     | Bits                             | Description |                                                                                                |                       |  |  |

|-----------|----------------------------------|-------------|------------------------------------------------------------------------------------------------|-----------------------|--|--|

| channel x |                                  |             | nmand                                                                                          |                       |  |  |

| (x = 1–8) | 13, 12<br>11, 10<br>9, 8<br>7, 6 | 00          | 0 Channel Stand-by Mode<br>Fast channel turn off<br>Corresponding Channel Fault Register reset |                       |  |  |

|           | 5, 4<br>3, 2                     |             | Diagnostic Current                                                                             | Disabled              |  |  |

|           | 1, 0                             |             | Input Mode<br>Channel Input directed to INx.<br>(reference PWM operation section).             |                       |  |  |

|           |                                  |             | Diagnostic Current                                                                             | Enabled in OFF State. |  |  |

|           |                                  | 10          | ON Mode<br>Channel turned on.                                                                  |                       |  |  |

|           |                                  |             | Diagnostic Current                                                                             | Disabled              |  |  |

|           |                                  | 11          | OFF Mode<br>Channel turned off.8)                                                              |                       |  |  |

#### Table 6. FAULT CONDITIONS

| Output<br>Fault<br>Condition | Fault<br>Memory | Miscellaneous                                                                                                                                                                                                 |

|------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

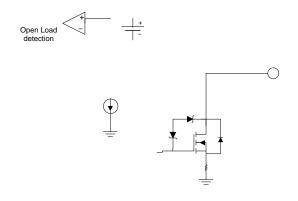

| Open Load                    | Latched         | Detected in Driver Off State (1.75 V [Typ] threshold) when detection is enabled.<br>Reported in Output Fault Diagnostics Register until cleared via the SPI port.<br>Output will maintain turn-on capability. |

| Short to<br>Ground           | Latched         |                                                                                                                                                                                                               |

| SSOP24 NB  |

|------------|

| CASE 565AL |

| ISSUE O    |

DATE 06 JUL 2010

SCALE 1:1

| е  | 0.65 BSC |      |  |  |  |  |  |  |

|----|----------|------|--|--|--|--|--|--|

| h  | 0.22     | 0.50 |  |  |  |  |  |  |

| L  | 0.40     | 1.27 |  |  |  |  |  |  |

| L2 | 0.25     | BSC  |  |  |  |  |  |  |

|    |          |      |  |  |  |  |  |  |

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi