# C 7343

#### Description

The NCV7343 CAN FD transceiver is the interface between a controller area network (CAN) protocol controller and the physical bus. The transceiver provides differential transmit capability to the bus and differential receive capability to the CAN controller.

The NCV7343 is an addition to the CAN high–speed transceiver family complementing NCV734x CAN stand–alone transceivers and previous generations such as AMIS42665, AMIS3066x, etc.

The NCV7343 guarantees additional timing parameters to ensure robust communication at data rates beyond 1 Mbit/s to cope with CAN flexible data rate requirements (CAN FD). These features make the NCV7343 an excellent choice for all types of HS–CAN networks, in nodes that require a low–power mode with wake–up capability via the CAN bus.

### Features

Compliant with International Standard ISO11898-2:2016 CAN FD Timing Specified up to 5 Mbit/s Extended Bus Load Range Standby and Sleep Mode with very Low Current Consumption CAN Wake-up with Wake-up Pattern (WUP), Short CAN Activity Filter Time, Long Wake-up Timeout and Normal Bus Biasing. Local Wake-up V<sub>IO</sub> Pin Allowing Direct Interfacing with 3 V to 5 V MCUs Low Electromagnetic Emission (EME) and High Electromagnetic Susceptibility (EMS) High Impedance Bus Lines in Unpowered State Transmit Data (TxD) Dominant Timeout Function (Long) **Bus Error Detection** Under all Supply Conditions the Chip behaves Predictably ESD Robustness of Bus Pins > 8 kVThermal Protection Bus Pins Short Circuit Proof to Supply Voltage and Ground

Bus Pins Protected against Transients in an Automotive Environment

AEC-Q100 Grade 0 Qualified and PPAP Capable

These are Pb-Free Devices

### Quality

Wettable Flank Package for Enhanced Optical Inspection Typical Applications Automotive

Industrial Networks

SOIC-14 D2 SUFFIX CASE 751A-03

DFNW14 4.5x3, 0.65P MW SUFFIX CASE 507AC

#### MARKING DIAGRAMS

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 21 of this data sheet.

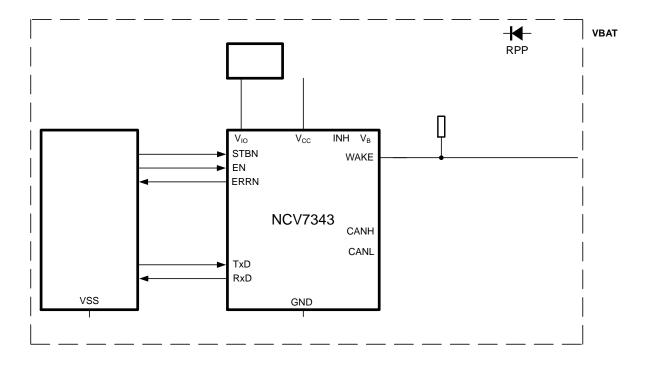

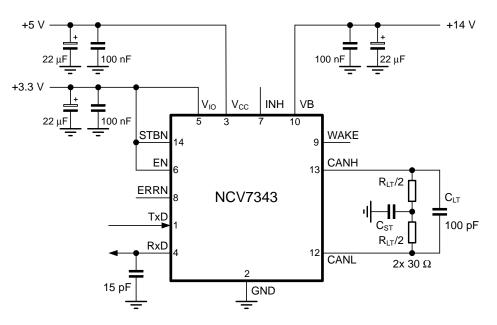

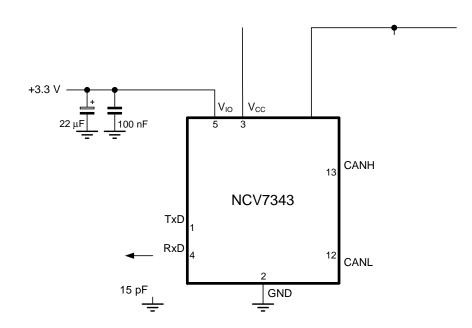

# TYPICAL APPLICATION

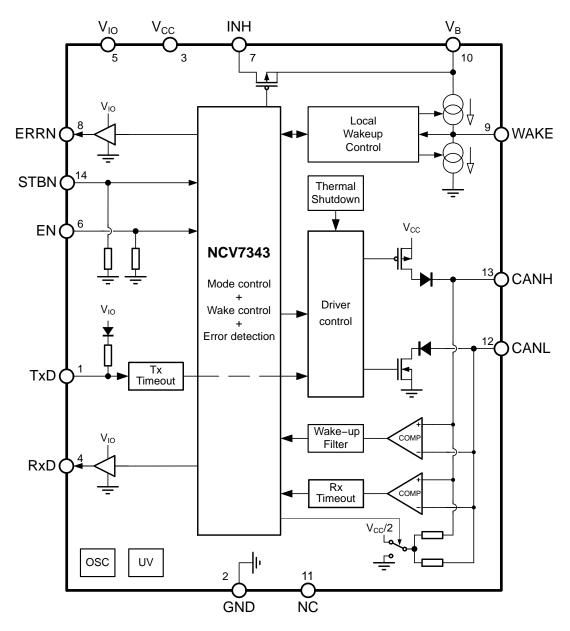

# **BLOCK DIAGRAM**

Figure 2. NCV7343 Block Diagram

# **PIN CONNECTIONS**

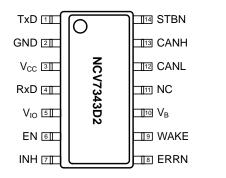

| [1] | [14]              |

|-----|-------------------|

| 2   | [ <sup>13</sup> ] |

| 3]  | [12]              |

| 4   | [11]              |

| 5]  | [10]              |

|     |                   |

|     | : :               |

#### MAXIMUM RATINGS (continued)

| Symbol                                                                                                   | Parameter                                                                                            | Conditions                | Min  | Max  | Unit |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|

| $V_{\text{ESD}_{\text{INT}}}$                                                                            | Electrostatic Discharge Voltage at All Other Pins;<br>Component HBM, According to JEDEC JESD22–A114. | (Note 4)                  | -4   | +4   | kV   |

| $V_{ESD\_CDM}$                                                                                           | Electrostatic Discharge Voltage at All Pins;<br>Component CDM, According to JEDEC JESD22–C101.       |                           | -750 | +750 | V    |

| $V_{\text{ESD}}$ MM                                                                                      | Electrostatic Discharge Voltage at All Pins;<br>Component MM, According to JEDEC JESD22–A115.        | (Note 5)                  | -200 | +200 | V    |

| V <sub>TRAN</sub> Voltage Transients, Pins CANH, CANL.<br>Test Pulses According to ISO7637–2, Class C, ( |                                                                                                      | Test pulses 1             | -100 | -    | V    |

|                                                                                                          | Test Pulses According to ISO7637–2, Class C, (Note 6)                                                | Test pulses 2a            | -    | +75  | V    |

|                                                                                                          |                                                                                                      | Test pulses 3a            | -150 | -    | V    |

|                                                                                                          |                                                                                                      | Test pulses 3b            | -    | +100 | V    |

|                                                                                                          | Voltage Transients, Pin V <sub>B</sub> , According to ISO7637–2                                      | Test pulse 5<br>Load dump | -    | 40   | V    |

| Latch-up                                                                                                 | Static Latch-up at All Pins, According to JEDEC JESD78                                               |                           | -    | 150  | mA   |

| TJ                                                                                                       | Maximum Junction Temperature                                                                         |                           | -40  | +160 | ° C  |

| T <sub>STG</sub>                                                                                         | Storage Temperature                                                                                  |                           | -55  | +150 | ° C  |

| MSL                                                                                                      | Moisture Sensitivity Level                                                                           | SOIC-14                   | :    | 2    |      |

|                                                                                                          |                                                                                                      | DFNW14                    |      | 1    |      |

| T <sub>SLD</sub>                                                                                         | Peak Soldering Temperature (Note 7)                                                                  |                           | -    | 260  | 。C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 2. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 3. Equivalent to discharging a 150 pF capacitor through a 330  $\Omega$  resistor, referenced to GND. WAKE pin stressed through an external series resistor 3.3 k $\Omega$  and with 10 nF capacitor on the module input. VB pin decoupled with 100 nF during stressing. Results were verified by an external test house.

4. Equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  resistor.

5. Equivalent to discharging a 200 pF capacitor through a 10  $\Omega$  resistor and 0.75  $\mu$ H coil.

6. Results were verified by an external test house.

7. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### THERMAL CHARACTERISTICS

| Rating                                                                                                                                     | Symbol                                    | Value     | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------|------|

| Thermal Characteristics, SOIC–14 (Note 8)<br>Thermal Resistance Junction–to–Air, (Note 9)<br>Thermal Resistance Junction–to–Air, (Note 10) | ${f R}_{	heta JA_1} \ {f R}_{	heta JA_2}$ | 100<br>63 | K/W  |

| Thermal Characteristics, DFNW14 (Note 8)<br>Thermal Resistance Junction-to-Air, (Note 9)<br>Thermal Resistance Junction-to-Air, (Note 10)  | R <sub>θJA_1</sub><br>R <sub>θJA_2</sub>  | 115<br>65 | K/W  |

8. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

9. Test board according to EIA/JEDEC Standard JESD51-3 (1S0P PCB), signal layer with 10% trace coverage.

10. Test board according to EIA/JEDEC Standard JESD51-7 (2S2P PCB), signal layers with 10% trace coverage.

#### **RECOMMENDED OPERATING RANGES**

| Symbol                        | Parameter                            | Conditions | Min | Max             | Unit |

|-------------------------------|--------------------------------------|------------|-----|-----------------|------|

| V <sub>B</sub>                | Supply Voltage, Pin V <sub>B</sub>   |            | 5.0 | 40              | V    |

| V <sub>CC</sub>               | Supply Voltage, Pin V <sub>CC</sub>  |            | 4.5 | 5.5             | V    |

| V <sub>IO</sub>               | Supply Voltage, Pin V <sub>IO</sub>  |            | 2.8 | 5.5             | V    |

| V <sub>CAN</sub>              | DC Voltage at Pins CANH and CANL     |            | -36 | 36              | V    |

| V <sub>DIG_IN</sub>           | DC Voltage at Pins TxD, STBN, and EN |            | 0   | 5.5             | V    |

| V <sub>DIG_OUT</sub>          | DC Voltage at Pins RxD and ERRN      |            | 0   | V <sub>IO</sub> | V    |

| V <sub>INH, 27.2835</sub> 0 m | o¢urନିର୍ଦ୍ଧେମାଶ୍ରେମ୍ଭକ୍ୟାPin INH     | -          | -   | -               | -    |

# RECOMMENDED OPERATING RANGES (continued)

| Symbol            | Parameter              | Conditions | Min | Max | Unit |

|-------------------|------------------------|------------|-----|-----|------|

| V <sub>WAKE</sub> | DC Voltage at Pin WAKE |            | -42 | VB  | V    |

| TJ                | Junction Temperature   |            | -40 | 150 | ° C  |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 4.5 V to 5.5 V;  $V_{IO}$  = 2.8 V to 5.5 V;  $V_{B}$ = 5.0 V to 40 V; for typical values  $T_A$  = 25 C, for min/max values  $T_J$  = -40 to +150 C;  $R_{LT}$  = 60  $\Omega$ ,  $C_{RxD}$  = 15 pF; unless otherwise noted. All voltages are referenced to GND (pin 2). Positive current flow into the respective pin) (continued)

| Symbol                   | Parameter                            | Conditions                                                                                                                     | Min                     | Тур                      | Max                     | Unit |

|--------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------|------|

| V <sub>B</sub> SUPPLY VO | LTAGE (Pin V <sub>B</sub> )          |                                                                                                                                |                         |                          |                         |      |

| V <sub>uvd_VB</sub>      | Undervoltage Detection<br>Threshold  | V <sub>B</sub> falling                                                                                                         | 3.7                     | 4.1                      | 4.5                     | V    |

| V <sub>uvr_VB</sub>      | Undervoltage Recovery<br>Threshold   | V <sub>B</sub> rising                                                                                                          | 3.9                     | 4.4                      | 4.9                     | V    |

| $V_{uvh\_VB}$            | Undervoltage Threshold<br>Hysteresis |                                                                                                                                | 100                     | 300                      | 400                     | mV   |

| TRANSMITTER              | DATA INPUT (PIN TxD)                 | -                                                                                                                              |                         |                          |                         |      |

| V <sub>IH</sub>          | High-level Input Voltage             | Output recessive                                                                                                               | 2.0                     | _                        | -                       | V    |

| V <sub>IL</sub>          | Low-level Input Voltage              | Output dominant                                                                                                                | -                       | -                        | 0.8                     | V    |

| IIH                      | High-level Input Current             | V <sub>TxD</sub> = V <sub>IO</sub>                                                                                             | -5.0                    | 0                        | +5.0                    | μA   |

| R <sub>PU</sub>          | Pull–up Resistor                     |                                                                                                                                | 10                      | 25                       | 50                      | kΩ   |

| I <sub>LEAK</sub>        | Leakage Current                      | V <sub>TxD</sub> = 5.5 V, V <sub>IO</sub> = 0 V                                                                                | -1.0                    | 0                        | +1.0                    | μA   |

| Ci                       | Input Capacitance                    | (Note 11)                                                                                                                      | -                       | 5                        | 10                      | pF   |

| RECEIVER DAT             | A OUTPUT (Pin RxD)                   |                                                                                                                                | -                       |                          | -                       | -    |

| I <sub>OH</sub>          | High-level Output Current            | $V_{RxD} = V_{IO} - 0.4 V$                                                                                                     | -8.0                    | -3.0                     | -1.0                    | mA   |

| I <sub>OL</sub>          | Low-level Output Current             | $V_{RxD} = 0.4 V$                                                                                                              | 1.0                     | 6.0                      | 12                      | mA   |

| TRANSMITTER              | MODE SELECT (Pin STBN, EN)           |                                                                                                                                | -                       |                          | -                       | -    |

| V <sub>IH</sub>          | High-level Input Voltage             | Standby mode                                                                                                                   | 2.0                     | -                        | -                       | V    |

| V <sub>IL</sub>          | Low-level Input Voltage              | Normal mode                                                                                                                    | -                       | -                        | 0.8                     | V    |

| R <sub>PD</sub>          | Pull-down Resistor                   |                                                                                                                                | 300                     | 650                      | 1000                    | kΩ   |

| IIL                      | Low-level Input Current              | V <sub>STBN</sub> = 0 V                                                                                                        | -1.0                    | 0                        | +1.0                    | μA   |

| I <sub>LEAK</sub>        | Leakage Current                      | $V_{STBN}$ = 5.5 V, $V_B$ = $V_{CC}$ = $V_{IO}$ = 0 V                                                                          | -1.0                    | 0                        | +1.0                    | μA   |

| C <sub>i</sub>           | Input Capacitance                    | (Note 11)                                                                                                                      | -                       | 5                        | 10                      | pF   |

| ERROR SIGNA              | LING (Pin ERRN)                      | -                                                                                                                              |                         |                          |                         |      |

| I <sub>OH</sub>          | High Level Output Current            | $V_{ERRN} = V_{IO} - 0.4 V$                                                                                                    | -100                    | -50                      | -10                     | μA   |

| I <sub>OL</sub>          | Low Level Output Current             | $V_{ERRN} = 0.4 V$                                                                                                             | 0.1                     | 0.5                      | 1.0                     | mA   |

| LOCAL WAKE-              | UP INPUT (Pin WAKE)                  |                                                                                                                                |                         |                          |                         |      |

| V <sub>IH</sub>          | High-level Input Voltage             | Standby or Sleep                                                                                                               | V <sub>B</sub> – 2      | _                        | -                       | V    |

| V <sub>IL</sub>          | Low-level Input Voltage              | Standby or Sleep                                                                                                               | -                       | _                        | V <sub>B</sub> – 4      | V    |

| liH                      | High-level Input Current             | $ \begin{array}{l} V_{WAKE} = V_B - 2 \ V; \\ V_{WAKE} = High \ for \ t \geq t_{wake_filt} \\ (Pull-up \ active) \end{array} $ | -11                     | _                        | -3.0                    | μA   |

| IIL                      | Low-level Input Current              | $V_{WAKE} = V_B - 4 V;$<br>$V_{WAKE} = Low \text{ for } t \ge t_{wake_filt}$<br>(Pull-down active)                             | 3.0                     | -                        | 11                      | μΑ   |

| INHIBIT OUTPU            | JT (Pin INH)                         |                                                                                                                                | -                       |                          | -                       | -    |

| V <sub>OH</sub>          | High-level Output Voltage            | I <sub>INH</sub> = -1 mA                                                                                                       | V <sub>B</sub> –<br>0.6 | V <sub>B</sub> –<br>0.27 | V <sub>B</sub> –<br>0.1 | V    |

| ILEA                     | ge Current                           | Sleep or Power–off mode, $V_{INH} = 0 V$                                                                                       | -5                      | 0                        | +5                      | μA   |

| CAN                      | s CANH and CANL)                     | -                                                                                                                              |                         |                          | •                       |      |

| Vo(doin)(CANIT)          | ant Output Voltage at Pin<br>CANH    | Normal mode; $V_{TxD}$ = Low;<br>t < t <sub>dom(TxD)</sub> ; 45 $\Omega \leq R_{LT} \leq 65 \Omega t$                          | 2.75                    | 3.65                     | 4.5                     |      |

|                          |                                      |                                                                                                                                |                         |                          | -                       |      |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 4.5 V to 5.5 V;  $V_{IO}$  = 2.8 V to 5.5 V;  $V_{B}$ = 5.0 V to 40 V; for typical values  $T_A$  = 25 C, for min/max values  $T_J$  = -40 to +150 C;  $R_{LT}$  = 60  $\Omega$ ,  $C_{RxD}$  = 15 pF; unless otherwise noted. All voltages are referenced to GND (pin 2). Positive current flow into the respective pin) (continued)

| Symbol                      | Parameter                                                                            | Conditions                                                                                                                             | Min                | Тур      | Max       | Unit     |

|-----------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|-----------|----------|

| CAN TRANSMITT               | ER (Pins CANH and CANL)                                                              |                                                                                                                                        |                    |          | -         |          |

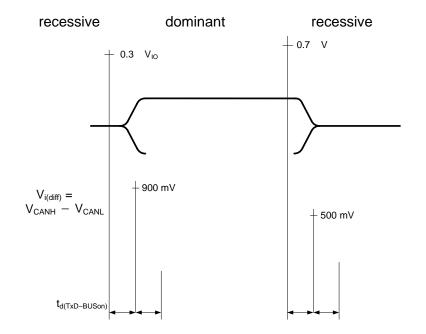

| V <sub>o(dom)(CANL)</sub>   | Dominant Output Voltage at Pin<br>CANL                                               | Normal mode; $V_{TxD}$ Low;<br>t < t <sub>dom(TxD)</sub> ; 45 $\Omega$ R <sub>LT</sub> 65 $\Omega$                                     | 0.5                | 1.35     | 2.25      | V        |

| V <sub>o(rec)</sub>         | Recessive Output Voltage at Pins<br>CANH and CANL                                    | Normal or Silent mode;<br>$V_{TxD}$ = High<br>or $V_{TxD}$ = Low and t > t <sub>dom(TxD)</sub> ;<br>no load                            | 2.0                | 2.5      | 3.0       | V        |

| V <sub>o(off)</sub>         | Recessive Output Voltage at Pins<br>CANH and CANL                                    | Standby or Sleep mode;<br>no load                                                                                                      | -0.1               | 0        | +0.1      | V        |

| V <sub>o(dom)(diff)</sub>   | Differential Dominant Output<br>Voltage<br>(V <sub>CANH</sub> – V <sub>CANL</sub> )  | Normal mode; $V_{TxD} = Low;$<br>t < t <sub>dom(TxD)</sub> ; 50 $\Omega = R_{LT} = 65 \Omega$                                          | 1.5                | 2.3      | 3.0       | V        |

| V <sub>o(dom)(diff)_E</sub> |                                                                                      | Normal mode; $V_{TxD} = Low;$<br>t < t <sub>dom(TxD</sub> ); 45 $\Omega = R_{LT} = 70 \Omega$                                          | 1.4                | 2.3      | 3.3       | V        |

| $V_{o(dom)(diff)\_ARB}$     |                                                                                      | Normal mode; $V_{TxD}$ = Low;<br>t < t <sub>dom(TxD)</sub> ; R <sub>LT</sub> = 2 240 $\Omega$                                          | 1.5                | -        | 5.0       | V        |

| V <sub>o(rec)(diff)</sub>   | Differential Recessive Output<br>Voltage<br>(V <sub>CANH</sub> – V <sub>CANL</sub> ) | Normal or Silent mode;<br>$V_{TxD}$ = High<br>or $V_{TxD}$ = Low and t > t <sub>dom(TxD)</sub> ;<br>no load;r90707 refq415.2193 71.717 | –50<br>.90707 r45W | nBT/F2Tc | :(CANH)Tj | 8 0 0070 |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 4.5 V to 5.5 V;  $V_{IO}$  = 2.8 V to 5.5 V;  $V_{B}$ = 5.0 V to 40 V; for typical values T<sub>A</sub> = 25 C, for min/max values T<sub>J</sub> = -40 to +150 C; R<sub>LT</sub> = 60  $\Omega$ , C<sub>RxD</sub> = 15 pF; unless otherwise noted. All voltages are referenced to GND (pin 2). Positive current flow into the respective pin) (continued)

| Symbol      Parameter      Conditions      Min      Typ      Max | Unit |

|------------------------------------------------------------------|------|

|------------------------------------------------------------------|------|

272.8063 rem.0041

#### FUNCTIONAL DESCRIPTION

#### POWER SUPPLY

#### V<sub>B</sub> Supply Pin

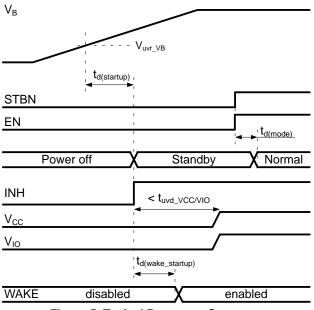

$V_B$  is the main supply pin of the NCV7343. The NCV7343 proceeds from Power–off mode to Standby mode as soon as the  $V_B$  supply is available. This supply input is used to provide the minimum power required for the operation in case of absence of the remaining supplies. Typically this is the only active supply in a low–power Sleep mode providing power supply to the low–power wake–up detector.

### V<sub>CC</sub> Supply Pin

$V_{\mbox{\scriptsize CC}}$  pin is the CAN transceiver main supply input in Normal and Silent mode.

#### VIO Supply Pin

Digital pins interfacing with the microcontroller have a separate IO supply. The  $V_{IO}$  pin should be connected to microcontroller supply pin. By using  $V_{IO}$  supply pin shared with microcontroller the IO levels between microcontroller and transceiver are properly adjusted. See Figure 1.

Figure 5. Typical Power-up Sequence

#### **Power Supplies Monitoring**

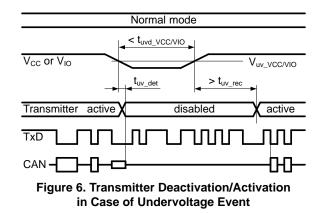

$V_{B}$ ,  $V_{CC}$  and  $V_{IO}$  supply inputs are monitored by undervoltage detectors with individual thresholds and filtering times both for undervoltage detection and undervoltage recovery. In Normal mode, the transmitter is disabled  $t_{uv\_det}$  after  $V_{CC}$  or  $V_{IO}$  voltage falls below respective undervoltage detection thresholds. The transmitter is re–enabled  $t_{uv\_rec}$  after both  $V_{CC}$  and  $V_{IO}$  voltage rises above the undervoltage recovery thresholds (Figure 6).

$V_B$  undervoltage is detected if  $V_B$  supply voltage falls below undervoltage detection threshold,  $V_{uvd_VB}$ .  $V_B$ undervoltage recovery is detected if  $V_B$  supply voltage rises above the undervoltage recovery threshold,  $V_{uvr_VB}$ .

$V_{CC}$  undervoltage flag is set if  $V_{CC}$  supply voltage is lower than  $V_{uv\_VCC}$  for longer than  $V_{CC}$  undervoltage detection time  $t_{uvd\_VCC}$ .  $V_{CC}$  undervoltage recovery is detected and the flag is reset if  $V_{CC}$  supply voltage is higher than  $V_{uv\_VCC}$  for longer than  $V_{CC}$  undervoltage recovery time  $t_{uvr\_VCC}$ .

Similarly,  $V_{IO}$  undervoltage flag is set if  $V_{IO}$  supply voltage is lower than  $V_{uv\_VIO}$  for longer than  $V_{IO}$  undervoltage detection time  $t_{uvd\_VIO}$ .  $V_{IO}$  undervoltage recovery is detected and the flag is reset if  $V_{IO}$  supply voltage is higher than  $V_{uv\_VIO}$  for longer than  $V_{IO}$  undervoltage recovery time  $t_{uvr\_VIO}$ .

Both  $V_{CC}$  and  $V_{IO}$  undervoltage flags and the undervoltage detection timers are also reset after local or remote wake–up detection event or STBN pin rising edge detection in Sleep mode.

Once the  $V_{CC}$  and/or  $V_{IO}$  undervoltage flag is set the device changes to Sleep mode. The Sleep mode can be left and the operation mode control by STBN and EN pin is re–enabled as soon as both  $V_{CC}$  and  $V_{IO}$  supplies are recovered. The operating mode control state machine is not reset when an undervoltage condition is detected. Thus if Sleep mode was requested by the host prior to  $V_{CC}$  and/or  $V_{IO}$  undervoltage condition detection and the EN pin was set Low in Sleep mode, the device stays in Sleep once the undervoltage is recovered, although STBN and EN pins are both set Low, which is otherwise considered a Standby mode request.

### INH Pin

The INH output pin is a high–voltage high–side switch to  $V_B$  supply. It can be used to control the  $V_{CC}$  or  $V_{IO}$  external supply voltage regulators. The output is switched high in all operating modes except for the Sleep mode. In Sleep mode the pin is left floating (high–impedance) which can be used to deactivate the external regulators in order to minimize the ECU current consumption. The INH switch is also deactivated in Power–off mode.

### HIGH SPEED CAN TRANSCEIVER

NCV7343 implements high–speed physical layer CAN FD transceiver compatible with ISO11898–2:2016, implementing following optional features or alternatives:

Extended bus load range

Transmit dominant timeout, long

Support of bit rates up to 5 Mbit/s

Low–power modes with wake–up via wake–up pattern, Short CAN activity filter time and long wake–up

Figure 11. Operation Modes

# WAKE-UP

A Wake-up flag is set if Local wake-up via WAKE pin (positive or negative edge) is detected or Remote wake-up via bus (wake-up pattern) is detected. If the Wake-up flag is set in Sleep mode, the device changes to Standby mode. Undervoltage detection flags are cleared and the corresponding timers are restarted upon detection

#### FAILURE DETECTION Local Failures

A Local failure flag is set if any of the flowing flags are set:

TxD Dominant Timeout Bus Dominant Timeout Short–TxD to RxD Overtemperature Detection

The local failure flag is signaled on ERRN pin in Silent mode entered from Normal mode. The flag is cleared if all of the mentioned flags are cleared.

### TxD Dominant Timeout

A TxD dominant timeout timer circuit prevents the bus lines being driven to a permanent dominant state if pin TxD is forced permanently low. The timer is triggered by a negative edge on pin TxD in Normal mode. If the duration

### INTERNAL FLAGS AND THEIR VISIBILITY

| Internal Flag                                   | Set Conditions                                                                                | Reset Conditions                                                                                               | Visibility on ERRN Pin |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|

| V <sub>CC</sub> or V <sub>IO</sub> Undervoltage | $V_{CC} < V_{uv_VCC}$ for t > $t_{uvd_VCC}$ or<br>$V_{IO} < V_{uv_VIO}$ for t > $t_{uvd_VIO}$ | $(V_{CC} > V_{uv\_VCC} \text{ for } t > t_{uvr\_VCC}$ and $V_{IO} > V_{uv\_VIO} \text{ for } t > t_{uvr\_VIO}$ |                        |

### FAIL SAFE

A current–limiting circuit protects the transmitter output stage from damage caused by accidental short circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

Undervoltage on supply pins prevents the chip from sending data on the bus when there is not enough  $V_{CC}$  supply voltage to build required bus differential voltage, or when  $V_{IO}$  supply voltage is low and thus the digital input or output signals might be interpreted falsely. After supply is recovered TxD pin must be first released to High to allow sending dominant bits again.

The pins CANH and CANL are protected from automotive electrical transients (according to ISO 7637; see Figure 19). Pin TxD is pulled high and pins STBN and EN are pulled low internally should the input become disconnected. Digital pins, TxD, STBN and EN will be floating, preventing reverse supply should the  $V_{IO}$  supply be removed. RxD and ERRN have forward diode to  $V_{IO}$  supply.

# MEASUREMENT SETUPS AND DEFINITIONS

Figure 18. Test Circuit for Timing Characteristics

# ISO 11898-2:2016 PARAMETER CROSS-REFERENCE TABLE (continued)

| Parameter                                                                                     | Notation                                 | Symbol                               |

|-----------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------|

| DATA SIGNAL TIMING REQUIREMENTS FOR USE WITH BIT RATES ABOVE 2 N                              | lbit/s AND UP TO 5 Mbit/s                | 5                                    |

| Transmitted Recessive Bit Width @ 5 Mbit/s                                                    | t <sub>Bit(Bus)</sub>                    | t <sub>bit(Vi(diff))</sub>           |

| Received Recessive Bit Width @ 5 Mbit/s                                                       | t <sub>Bit(RXD)</sub>                    | t <sub>bit(RxD)</sub>                |

| Receiver Timing Symmetry @ 5 Mbit/s                                                           | $\Delta t_{Rec}$                         | $\Delta t_{rec}$                     |

| MAXIMUM RATINGS OF V <sub>CAN_H</sub> , V <sub>CAN_L</sub> AND V <sub>Diff</sub>              |                                          | ·                                    |

| Maximum Rating V <sub>Diff</sub>                                                              | V <sub>Diff</sub>                        | V <sub>Diff</sub>                    |

| General Maximum Rating $V_{\mbox{CAN}_{\mbox{H}}}$ and $V_{\mbox{CAN}_{\mbox{L}}}$            | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub> | V <sub>CAN</sub><br>V <sub>CAN</sub> |

| Optional: Extended Maximum Rating $V_{\mbox{CAN}_{\mbox{H}}}$ and $V_{\mbox{CAN}_{\mbox{L}}}$ | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub> | NA                                   |

| MAXIMUM LEAKAGE CURRENTS ON CAN_H and CAN_L, UNPOWERED                                        |                                          | •                                    |

| Leakage Current on CAN_H, CAN_L                                                               | I <sub>CAN_H</sub><br>I <sub>CAN_L</sub> | I <sub>LEAK(off)</sub>               |

| BUS BIASING CONTROL TIMINGS                                                                   |                                          |                                      |

| CAN Activity Filter Time, Long                                                                | t <sub>Filter</sub>                      | NA                                   |

| CAN Activity Filter Time, Short                                                               | t <sub>Filter</sub>                      | t <sub>wup_filt</sub>                |

| Wake-up Timeout, Short                                                                        | t <sub>Wake</sub>                        | NA                                   |

| Wake-up Timeout, Long                                                                         | t <sub>Wake</sub>                        | t <sub>wup_to</sub>                  |

| Timeout for Bus Inactivity (Required for Selective Wake-up Implementation Only)               | t <sub>Silence</sub>                     | NA                                   |

| Bus Bias Reaction Time (Required for Selective Wake-up Implementation Only)                   | t <sub>Bias</sub>                        | NA                                   |

### Table 1. ORDERING INFORMATION

| Part Number   | Description                                                                          | Package                               | Shipping <sup>†</sup> |

|---------------|--------------------------------------------------------------------------------------|---------------------------------------|-----------------------|

| NCV7343D20R2G | CAN FD Transceiver, High Speed, Low<br>Power, with WAKE, INH and V <sub>IO</sub> Pin | SOIC-14<br>(Pb-free)                  | 3000 / Tape & Reel    |

| NCV7343MW0R2G | CAN FD Transceiver, High Speed, Low<br>Power, with WAKE, INH and V <sub>IO</sub> Pin | DFNW14<br>Wettable Flank<br>(Pb–free) | 5000 / Tape & Reel    |

| NCV7343D21R2G | CAN FD Transceiver, High Speed, Low<br>Power, with WAKE, INH and V <sub>IO</sub>     |                                       |                       |

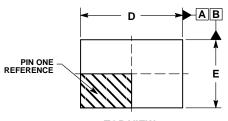

### PACKAGE DIMENSIONS

SOIC-14 NB CASE 751A-03 ISSUE L

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

5. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

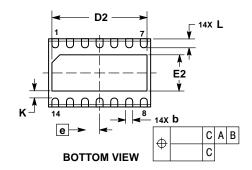

### PACKAGE DIMENSIONS

#### DFNW14 4.5x3, 0.65P CASE 507AC **ISSUE D**

- NOTES:

DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMESNION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

THIS DEVICE CONTAINS WETTABLE FLANK DESIGN FEATURES TO AID IN FILLET FOR-MATION ON THE LEADS DURING MOUNTING.

**SOLDERING FOOTPRINT\***

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.