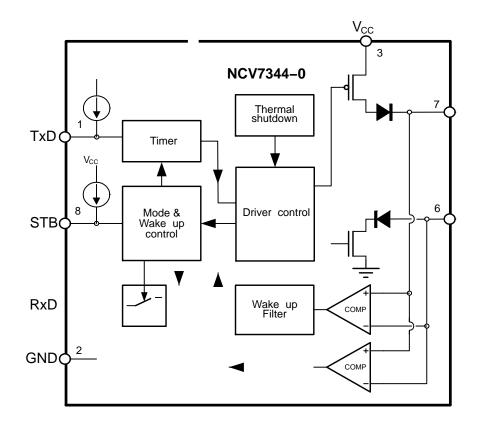

### **BLOCK DIAGRAM**

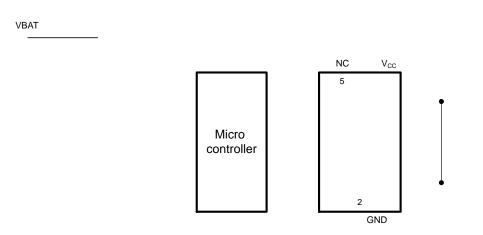

### **TYPICAL APPLICATION**

### **ELECTRICAL CHARACTERISTICS**

#### Definitions

All voltages are referenced to GND (pin 2). Positive currents flow into the IC. Sinking current means the current

is flowing into the pin; sourcing current means the current is flowing out of the pin.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3. ABSOLUTE MAXIMUM RATINGS

|   | Symbol            | Parameter                                        | Conditions                            | Min | Max | Unit |

|---|-------------------|--------------------------------------------------|---------------------------------------|-----|-----|------|

|   | V <sub>SUP</sub>  | Supply voltage V <sub>CC</sub> , V <sub>IO</sub> |                                       | 0.3 | +6  | V    |

| Γ | V <sub>CANH</sub> | DC voltage at pin CANH                           | $0 < V_{CC} < 5.25 V$ ; no time limit |     |     |      |

| <b>Table 5. ELECTRICAL CHARACTERISTICS</b> $V_{CC} = 4.75$ V to 5.25 V; $V_{IO} = 2.8$ to 5.25 V; $T_J = -40$ to $+150^{\circ}$ C; $R_{LT} = 60 \Omega$ , |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $C_{LT}$ = 100 pF, $C_1$ not used, $C_{RxD}$ = 15 pF unless specified otherwise.                                                                          |  |

| Symbol                         | Parameter                                                                 | Conditions                                                                                                      | Min  | Тур | Max | Unit |  |

|--------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|-----|-----|------|--|

| BUS LINES (Pins CANH and CANL) |                                                                           |                                                                                                                 |      |     |     |      |  |

| V <sub>o(off)</sub> (CANL)     | Recessive output voltage at pin CANL                                      | Standby mode; $R_{LT}$ and $C_{LT}$ not used                                                                    | 0.1  | 0   | 0.1 | V    |  |

| V <sub>o(off)(diff)</sub>      | Differential bus output voltage<br>(V <sub>CANH</sub> V <sub>CANL</sub> ) | Standby mode; $R_{LT}$ and $C_{LT}$ not used                                                                    | 0.2  | 0   | 0.2 | V    |  |

| V <sub>o(dom)</sub> (CANH)     | Dominant output voltage at pin CANH                                       | $ \begin{array}{l} V_{TxD} = 0 \; V; \; t < t_{dom(TxD);} \\ 50 \; \Omega < R_{LT} < 65 \; \Omega \end{array} $ | 2.75 | 3.5 | 4.5 | V    |  |

| V <sub>o(dom)</sub> (CANL)     | Dominant output voltage at pin CANL                                       | $V_{TxD} = 0 V; t < t_{dom(TxD)};$<br>50 $\Omega < R_{LT} <$                                                    | -    |     | •   | -    |  |

| Table 5. ELECTRICAL CHARACTERISTICS V <sub>CC</sub> = 4.75 V to 5.25 V; V <sub>IO</sub> = 2.8 to 5.25 V; T <sub>J</sub> = 40 to +150°C; R <sub>LT</sub> = 60 $\Omega$ , |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $C_{LT}$ = 100 pF, $C_1$ not used, $C_{RxD}$ = 15 pF unless specified otherwise.                                                                                        |  |

| Symbol                                       | Parameter                                                       | Conditions                          | Min  | Тур | Max | Unit |  |

|----------------------------------------------|-----------------------------------------------------------------|-------------------------------------|------|-----|-----|------|--|

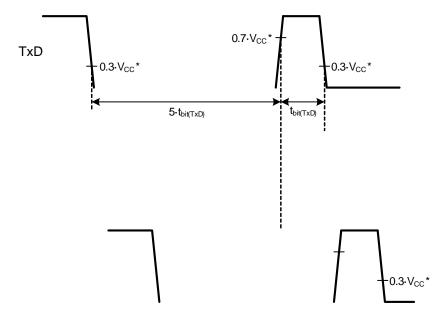

| TIMING CHARACTERISTICS (see Figures 6 and 8) |                                                                 |                                     |      |     |     |      |  |

| t <sub>d(TxD BUSon)</sub>                    | Delay TxD to bus active                                         |                                     |      | 75  |     | ns   |  |

| t <sub>d(TxD BUSoff)</sub>                   | Delay TxD to bus inactive                                       |                                     |      | 85  |     | ns   |  |

| t <sub>d(BUSon</sub> RxD)                    | Delay bus active to RxD                                         |                                     |      | 24  |     | ns   |  |

| t <sub>d(BUSoff RxD)</sub>                   | Delay bus inactive to RxD                                       |                                     |      | 32  |     | ns   |  |

| t <sub>pd_dr</sub>                           | Propagation delay TxD to RxD dominant to recessive transition   |                                     | 50   | 100 | 210 | ns   |  |

| t <sub>pd_rd</sub>                           | Propagation delay TxD to RxD recessive to dominant transition   |                                     | 50   | 120 | 210 | ns   |  |

| t <sub>d(stb nm)</sub>                       | Delay standby mode to normal mode                               |                                     | 5    | 11  | 20  | μs   |  |

| twake_filt                                   | Filter time for wake up via bus                                 | NCV7344 version                     | 0.5  |     | 5   | μs   |  |

|                                              |                                                                 | NCV7344A version                    | 0.15 |     | 1.8 | μs   |  |

| t <sub>dwakerd</sub>                         | Delay to flag wake event<br>(recessive to dominant transitions) | Valid bus wake up event             | 0.5  | 2.6 | 6   | μs   |  |

| <sup>t</sup> dwakedr                         | Delay to flag wake event<br>(dominant to recessive transitions) | Valid bus wake up event             | 0.5  | 2.6 | 6   | μs   |  |

| t <sub>wake_to</sub>                         | Bus time for wake up timeout                                    | Standby mode                        | 1    |     | 10  | ms   |  |

| t <sub>dom(TxD)</sub>                        | TxD dominant time for timeout                                   | V <sub>TxD</sub> = Low; Normal mode | 1    |     | 10  | ms   |  |

| t <sub>Bit(RxD)</sub>                        | Bit time on RxD pin                                             | t <sub>Bit(TxD)</sub> = 500 ns      | 400  |     | 550 | ns   |  |

|                                              |                                                                 | t <sub>Bit(TxD)</sub> = 200 ns      | 120  |     | 220 | ns   |  |

| t <sub>Bit(Vi(diff))</sub>                   | Bit time on bus (CANH – CANL pin)                               | t <sub>Bit(TxD)</sub> = 500 ns      | •    | •   | •   | •    |  |

## MEASUREMENT SETUPS AND DEFINITIONS

#### Table 6. ISO 11898–2:2016 Parameter Cross–Reference Table

| ISO 11898–2:2016 Specification                                                   |                                          | NCV7344<br>Datasheet                                 |

|----------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------|

| Parameter                                                                        | Notation                                 | Symbol                                               |

| Dominant output characteristics                                                  |                                          |                                                      |

| Single ended voltage on CAN_H                                                    | V <sub>CAN_H</sub>                       | V <sub>o(dom)</sub> (CANH)                           |

| Single ended voltage on CAN_L                                                    | V <sub>CAN_L</sub>                       | V <sub>o(dom)(CANL)</sub>                            |

| Differential voltage on normal bus load                                          | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)</sub>                            |

| Differential voltage on effective resistance during arbitration                  | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)_arb</sub>                        |

| Differential voltage on extended bus load range (optional)                       | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)</sub>                            |

| Driver symmetry                                                                  |                                          |                                                      |

| Driver symmetry                                                                  | V <sub>SYM</sub>                         | V <sub>o(dom)(sym)</sub>                             |

| Driver output current                                                            |                                          |                                                      |

| Absolute current on CAN_H                                                        | I <sub>CAN_H</sub>                       | I <sub>o(SC)(CANH)</sub>                             |

| Absolute current on CAN_L                                                        | I <sub>CAN_L</sub>                       | I <sub>o(SC)(CANL)</sub>                             |

| Receiver output characteristics, bus biasing active                              | ·                                        | -                                                    |

| Single ended output voltage on CAN_H                                             | V <sub>CAN_H</sub>                       | V <sub>o(rec)(CANH)</sub>                            |

| Single ended output voltage on CAN_L                                             | V <sub>CAN_L</sub>                       | V <sub>o(rec)(CANL)</sub>                            |

| Differential output voltage                                                      | V <sub>Diff</sub>                        | V <sub>o(rec)(diff)</sub>                            |

| Receiver output characteristics, bus biasing inactive                            |                                          |                                                      |

| Single ended output voltage on CAN_H                                             | V <sub>CAN_H</sub>                       | V <sub>o(off)(CANH)</sub>                            |

| Single ended output voltage on CAN_L                                             | V <sub>CAN_L</sub>                       | V <sub>o(off)(CANL)</sub>                            |

| Differential output voltage                                                      | V <sub>Diff</sub>                        | V <sub>o(off)(diff)</sub>                            |

| Optional transmit dominant timeout                                               |                                          |                                                      |

| Transmit dominant timeout, long                                                  | t <sub>dom</sub>                         | t <sub>dom(TxD)</sub>                                |

| Transmit dominant timeout, short                                                 | t <sub>dom</sub>                         | NA                                                   |

| Static receiver input characteristics, bus biasing active                        | l                                        |                                                      |

| Recessive state differential input voltage range                                 | V <sub>Diff</sub>                        | V <sub>i(rec)(diff)_NM</sub>                         |

| Dominant state differential input voltage range                                  | V <sub>Diff</sub>                        | V <sub>i(dom)(diff)_NM</sub>                         |

| Static receiver input characteristics, bus biasing inactive                      | l                                        |                                                      |

| Recessive state differential input voltage range                                 | V <sub>Diff</sub>                        | V <sub>i(rec)(diff)_LP</sub>                         |

| Dominant state differential input voltage range                                  | V <sub>Diff</sub>                        | V <sub>i(dom)(diff)_LP</sub>                         |

| Receiver input resistance                                                        |                                          |                                                      |

| Differential internal resistance                                                 | R <sub>Diff</sub>                        | R <sub>i(diff)</sub>                                 |

| Single ended internal resistance                                                 | R <sub>CAN_H</sub><br>R <sub>CAN_L</sub> | R <sub>i(cm)(CANH)</sub><br>R <sub>i(cm)(CANL)</sub> |

| Receiver input resistance matching                                               |                                          |                                                      |

| Matching a of internal resistance                                                | m <sub>R</sub>                           | R <sub>i(cm)(m)</sub>                                |

| Implementation loop delay requirement                                            | I                                        |                                                      |

| Loop delay                                                                       | t <sub>Loop</sub>                        | t <sub>pd_rd</sub><br>t <sub>pd_dr</sub>             |

| Optional implementation data signal timing requirements for use with bit rates a | above 1 Mbit/s and up to 2               | Mbit/s                                               |

| Transmitted recessive bit width @ 2 Mbit/s                                       | t <sub>Bit(Bus)</sub>                    | t <sub>Bit(Vi(diff))</sub>                           |

| Received recessive bit width @ 2 Mbit/s                                          | t <sub>Bit(RXD)</sub>                    | t <sub>Bit(RxD)</sub>                                |

#### Table 6. ISO 11898-2:2016 Parameter Cross-Reference Table

| Parameter                           | Notation | Symbol          |

|-------------------------------------|----------|-----------------|

| Receiver timing symmetry @ 2 Mbit/s |          | $\Delta_{tRec}$ |

DATE 02 JUL 2021

A

#### GENERIC MARKING DIAGRAM\*

<--D2--►

1 OXXXXXX XXXXXX ALYW•

XXXXXX = Specific Device Code

- A = Assembly Location

- L = Wafer Lot

.

Y = Year

W = Work Week

= Pb–Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

DATE 16 FEB 2011

SEATING PLANE

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi