# A omo E 10BA E- 1 M D o

# NC 7410

### Description

The NCV7410 device is an IEEE 802.3cg-compliant Ethernet Transceiver with an integrated Media Access Controller (MAC-PHY).

The NCV7410 can communicate with multiple nodes connected to a shared medium (UTP) at 10 Mbps. It consists of CSMA/CD MAC and PHY with Physical Layer Collision Avoidance (PLCA). PLCA prevents collisions at the physical layer and, therefore, improves the throughput of CSMA/CD. The NCV7410 uses SPI (with a clock up to 25 MHz) as an interface to host MCU.

### **Features**

- Compliant to IEEE 802.3cg 2019

- Supports Half-Duplex, Multidrop Mode

- Physical Layer Collision Avoidance (PLCA)

- SPI Interface (OPEN Alliance 10BASE-T1x MAC-PHY Serial Interface)

- Distance Measurement between Nodes

- Single 3.3 V Supply Operation

- Transmitter Optimized for Capacitive Coupling to UTP Cable

- MDI Pins Protected against:

- ◆ ±6 kV ESD (HBM, IEC61000-4-2)

- ◆ Transient Pulses (ISO7637)

- Operating Ambient Temperature –40°C to +125°C (T<sub>AMB\_Class1</sub>)

- Junction Temperature Range -40°C to +150°C

### **Environment**

• These are Pb-Free Devices

### **Typical Applications**

- Automotive

- Agricultural Machinery

- Machine Control

### Quality

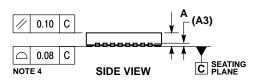

- Wettable Flank Package for Enhanced Optical Inspection

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

1

### **MARKING DIAGRAM**

V7410 = Specific Device Code A = Assembly Location WL = Wafer Lot

= Pb-Free Package

YY = Year WW = Work Week

### ORDERw[881.85(4) INF¥i/TT6 1 Tf.5617 0 TD-0023

See detailed or **GAS E**n**484 A B** g information on page 64 of this data sheet.

V7410 AWLYYWW

# **TABLE OF CONTENTS**

| Application Information       | . 3  |

|-------------------------------|------|

| Block Diagram                 | . 4  |

| Pin Assignment                | . 5  |

| Pin Definition                |      |

| Electrical Characteristics    | . 8  |

| SPI Interface Timing          | 10   |

| Detailed Description          | . 11 |

| Operating Modes               | . 12 |

| Register Memory Map           | . 13 |

| Application Information       |      |

| Device Configuration Examples | 63   |

# **APPLICATION INFORMATION**

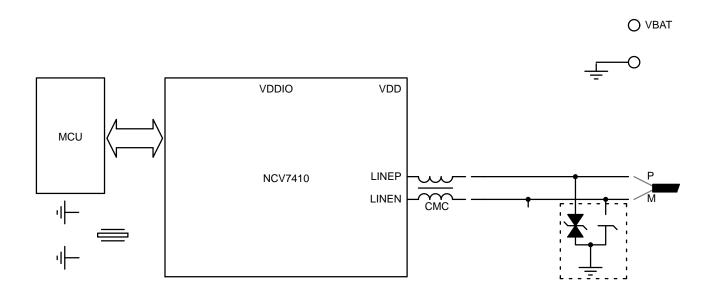

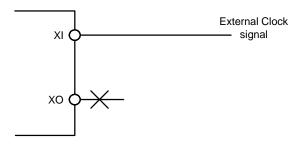

Figure 1 shows an example of an application with the NCV7410.

Figure 1. Basic Application Diagram

# PIN ASSIGNMENT

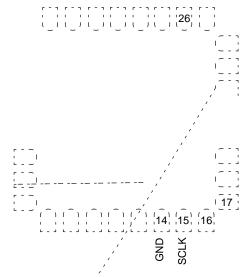

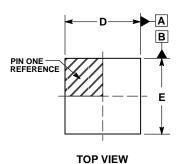

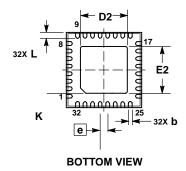

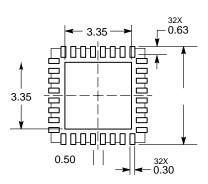

Figure 3. Pin Assignment ï QFN32 (Top View)

# PIN DEFINITION

The pinout of the NCV7410 is shown in Figure 3. The pin list is given in Pin Function Description table below.

Table 2. PIN FUNCTION DESCRIPTION

| Pin No.                            | Pin Name | Pin Function               | Description                                                                                                                                                                                                                             |

|------------------------------------|----------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                  | XO       | Output                     | Crystal XO                                                                                                                                                                                                                              |

| 2                                  | XI       | Input                      | Crystal XI / Reference clock input                                                                                                                                                                                                      |

| 4                                  | VDD      | Power Supply               | 3.3 V Power Supply Input                                                                                                                                                                                                                |

| 6                                  | LINEP    | Analog Input / Output      | Positive Medium Dependent Interface (MDI) terminal                                                                                                                                                                                      |

| 7                                  | LINEN    |                            | Negative Medium Dependent Interface (MDI) terminal                                                                                                                                                                                      |

| 8                                  | VDRVN    | Supply (regulator output)  | Output of internal TX LDO. Proper decoupling needed.                                                                                                                                                                                    |

| 11                                 | DIO1     | GPIO                       | General Purpose IO. During BOOT, an internal pull idown is connected                                                                                                                                                                    |

| 12                                 | DIO0     |                            | to both DIOs. See DIO Configuration Register.                                                                                                                                                                                           |

| 13                                 | RSTn     | Digital Input, Open Drain  | Reset pin (Active ïlow), internal 54 k pull ïup, driven low (25 ) during undervoltage event. To prevent damage, when driving this from an MCU or any active driver, make sure that such drive is configured to be an open drain driver. |

| 15                                 | SCLK     | Digital Input              | SPI interface Shift Clock                                                                                                                                                                                                               |

| 16                                 | IRQn     | Digital Output, open drain | Interrupt pin, active low                                                                                                                                                                                                               |

| 17, 21                             | VDDIO    | Supply Input               | Digital I/O voltage reference (3.3 V or 2.5 V)                                                                                                                                                                                          |

| 18                                 | MOSI     | Digital Input              | SPI interface Serial Data Input                                                                                                                                                                                                         |

| 19                                 | CSn      |                            | SPI interface Chip Select (active low)                                                                                                                                                                                                  |

| 20                                 | CLK_O    | Digital Output             | 25 MHz clock output                                                                                                                                                                                                                     |

| 23                                 | MISO     | Digital Output             | SPI interface Serial Data Output                                                                                                                                                                                                        |

| 25, 26, 27                         | NC       | Reserved                   | Do not connect                                                                                                                                                                                                                          |

| 28, 29                             | DVDD     | Supply (regulator output)  | Output of internal 1.8 V LDO. Proper decoupling is needed.                                                                                                                                                                              |

| 32                                 | NC       | Reserved                   | Do not connect                                                                                                                                                                                                                          |

| 3, 5, 9, 10, 14,<br>22, 24, 30, 31 | GND      | •                          | ·                                                                                                                                                                                                                                       |

# **Table 3. MAXIMUM RATINGS**

| Symbol          | Rating                                  | Min  | Max  | Unit |

|-----------------|-----------------------------------------|------|------|------|

| $V_{VDD\_MAX}$  | Voltage Supplies (VDD, VDDIO), (Note 1) | -0.3 | 3.65 | V    |

| $V_{DVDD\_MAX}$ | Low Voltage Supply Output (DVDD)        | -0.3 | 1.98 | V    |

# **ELECTRICAL CHARACTERISTICS**

**ELECTRICAL CHARACTERISTICS** (VDD = 2.97 V to 3.63 V; VDDIO = 2.25 V to 3.63 V; C<sub>VDD</sub>, C<sub>VDDA</sub>, C<sub>DRVN</sub> = 2.2  $\mu$ F; C<sub>VDDIO</sub> = 100 nF; T<sub>J</sub> = -40 to +150°C; for typical values T<sub>J</sub> = 25°C; for min/max values. T<sub>J</sub> = -40 to 150°C; unless otherwise noted. All voltages are referenced to GND (Exposed Pad). Positive currents flow into the respective pin.)

| Symbol           | Parameter      | Test Condition | Min | Тур | Max | Unit |

|------------------|----------------|----------------|-----|-----|-----|------|

| POWER SU         | PPLY – PIN VDD |                |     |     |     |      |

| I <sub>VDD</sub> | Supply Current | Transmitting   | _   | 45  |     |      |

|                  |                |                | -   |     |     |      |

|                  |                |                |     |     |     |      |

**ELECTRICAL CHARACTERISTICS** (VDD = 2.97 V to 3.63 V; VDDIO = 2.25 V to 3.63 V; C<sub>VDD</sub>, C<sub>VDDA</sub>, C<sub>DRVN</sub> = 2.2  $\mu$ F; C<sub>VDDIO</sub> = 100 nF; T<sub>J</sub> = -40 to +150°C; for typical values T<sub>J</sub> = 25°C; for min/max values. T<sub>J</sub> = -40 to 150°C; unless otherwise noted. All voltages are referenced to GND (Exposed Pad). Positive currents flow into the respective pin.) (continued)

| Symbol Parameter Test Condition Min Typ Max C | I | Symbol | Parameter | Test Condition | Min | Тур | Max | Unit |

|-----------------------------------------------|---|--------|-----------|----------------|-----|-----|-----|------|

|-----------------------------------------------|---|--------|-----------|----------------|-----|-----|-----|------|

# **SPI INTERFACE TIMING**

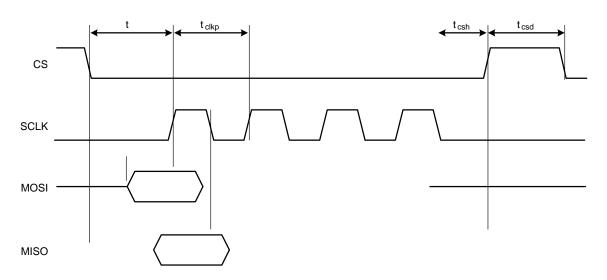

Figure 4. SPI Interface AC Timing Diagram

### **DETAILED DESCRIPTION**

The NCV7410 is a 10BASE–T1S Physical Layer Transceiver as specified in IEEE 802.3cg with an integrated Media Access Controller (MAC). It supports operation over a shared media (multidrop) network with up to 25 m of a single twisted pair (UTP / STP) connection.

The NCV7410 provides a Serial Peripheral Interface (SPI) in slave mode, allowing low pin count connection to standard, off–the–shelf Microcontrollers or SoC. The NCV7410 provides a link speed of 10 Mbit/s in half–duplex operation.

The MAC-PHY's SPI protocol is compliant to the specification issued by the Open Alliance. The NCV7410 can be locally configured to run Physical Layer Collision Avoidance (PLCA), that supports at least 8 nodes on the shared medium, depending on environmental conditions.

PLCA improves data throughput under high network load and provides additional benefits:

- Nodes are granted transmit opportunities using a round-robin arbitration scheme, enabling fair-shared access to the medium.

- By avoiding multiple back-off and retry events in the embedded MAC, maximum latencies are significantly reduced.

- Protects against the "babbling idiot" problem, as a single station can only transmit when granted an opportunity to do so.

The integration of the PLCA reconciliation sublayer (PLCA RS) in the device enables connected hosts to take full advantage of collision–free Ethernet communication on a single twisted pair, shared medium.

The integrated CSMA/CD 10 Mbps MAC provides the following features:

• Multiple MAC address filtering

- Broadcast / Multicast filtering

- Promiscuous Mode, accepting every frame regardless of its type or address

- FCS generation / checking

- Statistics / Diagnostic Counters

- Status reporting

- Factory provided unique MAC address.

The SPI Protocol handler supports:

- 8-byte, 16-byte, 32-byte and 64-byte data chunks

- Both "Store & Forward" and "Cut-Through" operation

- Protected and Unprotected control transaction

- 4 kB TX-Buffer

- 4 kB RX-Buffer

- SPI clock up to 25 MHz

Additional non-standard features are implemented into the NCV7410:

- Enhanced Noise Immunity PMA operation (ENI)

- Collision detection masking

- PLCA Precedence Mode

- PLCA coordinator selection

- Proprietary topology discovery, allowing to measure the distance between nodes on the link segment works only when all communication partners are onsemi 10BASE-T1S devices: NCV7410, NCV7311, NCN26010 or NCN26000.

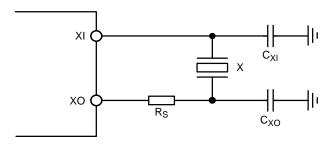

The integrated Crystal Oscillator circuitry allows the use of an external CMOS oscillator, a quartz crystal, or any other external clock source, as long as its accuracy is in line with the specifications.

# **REGISTER MEMORY MAP**

The NCV7410 provides the registers grouped in memory map selection groups. See the below table for details.

Table 9. REGISTER MAP OVERVIEW

|          | EGISTER N<br>MS | Addr       |            |                                                                  |

|----------|-----------------|------------|------------|------------------------------------------------------------------|

| Hex      | Dec             | Hex        | Dec        | Name                                                             |

| MMS0 REG | SISTERS         |            |            |                                                                  |

| 0x0      | 0               | 0x0        | 0          | SPI Identification Register, IDVER                               |

|          |                 | 0x1        | 1          | SPI Identification Register, PHY ID                              |

|          |                 | 0x2        | 2          | SPI Capabilities, SPICAP                                         |

|          |                 | 0x3        | 3          | Reset Control and Status, RESET                                  |

|          |                 | 0x4        | 4          | SPI Protocol Configuration Register, CONFIG0                     |

|          |                 | 0x8        | 8          | SPI Protocol Status Register, STATUS0                            |

|          |                 | 0xB        | 11         | Buffer Status Register, BUFSTS                                   |

|          |                 | 0xC        | 12         | Interrupt Mask Register, IMASK                                   |

|          |                 | 0xFF00     | 65280      | PHY Control Register                                             |

|          |                 | 0xFF01     | 65281      | PHY Status Register                                              |

|          |                 | 0xFF02     | 65282      | PHY Identifier 0 Registers                                       |

|          |                 | 0xFF03     | 65283      | PHY Identifier 1 Registers                                       |

| MMS1 REG | SISTERS ï R     | EGISTERS F | RELATED TO | THE MAC                                                          |

| 0x1      | 1               | 0x0        | 0          | MAC Control0 Register                                            |

|          |                 | 0x10       | 16         | Address Filter 0 Low, ADDRFILT0L                                 |

|          |                 | 0x11       | 17         | Address Filter 0 High, ADDRFILT0H                                |

|          |                 | 0x12       | 18         | Address Filter 1 Low, ADDRFILT1L                                 |

|          |                 | 0x13       | 19         | Address Filter 1 High, ADDRFILT1H                                |

|          |                 | 0x14       | 20         | Address Filter 2 Low, ADDRFILT2L                                 |

|          |                 | 0x15       | 21         | Address Filter 2 High, ADDRFILT2H                                |

|          |                 | 0x16       | 22         | Address Filter 3 Low, ADDRFILT3L                                 |

|          |                 | 0x17       | 23         | Address Filter 3 High, ADDRFILT3H                                |

|          |                 | 0x20       | 32         | Address Mask 0 Low, ADDRMASK0L                                   |

|          |                 | 0x21       | 33         | Address Mask 0 High, ADDRMASK0H                                  |

|          |                 | 0x22       | 34         | Address Mask 1 Low, ADDRMASK1L                                   |

|          |                 | 0x23       | 35         | Address Mask 1 High, ADDRMASK1H                                  |

|          |                 | 0x24       | 36         | Address Mask 2 Low, ADDRMASK2L                                   |

|          |                 | 0x25       | 37         | Address Mask 2 High, ADDRMASK0H                                  |

|          |                 | 0x26       | 38         | Address Mask 3 Low, ADDRMASK3L                                   |

|          |                 | 0x27       | 39         | Address Mask 0 High, ADDRMASK3H                                  |

|          |                 | 0x30       | 48         | Statistic, Sent Bytes Counter Low, STOCTETSTXL                   |

|          |                 | 0x31       | 49         | Statistic, Sent Bytes Counter High, STOCTETSTXH                  |

|          |                 | 0x32       | 50         | Statistic, Frames Sent Ok, STFRAMESTXOK                          |

|          |                 | 0x33       | 51         | Statistic, Broadcast Frames Sent Ok, STBCASTTXOK                 |

|          |                 | 0x34       | 52         | Statistic, Multicast Frames Sent Ok, STMCASTTXOK                 |

|          |                 | 0x35       | 53         | Statistic, 64 ïbyte Frames Sent Ok, STFRAMESTX64                 |

|          |                 | 0x36       | 54         | Statistic, 65 ïbyte to 127 ïbyte Frames Sent Ok, STFRAMESTX65    |

|          |                 | 0x37       | 55         | Statistic, 128 ïbyte to 255 ïbyte Frames Sent Ok, STFRAMESTX128  |

|          |                 | 0x38       | 56         | Statistic, 256 ïbyte to 511 ïbyte Frames Sent Ok, STFRAMESTX256  |

|          |                 | 0x39       | 57         | Statistic, 512 ïbyte to 1023 ïbyte Frames Sent Ok, STFRAMESTX512 |

Table 9. REGISTER MAP OVERVIEW (continued)

| 0x3B 59 Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERF 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLEC 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCO 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES 0x4A 74 Statistic, 512-byte or 1023-byte Frames Received Ok, STFRAMEST 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMEST 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                  | ISTERS - REGISTERS RELATED TO THE MAC  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | MS          | Add        | ress       |                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|------------|------------|----------------------------------------------------------------------------|

| 1 0x3A 58 Statistic, 1024-byte or More Frames Sent Ok, STFRAMESTX1024 0x3B 59 Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERF 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLEC 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCC 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 128-byte to 511-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMEST 0x4B 75 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG 0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames Received, STSYMBOLERF 0x50 80 Statistic, Symbol Errors During Frame Reception, STSYMBOLERF 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERF 0x50 80 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED | 1 0x3A 58 Statistic, 1024-byte or More Frames Sent Ok, STFRAMESTX1024 0x3B 59 Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERFLOW 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLECOL 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCOL 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Frames Received Dk, STCAMESRXOK 0x43 67 Statistic, Frames Received Ok, STEAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STBCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX128 0x4A 74 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX512 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frame STRXTOOLONG 0x4E 78 Statistic, Dropped Too Long Frame STRXTOOLONG 0x4E 78 Statistic, Align Errors During Frame Reception, STSYMBOLERRS 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  STERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  Devices in Package 2 Register        | Hex      | Dec         | Hex        | Dec        | Name                                                                       |

| 0x3B 59 Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERF 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLEC 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCO 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x3F 63 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x4D 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMEST 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMEST 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Short Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR 0x5D 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                      | 0x3B 59 Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERFLOW 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLECOL 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCOL 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX55 0x48 72 Statistic, 128-byte to 555-byte Frames Received Ok, STFRAMESTX55 0x4A 74 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024 0x4C 76 Statistic, Dropped Too Long Frames Received Ok, STFRAMESTX1024 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Short Frames STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frame Received Ok, STFRAMESTX1024 0x4E 78 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS 0x5D 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x5D 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x5D 82 Statistic, RX Dropped Frame Count, STRXDROPPED | IMS1 REG | SISTERS – R | EGISTERS F | RELATED TO | O THE MAC                                                                  |

| 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLEC 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCO 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STMCASTRXOK 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512-byte or 1023-byte Frames Received Ok, STFRAMEST 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMEST 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                              | 0x3C 60 Statistic, Frames Transmitted after a Single Collision, STSINGLECOL 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCOL 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL 0x3F 63 Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL 0x3F 63 Statistic, Counter of CRS De–assertion During Frame Transmission, STCRSERR 0x40 64 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STBCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 124-byte or 1023-byte Frames Received Ok, STFRAMESTX56 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX124 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frame Received Ok, STFRAMESTX1024 0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERRS 0x50 80 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                | 0x1      | 1           | 0x3A       | 58         | Statistic, 1024-byte or More Frames Sent Ok, STFRAMESTX1024                |

| 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCO 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512-byte or More Frames Received Ok, STFRAMEST 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped Too Long Frame Reception, STSYMBOLERF 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERF 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                         | 0x3D 61 Statistic, Frames Transmitted after Multiple Collisions, STMULITCOL 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Broadcast Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STMCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX562 0x4A 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX124 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames Reception, STSYMBOLERRS 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  Devices in Package 2 Register                                                                                                                                                                                                                                                                                                                                               |          |             | 0x3B       | 59         | Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERFLOW          |

| 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCES 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMEST 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames STFCSERRS 0x50 80 Statistic, Mign Errors During Frame Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                           | 0x3E 62 Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024 0x4C 76 Statistic, Dropped Too Short Frames STRXTOOLONG 0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register 0x60 Bevices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                            |          |             | 0x3C       | 60         | Statistic, Frames Transmitted after a Single Collision, STSINGLECOL        |

| 0x3F 63 Statistic, Frames Transmitted after Deferral, STDEFEEREDTX 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES' 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES' 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x3F         63         Statistic, Frames Transmitted after Deferral, STDEFEEREDTX           0x40         64         Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR           0x41         65         Statistic, Received Bytes Counter Low, STOCTETSRXL           0x42         66         Statistic, Received Bytes Counter High, STOCTETSRXH           0x43         67         Statistic, Frames Received Ok, STFRAMESRXOK           0x44         68         Statistic, Broadcast Frames Received Ok, STBCASTRXOK           0x45         69         Statistic, Multicast Frames Received Ok, STBCASTRXOK           0x46         70         Statistic, 64-byte Frames Received Ok, STFRAMESRX64           0x47         71         Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX128           0x48         72         Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128           0x49         73         Statistic, 512-byte to 101-byte Frames Received Ok, STFRAMESTX512           0x40         74         Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024           0x40         75         Statistic, Dropped Too Short Frames, STRUNTERR           0x40         76         Statistic, Dropped Too Long Frames STRXTOOLONG           0x4F         79         Statistic, Dropped FCS Error Frames STFCSERRS           0x50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |             | 0x3D       | 61         | Statistic, Frames Transmitted after Multiple Collisions, STMULITCOL        |

| 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Align Errors During Frame Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x40 64 Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256 0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512 0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG 0x4E 78 Statistic, Dropped Too Long Frames STFCSERRS 0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  0x60 Devices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             | 0x3E       | 62         | Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL      |

| 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES' 0x49 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES' 0x4A 74 Statistic, 512-byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG 0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x41 65 Statistic, Received Bytes Counter Low, STOCTETSRXL  0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH  0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK  0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX128  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |             | 0x3F       | 63         | Statistic, Frames Transmitted after Deferral, STDEFEEREDTX                 |

| 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH  0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK  0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESR  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMES'  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES'  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES'  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMES'X  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS  0x4F 79 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x42 66 Statistic, Received Bytes Counter High, STOCTETSRXH  0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK  0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STFCSERRS  0x4F 79 Statistic, Dropped FCS Error Frames STFCSERRS  0x50 80 Statistic, Align Errors During Frame Reception, STSYMBOLERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  0x60 Devices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |             | 0x40       | 64         | Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR |

| 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK  0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESR  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMES'  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES'  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES'  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMES'X  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x43 67 Statistic, Frames Received Ok, STFRAMESRXOK  0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX512  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  0x6 6 Devices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |             | 0x41       | 65         | Statistic, Received Bytes Counter Low, STOCTETSRXL                         |

| 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMES'  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES'  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES'  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMES'  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STFXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x44 68 Statistic, Broadcast Frames Received Ok, STBCASTRXOK  0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |             | 0x42       | 66         | Statistic, Received Bytes Counter High, STOCTETSRXH                        |

| 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMES'  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES'  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES'  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMES'X  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x45 69 Statistic, Multicast Frames Received Ok, STMCASTRXOK  0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX512  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  0x60 6 Devices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             | 0x43       | 67         | Statistic, Frames Received Ok, STFRAMESRXOK                                |

| 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMEST  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMES'  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMES'  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMES'  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x46 70 Statistic, 64-byte Frames Received Ok, STFRAMESRX64  0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX512  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  0x60 6 Devices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |             | 0x44       | 68         | Statistic, Broadcast Frames Received Ok, STBCASTRXOK                       |

| 0x47 71 Statistic, 65–byte to 127–byte Frames Received Ok, STFRAMEST 0x48 72 Statistic, 128–byte to 255–byte Frames Received Ok, STFRAMEST 0x49 73 Statistic, 256–byte to 511–byte Frames Received Ok, STFRAMEST 0x4A 74 Statistic, 512–byte to 1023–byte Frames Received Ok, STFRAMEST 0x4B 75 Statistic, 1024–byte or More Frames Received Ok, STFRAMESTX 0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR 0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG 0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS 0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERR 0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS 0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW 0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x47 71 Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65  0x48 72 Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128  0x49 73 Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256  0x4A 74 Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512  0x4B 75 Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024  0x4C 76 Statistic, Dropped Too Short Frames, STRUNTERR  0x4D 77 Statistic, Dropped Too Long Frames STRXTOOLONG  0x4E 78 Statistic, Dropped FCS Error Frames STFCSERRS  0x4F 79 Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS  0x50 80 Statistic, Align Errors During Frame Reception, STALIGNERRS  0x51 81 Statistic, RX Buffer Overflow Errors, STRXOVERFLOW  0x52 82 Statistic, RX Dropped Frame Count, STRXDROPPED  ISTERS - REGISTERS RELATED TO THE PHY: PCS  2 0x5 5 Devices in Package 1 Register  0x60 Bevices in Package 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |             | 0x45       | 69         | Statistic, Multicast Frames Received Ok, STMCASTRXOK                       |