### ORDERING INFORMATION

| Device        | Packag  | e   | Shipping <sup>†</sup> |

|---------------|---------|-----|-----------------------|

| NCV7450DB0R2G | TSSOP16 | -EP | 4000 / Tape &         |

|               | (Pb–Fre | e)  | Reel                  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

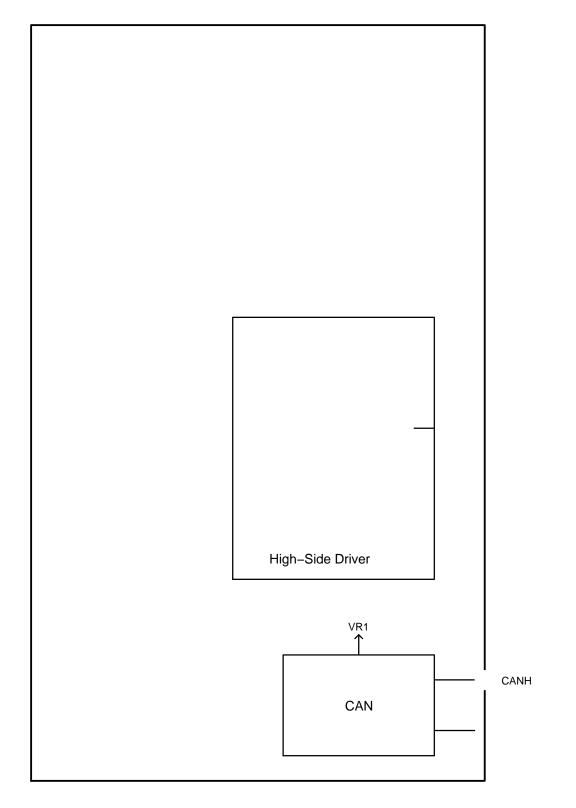

Figure 2. Block Diagram

| Symbol         | Rating                                           | Min | Max | Unit |

|----------------|--------------------------------------------------|-----|-----|------|

| VS1            | Functional supply voltage                        | 5   | 28  | V    |

| VSI            | Supply voltage for valid parameter specification | 6   | 18  | V    |

| VS2            | Functional supply voltage                        | 4.3 | 24  | V    |

| V52            | Supply voltage for valid parameter specification | 6   | 18  | V    |

| VR1            | VR1 LDO output voltage                           | 4.9 | 5.1 | V    |

| VdigIO         | Digital inputs/outputs voltage                   | 0   | VR1 | V    |

| HS             | High-side driver voltage                         | 0   | VS2 | V    |

| CANH, CANL     | CAN bus pins voltage                             | -40 | 40  | V    |

| TJ             | Junction Temperature                             | -40 | 150 | °C   |

| T <sub>A</sub> | Ambient Temperature                              | -40 | 125 | °C   |

### Table 4. RECOMMENDED OPERATING RANGES

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Table 5. ELECTRICAL CHARACTERISTICS (6 V  $\leq$  Vs1 = Vs2  $\leq$  18 V; -40°C  $\leq$  Tj  $\leq$  150°C; unless otherwise specified.)

| Symbol           | Parameter                        | Conditions                             | Min | Тур | Max | Unit |

|------------------|----------------------------------|----------------------------------------|-----|-----|-----|------|

| DIGITAL OUTPUT R | STN                              |                                        |     |     |     |      |

| VoutL_RSTN       | Low-level output voltage, low    | VR1 > 4.7 V, I(RSTN) = 0.7 mA          | -   | -   | 0.4 | V    |

|                  | VR1/VS1                          | VR1 > 2 V, VS1 < VR1, I(RSTN) = 0.1 mA | -   | -   | 0.4 |      |

|                  |                                  | VS1 > 2 V, I(RSTN) = 0.3 mA            | -   | -   | 0.4 |      |

| Rpullup_RSTN     | Internal pull-up resistor to VR1 |                                        | 5.0 | 10  | 19  | kΩ   |

DIGITAL INPUTS TxDC, CAN\_EN, WD\_EN, HS\_EN, WDI

| VinL_pinx | Low-level input voltage (logical "Low")      | 0   | _ | 0.8 | V |

|-----------|----------------------------------------------|-----|---|-----|---|

| VinH_pinx | High–level input voltage (logical<br>"High") | 2.0 | - | VR1 |   |

| <b>、</b> |      |      |

|----------|------|------|

| .)       |      |      |

| Тур      | Max  | Unit |

|          |      |      |

| Ι        | +5.0 | mA   |

| 0        | +5.0 | μΑ   |

| 2.5      | 3.0  | V    |

| 2.5      | 3.0  | V    |

| 0        | 0.1  | V    |

| 0        | 0.1  | V    |

| 0        | 0.2  | V    |

| 3.5      | 4.5  | V    |

| 1.5      | 2.25 | V    |

|          | 1.1  | VR1  |

2.25 3.0 V 94Ry"L I=9ï•p'\$ÃaU0I ®•ĐÄ 4:Sq1R‰ 7•y€ € Ci

### Table 6. ELECTRICAL CHARACTERISTICS (CONTINUED)

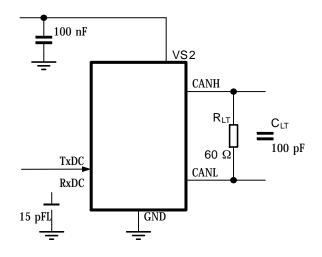

(VR1 = 4.75 V to 5.25 V;  $T_J$  = -40°C to +150°C;  $R_{LT}$  = 60  $\Omega$ ,  $C_{LT}$  = 100 pF,  $C_1$  not used unless specified otherwise.)

| Symbol                    | Parameter                                | Conditions          | Min | Тур | Max | Unit |

|---------------------------|------------------------------------------|---------------------|-----|-----|-----|------|

| CAN BUS LINES (           | Pins CANH and CANL)                      |                     |     |     |     |      |

| R <sub>i(cm)</sub> (CANL) | Common-mode input resistance at pin CANL | $-2 V \le V_{CANH}$ |     |     |     |      |

### FUNCTIONAL DESCRIPTION

### Supply Concept

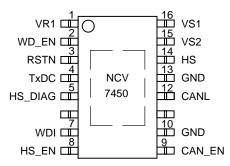

The device has two independent supply pins VS1 and VS2. While VR1 regulator and logic control are supplied from VS1, High side driver is supplied from VS2. Both supply lines have to be properly decoupled by filtration capacitors close to the device pins.

As long as  $VS1 < VS\_POR$  level, all the blocks are in power down mode.

### VR1 Low-drop Regulator

VR1 is a low drop output regulator providing 5 V voltage derived

### **HS** Driver

HS high side driver is intended to drive an external load. Its state is directly controlled via HS\_EN pin and diagnostics are flagged on HS\_DIAG pin (see Table 7).

When the driver is enabled (HS\_EN = High), it is protected against an excessive current and temperature and diagnosed on Underload condition.

In case the HS driver is controlled by a PWM signal through HS\_EN with very low duty cycle, the diagnostic

features are limited by  $td_oc_HS$  in case of an overcurrent and  $(VS2 / dVout_HS) + td_uld_HS$  in case of an underload.

The HS driver is designed to drive resistive loads. Therefore only a limited clamping energy (W < 1 mJ) can be dissipated by the device. For inductive loads (L > 100  $\mu$ H) an external freewheeling diode connected between GND and the HS pin is required.

| Table 7. | HS | Driver | Diagnostics |

|----------|----|--------|-------------|

|----------|----|--------|-------------|

| Event                         | HS_EN | Failure condition      | HS status | HS_DIAG | Recovery condition     |  |

|-------------------------------|-------|------------------------|-----------|---------|------------------------|--|

| Normal aparation (no failure) | Low   | -                      | Off       | High    | -                      |  |

| Normal operation (no failure) | High  | -                      | On        | High    | -                      |  |

| Overcurrent                   | High  | I(HS) > <i>loc_HS</i>  | Off       | Low     | HS_EN = Low            |  |

| Underload                     | Lliab |                        | 0.2       | Low     |                        |  |

| Short-to-battery              | High  | I(HS) < <i>luld_HS</i> | On        | Low     | I(HS) > <i>luld_HS</i> |  |

| Over-temperature              | High  | Tj > <i>T</i> sd1      | Off       | Low     | Tj < Tsd1_off          |  |

|                               | •     | •                      |           | •       | •                      |  |

VS2 Overvoltage

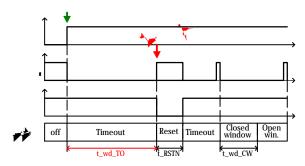

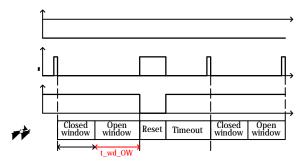

In case the watchdog is not triggered before the timeout or open window elapses (Figure 11, Figure 12), or trigger is sent within the closed window (Figure 13), RSTN signal is generated and then watchdog restarted in the timeout mode again.

Figure 11. Missed watchdog in Timeout mode

Figure 12. Missed watchdog in Window mode

### Table 8. ISO11898–2:2016 PARAMETER CROSS-REFERENCE TABLE

| ISO 11898–2:2016 Specification                                  | NCV7450 Datasheet  |                               |

|-----------------------------------------------------------------|--------------------|-------------------------------|

| Parameter                                                       | Notation           | Symbol                        |

| DOMINANT OUTPUT CHARACTERISTICS                                 |                    |                               |

| Single ended voltage on CAN_H                                   | V <sub>CAN_H</sub> | V <sub>o(dom)</sub> (CANH)    |

| Single ended voltage on CAN_L                                   | V <sub>CAN_L</sub> | V <sub>o(dom)(CANL)</sub>     |

| Differential voltage on normal bus load                         | V <sub>Diff</sub>  | V <sub>o(dom)(diff)</sub>     |

| Differential voltage on effective resistance during arbitration | V <sub>Diff</sub>  | V <sub>o(dom)(diff)_arb</sub> |

Optional: Differential voltage on extended bus load range

### Table 8. ISO11898-2:2016 PARAMETER CROSS-REFERENCE TABLE

| ISO 11898–2:2016 Specification                                                                                   | NCV7450 Datasheet                          |                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------|--|--|--|

| Parameter                                                                                                        | Notation                                   | Symbol                                 |  |  |  |

| OPTIONAL IMPLEMENTATION DATA SIGNAL TIMING REQUIREMENTS for use with bit rates above 2 Mbit/s and up to 5 Mbit/s |                                            |                                        |  |  |  |

| Transmitted recessive bit width @ 5 Mbit/s                                                                       | t <sub>Bit(Bus)</sub>                      | t <sub>Bit(Vi(diff))</sub>             |  |  |  |

| Transmitted recessive bit width @ 5 Mbit / s                                                                     | t <sub>Bit(RXD)</sub>                      | t <sub>Bit(RxD)</sub>                  |  |  |  |

| Received recessive bit width @ 5 Mbit / s                                                                        | $\Delta t_{Rec}$                           | $\Delta t_{Rec}$                       |  |  |  |

| MAXIMUM RATINGS OF V <sub>CAN_H</sub> , V <sub>CAN_L</sub> AND V <sub>DIFF</sub>                                 |                                            |                                        |  |  |  |

| Maximum rating V <sub>Diff</sub>                                                                                 | V <sub>Diff</sub>                          | Vmax_diff                              |  |  |  |

| General maximum rating $V_{\mbox{CAN}\mbox{-}\mbox{H}}$ and $V_{\mbox{CAN}\mbox{-}\mbox{L}}$                     | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub>   | V <sub>CANH</sub><br>V <sub>CANL</sub> |  |  |  |

| Optional: Extended maximum rating $V_{\mbox{CAN}\_\mbox{H}}$ and $V_{\mbox{CAN}\_\mbox{L}}$                      | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub>   | NA                                     |  |  |  |

| MAXIMUM LEAKAGE CURRENTS ON CAN_H AND CAN_L, UNPOWERED                                                           |                                            |                                        |  |  |  |

| Leakage current on CAN_H, CAN_L                                                                                  | I <sub>CAN_H</sub> ,<br>I <sub>CAN_L</sub> | lLi                                    |  |  |  |

| BUS BIASING CONTROL TIMINGS                                                                                      |                                            |                                        |  |  |  |

| CAN activity filter time, long                                                                                   | t <sub>Filter</sub>                        | NA                                     |  |  |  |

| CAN activity filter time, short                                                                                  | t <sub>Filter</sub>                        | t <sub>wake_filt</sub>                 |  |  |  |

| Optional: Wake-up timeout, short                                                                                 | t <sub>Wake</sub>                          | t <sub>wake_to</sub>                   |  |  |  |

| Optional: Wake-up timeout, long                                                                                  | t <sub>Wake</sub>                          | t <sub>wake_to</sub>                   |  |  |  |

| Timeout for bus inactivity (Required for selective wake-up implementation only)                                  | t <sub>Silence</sub>                       | NA                                     |  |  |  |

| Bus Bias reaction time (Required for selective wake-up implementation only)                                      | t <sub>Bias</sub>                          | NA                                     |  |  |  |

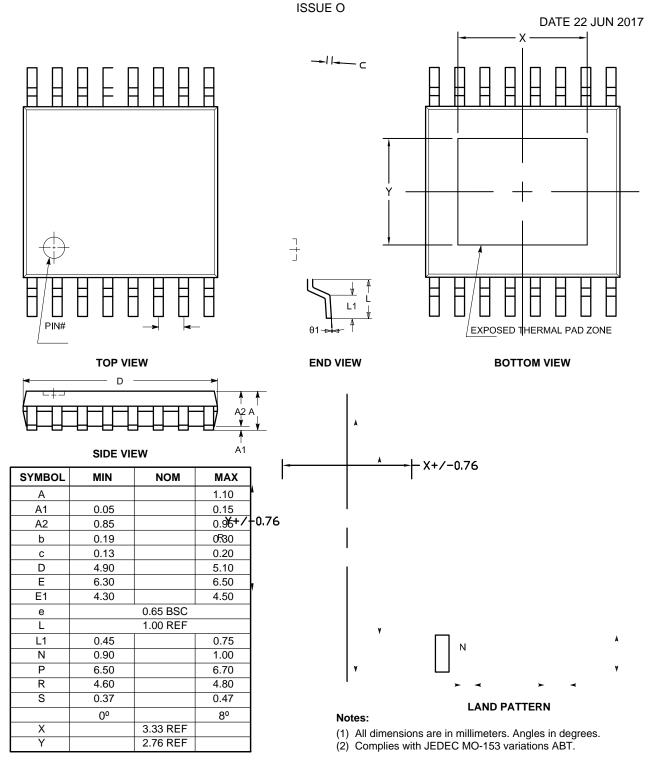

### MECHANICAL CASE OUTLINE PACKAGE DIMENSIONS

TSSOP16, 4.4x5 EXPOSED PAD CASE 948BV

TM

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi