# **•** • •

The NCV 890100 is a fixed

ceramic output filter capacitor forming a

.

space

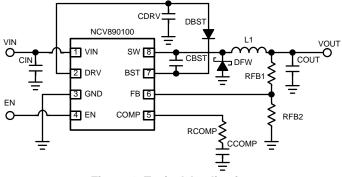

Figure 1. Typical Application

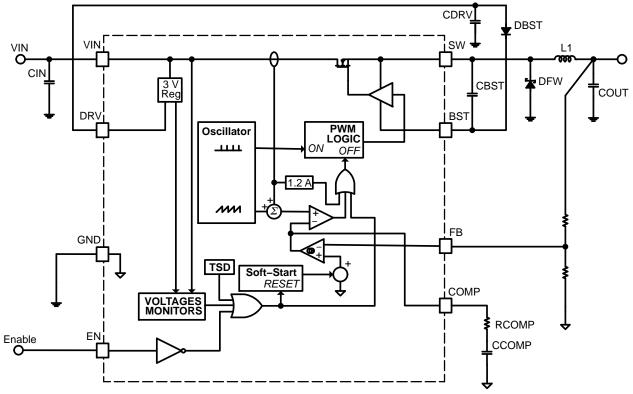

Figure 2. NCV890100 Block Diagram

#### MAXIMUM RATINGS

Rating

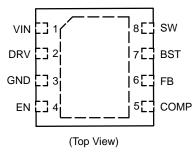

Figure 3. Pin Connections

#### **PIN FUNCTION DESCRIPTIONS**

| Pin No.        | Symbol | Description                                                                                                                                                                          |  |  |  |  |

|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1              | VIN    | Input voltage from battery. Place an input filter capacitor in close proximity to this pin.                                                                                          |  |  |  |  |

| 2              | DRV    | Output voltage to provide a regulated voltage to the Power Switch gate driver.                                                                                                       |  |  |  |  |

| 3              | GND    | Battery return, and output voltage ground reference.                                                                                                                                 |  |  |  |  |

| 4              | EN     | This TTL compatible Enable input allows the direct connection of Battery as the enable signal. Grounding this input stops switching and reduces quiescent current draw to a minimum. |  |  |  |  |

| 5              | COMP   | Error Amplifier output, for tailoring transient response with external compensation components.                                                                                      |  |  |  |  |

| 6              | FB     | Feedback input pin to program output voltage, and detect pre-charged or shorted output conditions.                                                                                   |  |  |  |  |

| 7              | BST    | Bootstrap input provides drive voltage higher than VIN to the N–channel Power Switch for optimum switch $R_{DS(on)}$ and highest efficiency.                                         |  |  |  |  |

| 8              | SW     | Switching node of the Regulator. Connect the output inductor and cathode of the freewheeling diode to this pin.                                                                      |  |  |  |  |

| Exposed<br>Pad |        | Connect to Pin 3 (electrical ground) and to a low thermal resistance path to the ambient temperature environment.                                                                    |  |  |  |  |

**ELECTRICAL CHARACTERISTICS** (VIN = 4.5 V to 28 V, VEN = 5 V, V

**ELECTRICAL CHARACTERISTICS** (V<sub>IN</sub> = 4.5 V to 28 V, V<sub>EN</sub> = 5 V, V<sub>BST</sub> = V<sub>SW</sub> + 3.0 V, C<sub>DRV</sub> = 0.1  $\mu$ F, Min/Max values are valid for the temperature range  $-40^{\circ}C \le T_J \le 150^{\circ}C$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Parameter                                                                                    | Symbol                                                         | Conditions                                                                                                                                                     | Min              | Тур              | Max              | Unit |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------|--|--|--|

| POWER SWITCH                                                                                 |                                                                |                                                                                                                                                                |                  |                  |                  |      |  |  |  |

| ON Resistance                                                                                | R <sub>DSON</sub>                                              | $V_{BST} = V_{SW} + 3.0 V$                                                                                                                                     |                  |                  | 650              | mΩ   |  |  |  |

| Leakage current VIN to SW                                                                    | I <sub>LKSW</sub>                                              | $V_{EN} = 0 \text{ V}, \text{ V}_{SW} = 0, \text{ V}_{IN} = 18 \text{ V}$                                                                                      |                  |                  | 10               | μΑ   |  |  |  |

| Minimum ON Time                                                                              | t <sub>ONMIN</sub>                                             | Measured at SW pin                                                                                                                                             | 45               |                  | 70               | ns   |  |  |  |

| Minimum OFF Time                                                                             | t <sub>OFFMIN</sub>                                            | $\begin{array}{l} \mbox{Measured at SW pin} \\ \mbox{At } F_{SW} = 2 \mbox{ MHz (normal)} \\ \mbox{At } F_{SW} = 500 \mbox{ kHz (max duty cycle)} \end{array}$ | 30               | 30<br>50         | 70               | ns   |  |  |  |

| PEAK CURRENT LIMIT                                                                           |                                                                |                                                                                                                                                                |                  |                  |                  |      |  |  |  |

| Current Limit Threshold                                                                      | I <sub>LIM</sub>                                               |                                                                                                                                                                | 1.4              | 1.55             | 1.7              | А    |  |  |  |

| SHORT CIRCUIT FREQUENCY FOLDBACK                                                             | (                                                              |                                                                                                                                                                |                  |                  |                  |      |  |  |  |

| Lowest Foldback Frequency<br>Lowest Foldback Frequency – High V <sub>in</sub><br>Hiccup Mode | F <sub>SWAF</sub><br>F <sub>SWAFHV</sub><br>F <sub>SWHIC</sub> | $ \begin{array}{c} V_{FB} = 0 \ V,  4.5 \ V < V_{IN} < 18 \ V \\ V_{FB} = 0 \ V,  20 \ V < V_{IN} < 28 \ V \\ V_{FB} = 0 \ V \end{array} $                     | 400<br>200<br>24 | 500<br>250<br>32 | 600<br>300<br>40 | kHz  |  |  |  |

| GATE VOLTAGE SUPPLY (DRV pin)                                                                |                                                                |                                                                                                                                                                |                  |                  |                  | -    |  |  |  |

| Output Voltage                                                                               | V <sub>DRV</sub>                                               |                                                                                                                                                                | 3.1              | 3.3              | 3.5              | V    |  |  |  |

| DRV POR Start Threshold                                                                      | V                                                              |                                                                                                                                                                |                  |                  |                  | -    |  |  |  |

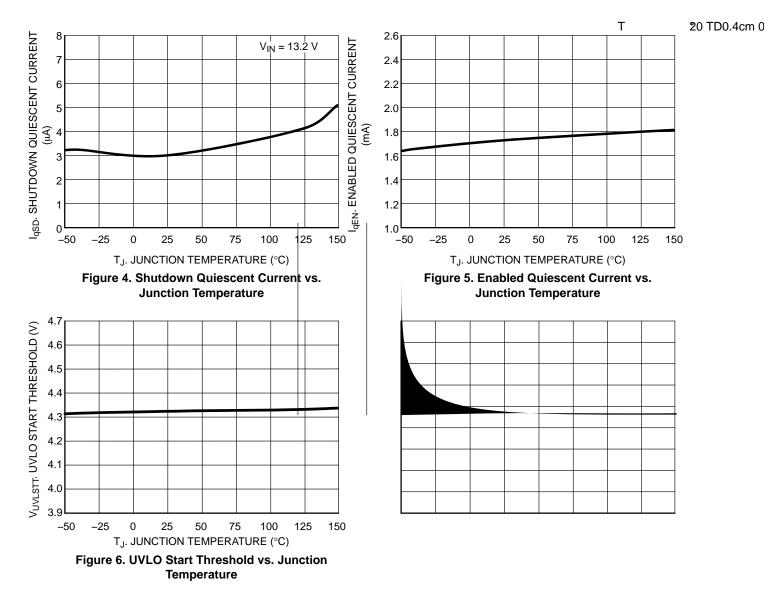

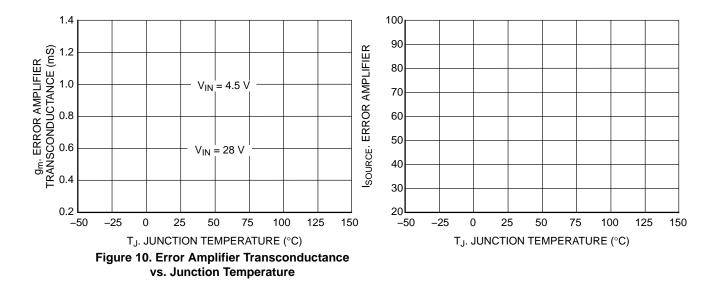

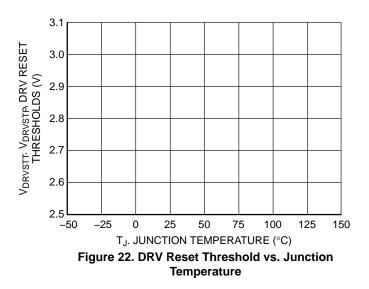

#### **TYPICAL CHARACTERISTICS CURVES**

#### T1 Tw[(. JUNCTION TEMPERA)70.7(TU

#### **TYPICAL CHARACTERISTICS CURVES**

# www.onsemi.com

NCV890100

## **TYPICAL CHARACTERISTICS CURVES**

## **GENERAL INFORMATION**

#### INPUT VOLTAGE

An Undervoltage Lockout (UVLO) circuit monitors the input, and inhibits switching and resets the Soft start circuit

#### BOOTSTRAP

At the DRV pin an internal regulator provides a ground referenced voltage to an external capacitor ( $C_{DRV}$ ), to allow fast recharge of the external bootstrap capacitor ( $C_{BST}$ ) used to supply power to the power switch gate driver. If the voltage at the DRV pin goes below the DRV UVLO Threshold V<sub>DRVSTB</sub> switching is inhibited and the Soft start circuit is reset, until the DRV pin voltage goes back up above V<sub>DRVSTT</sub>.

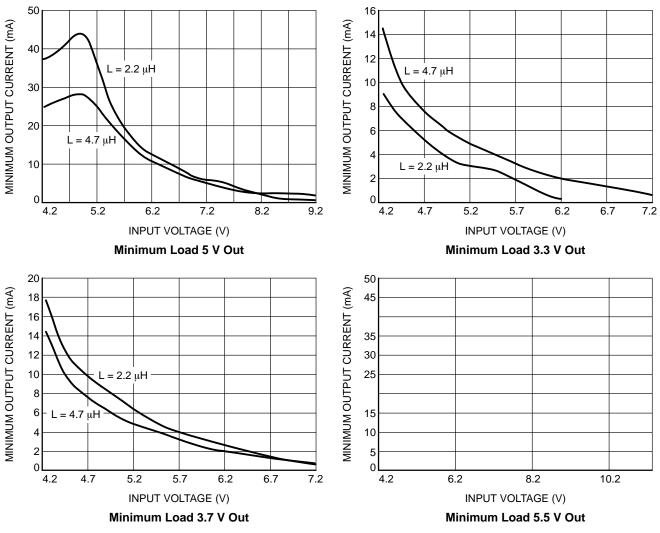

In order for the bootstrap capacitor to stay charged, the Switch node needs to be pulled down to ground regularly. In very light load condition, the NCV 890100 skips switching cycles to ensure the output voltage stays regulated. When the skip cycle repetition frequency gets too low, the bootstrap voltage collapses and the regulator stops switching. Practically, this means that the NCV 890100 needs a minimum load to operate correctly. Figure 27 shows the minimum current requirements for different input and output voltages.

Figure 27. Minimum Load Current with Different Input and Output Voltages

#### **OUTPUT PRECHARGE DETECTION**

Prior to Soft start, the FB pin is monitored to ensure the SW voltage is low enough to have charged the external bootstrap capacitor ( $C_{BST}$ ). If the FB pin is higher than  $V_{SSEN}$ , restart is delayed until the output has discharged.

where

$$Mc = 1 + \frac{Se}{Sn}$$

(eq. 16)

$$Sn = \frac{Vin - Vout}{L} \cdot Ri$$

(eq. 17)

Ri represents the equivalent sensing resistor which has a value of 0.29  $\Omega$ , Se is the compensation slope which is 291.9 kV/S, Sn is the slope of the sensing resistor current during on time. Fh(s) represents the sampling effect from the current loop which has two poles at one half of the switching frequency:

$$Fh(s) = \frac{1}{1 + \frac{s}{\omega n \cdot Qp} + \frac{s^2}{\omega n^2}}$$

(eq. 18)

$$\omega n = \pi \cdot Fsw$$

Qp =

$$\frac{1}{\pi \cdot [Mc \cdot (1 - D) - 0.5]}$$

(eq. 19)

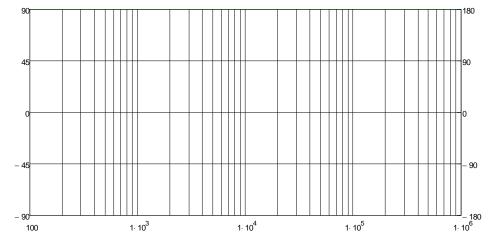

The total loop transfer function is the product of power stage and feedback compensation network.

$$Gloop(s) = Gdivider(s) \cdot Gerr_{amp(s)} \cdot Gps(s)$$

(eq. 20)

The bode plots of the open loop transfer function will show the gain and phase margin of the system. The compensation network is designed to make sure the system has enough phase margin and bandwidth.

#### **Design of the Compensation Network**

The function of the compensation network is to provide enough phase margin at crossover frequency to stabilize the system as well as to provide high gain at low frequency to eliminate the steady state error of the output voltage. Please refer to the design spreadsheet www.onsemi.com NCV 890100 page that helps with the calculation.

The design steps will be introduced through an example. Example:

Vin = 15.5 V, Vout = 3.3 V, Rload = 2.75  $\Omega,$  Iout = 1.2 A, L = 4.7  $\mu H,$  Cout = 20  $\mu F$  (Resr = 7 m $\Omega)$

The reference voltage of the feedback signal is 0.8 V and to meet the minimum load requirements, select RFB1 =  $100 \Omega$ , RFB2 =  $31.6 \Omega$ .

From the specification, the power stage transfer function can be plotted as below:

From the calculation: RCOMP = 10.6 K $\Omega$ , CCOMP = 2 nF, Cp = 37 pF So the feedback compensation network is as below:

Figure 31. Example of the Feedback Compensation Network

#### PCB LAYOUT RECOMMENDATION

As with any switching power supplies, there are some guidelines to follow to optimize the layout of the printed circuit board for the NCV 890100. However, because of the high switching frequency extra care has to be taken.

Minimize the area of the power current loops:

- ◆ Input capacitor  $\rightarrow$  NCV 890100 switch  $\rightarrow$  Inductor

- $\rightarrow$  output capacitor  $\rightarrow$  return through Ground

- Freewheeling diode → inductor → Output capacitor

→ return through ground

DFN8, 3x3, 0.65P CASE 506BY ISSUE A

#### DATE 23 MAY 2012

- NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

FOR DEVICE OPN CONTAINING W OPTION,

SCALE 2:1

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or incruit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi