# onse i

| Pin No.     | Pin Name | Description                                                                                                                                                                                                   |  |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | VIN      | Input voltage from battery. Place an input filter capacitor in close proximity to this pin.                                                                                                                   |  |  |  |

| 2           | RSTB     | Reset reporting flag. Open drain output, pulling down to ground when the output voltage is or of regulation. The value of the external pull-up resistor determines the delay time that the Reset is held low. |  |  |  |

| 3           | GND      | Analog ground reference – should be connected directly to the output capacitor ground and exposed pad.                                                                                                        |  |  |  |

| 4           | EN       | Enable input. Connecting a "high" voltage (TTL compatible, battery voltage tolerant) to this p turns on the regulator. A low voltage forces the part into a very low lq shutdown mode.                        |  |  |  |

| 5           | VOUT     | Output voltage sensing for regulation.                                                                                                                                                                        |  |  |  |

| 6           | SYNC     | Synchronization input. Connecting an external clock to this pin synchronizes switching to the rising edge of the SYNC signal.                                                                                 |  |  |  |

| 7           | PGND     | Power ground, connect directly to the input capacitor ground and to the exposed pad.                                                                                                                          |  |  |  |

| 8           | SW       | Switching node of the Regulator. Connect the output inductor to this pin.                                                                                                                                     |  |  |  |

| Exposed Pad | EPAD     | Must be connected to GND (pin 3, electrical ground) and to a low thermal resistance path to the ambient temperature environment.                                                                              |  |  |  |

### Table 1. PIN FUNCTION DESCRIPTIONS

#### Table 2. ABSOLUTE MAXIMUM RATINGS

Rating

Symbol

#### Table 3. ELECTRICAL CHARACTERISTICS

$(V_{IN} = 4.5 \text{ V to } 28 \text{ V}, \text{EN} = 5 \text{ V}. \text{Min/Max}$  values are valid for the temperature range  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Parameter                  | Test Conditions                        | Symbol           | Min | Тур | Max | Unit |

|----------------------------|----------------------------------------|------------------|-----|-----|-----|------|

| QUIESCENT CURRENT          |                                        |                  |     |     |     |      |

| Quiescent Current, Enabled | V <sub>IN</sub> = 13.2 V, no switching | I <sub>qEN</sub> |     | 2.0 | 3.0 | mA   |

Quiescent Current, Shutdown

#### www.onsemi.com 5

NCV890430

# **TYPICAL CHARACTERISTICS**

100

## **APPLICATION INFORMATION**

## **General Description**

The NCV890430 is a high-frequency synchronous switch-mode regulator with current-mode control, fixed output voltage and fixed internal closed-loop compensation, accepting a wide input voltage range typical to automotive applications.

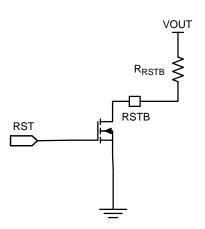

### **RESET** Function

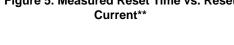

The RSTB pin is pulled low when the output voltage falls below 7% of the nominal regulation level, and floats when the output is properly regulated. A pull-up resistor tied to the output is needed to generate a logic high signal on this open-drain pin. The pin can be left unconnected when not used.

When the output voltage drops out of regulation, the pin goes low after a short noise-filtering delay ( $t_{RES}_{FILT}$ ). After the output goes back to regulation, the RSTB pin stays low for an adjustable delay time, simplifying the connection to a micro-controller.

The RSTB signal can either be used as a reset with delay or a power good (no delay). The adjustable delay is determined by the current into the RSTB pin, set by a resistor, as shown in Figure 10.

Use the following equation to determine the ideal reset delay time using currents less than  $500 \,\mu\text{A}$ :

$$t_{delay} = \frac{2500}{I_{RSTB}}$$

(eq. 1)

where:  $t_{delay}$  is the ideal reset delay time [ms]

$I_{RSTB}$  is the current into the RSTB pin [ $\mu$ A]

Using  $I_{RSTB} = 1$  mA removes the delay and allows the reset to act as a "power good" pin.

#### Table 4. TYPICAL DELAY TIMES – MEASURED

Figure 10. Reset with Adjustable Delay on a Single Pin

The RSTB resistor is commonly tied to VOUT. A RSTB resistor value that sets the current at the reset pin between 0.5 mA and 1 mA is not recommended due to the variation of the threshold between a set delay time and power good. Depending on the output voltage option, typical delay times can be achieved with the following resistor values:

| R <sub>RSTB</sub> (kΩ) | t <sub>delay</sub> (ms) – 5 V | t <sub>delay</sub> (ms) – 3.3 V | t <sub>delay</sub> (ms) – 2.5 V |

|------------------------|-------------------------------|---------------------------------|---------------------------------|

| 5                      | -                             | -                               | 5                               |

| 10                     | 5                             | 7.6                             | 10                              |

| 20                     | 10                            | 15                              | 20                              |

| 30                     | 15                            | 23                              | -                               |

| 50                     | 25                            | -                               | -                               |

#### Enable

The NCV890430 is designed to accept either a logic-level signal or battery voltage as an Enable signal. However, if voltages above 40 V are expected, EN should be tied to VIN through a 10 k $\Omega$  resistor in order to limit the current flowing into the overvoltage protection of the pin.

A low signal on Enable induces a shutdown mode which shuts off the regulator and minimizes its supply current to less than 5  $\mu$ A by disabling all functions.

Once the switching regulator output is enabled, a soft-start is always initiated.

#### **Thermal Shutdown**

A thermal shutdown circuit inhibits switching and resets the soft-start circuit if internal temperature exceeds a safe level indicated by the Thermal Shutdown Activation Temperature. Switching is automatically restored when temperature returns to a safe level based on the Thermal Shutdown Hysteresis.

#### Synchronization

Any number of NCV890430 can be synchronized to an external clock. If a part does not have its switching frequency controlled by the SYNC input, the part will be driven at the 2 MHz default switching frequency. A rising edge at the SYNC pin causes an NCV890430 to immediately turn on the power switch. If another rising edge does not arrive at the SYNC pin, the NCV890430 will start controlling its own frequency within the Master Reassertion Time. This allows uninterrupted operation if the clock is turned off. An external pulldown resistor is not needed at the SYNC pin if it is unconnected.

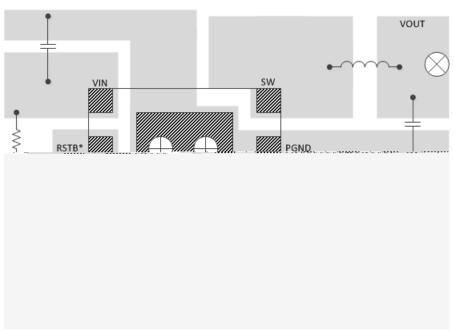

#### **Exposed Pad**

The exposed pad (EPAD) on the back of the package must be electrically connected to both the analog and the power electrical ground GND and PGND pins for proper, noise-free operation. It is recommended to connect these 2 pins directly to the EPAD with a PCB trace. Refer to the Recommended Layout for more information.

## **DEVICE ORDERING INFORMATION**

| Device           | Output | Marking   | Package   | Shipping <sup>†</sup> |

|------------------|--------|-----------|-----------|-----------------------|

| NCV890430MW50TXG | 5.0 V  | V8904050G | DFN8      | 2000 / Tana & Baal    |

| NCV890430MW33TXG | 3.3 V  | V8904033G | (Pb-Free) | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

## **RECOMMENDED LAYOUT**

Figure 11. Recommended NCV890430 Layout

DFN8, 3x3, 0.65P CASE 506BY ISSUE A

## DATE 23 MAY 2012

- NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

FOR DEVICE OPN CONTAINING W OPTION,

SCALE 2:1