www.onsemi.com

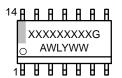

#### MARKING DIAGRAMS

8

A = Assembly Location

L, WL = Wafer Lot Y = Year W, WW = Work Week

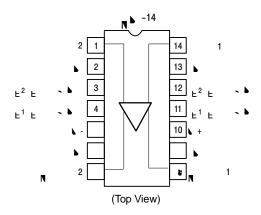

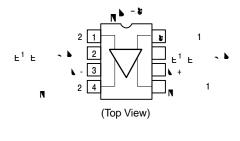

## **PIN CONNECTIONS**

# **MAXIMUM RATINGS** ( $T_A = +25^{\circ}C$ , unless otherwise noted.)

| Rating                                                                                                     | Symbol             | Value        | Unit |  |

|------------------------------------------------------------------------------------------------------------|--------------------|--------------|------|--|

| Supply Voltage                                                                                             | V <sub>CC</sub>    | ±8.0         | V    |  |

| Differential Input Voltage                                                                                 | V <sub>IN</sub>    | ±5.0         | V    |  |

| Common-Mode Input Voltage                                                                                  | V <sub>CM</sub>    | ±6.0         | V    |  |

| Output Current                                                                                             | l <sub>оит</sub>   | 10           | mA   |  |

| Operating Ambient Temperature Range                                                                        | T <sub>A</sub>     | 0 to +70     | °C   |  |

| Operating Junction Temperature                                                                             | T <sub>J</sub>     | 150          | °C   |  |

| Storage Temperature Range                                                                                  | T <sub>STG</sub>   | 65 to +150   | °C   |  |

| Maximum Power Dissipation, T <sub>A</sub> = 25°C (Still Air) (Note 1)<br>SOIC-14 Package<br>SOIC-8 Package | P <sub>D MAX</sub> | 0.98<br>0.79 | W    |  |

| Thermal Resistance, Junction-to-Ambient SOIC-14 Package SOIC-8 Package                                     | R <sub>θJA</sub>   | 145<br>182   | °C/W |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Derate above 25°C at the following rates:

SOIC-14 package at 6.9 mW/°C

SOIC-8 package at 5.5 mW/°C

**DC ELECTRICAL CHARACTERISTICS** ( $V_{SS} = \pm 6.0 \text{ V}$ ,  $V_{CM} = 0$ , typicals at  $T_A = +25^{\circ}\text{C}$ , min and max at  $0^{\circ}\text{C} \leq T_A \leq 70^{\circ}\text{C}$ , unless otherwise noted. Recommended operating supply voltages  $V_S = \pm 6.0 \text{ V}$ .)

| Characteristic                                                         | Test Conditions                                                                | Symbol           | Min            | Тур            | Max         | Unit |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------|----------------|----------------|-------------|------|

| Differential Voltage Gain<br>Gain 1 (Note 2)<br>Gain 2 (Notes 3 and 4) | $R_L = 2.0 \text{ k}\Omega, V_{OUT} = 3.0 V_{P-P}$                             | A <sub>VOL</sub> | 250<br>80      | 400<br>100     | 600<br>120  | V/V  |

| Input Resistance<br>Gain 1 (Note 2)<br>Gain 2 (Notes 3 and 4)          | 2) –                                                                           |                  | -<br>10<br>8.0 | 4.0<br>30<br>- | -<br>-<br>- | kΩ   |

| Input Capacitance                                                      | Gain 2 (Note 4)                                                                | C <sub>IN</sub>  | _              | 2.0            | -           | pF   |

| Input Offset Current                                                   | t Offset Current $ T_A = 25^{\circ}C \\ 0^{\circ}C \leq T_A \leq 70^{\circ}C $ |                  |                | -              |             |      |

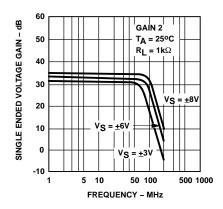

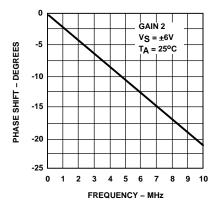

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

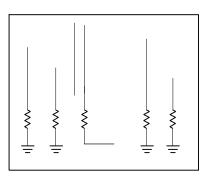

Basic Configuration

NOTE:

For frequency  $F_1 << 1/2 \pi$  (32) C

$$V_O \simeq 1.4 \times 10^4 C \frac{dVi}{dT}$$

Differentiation with High Common-Mode Noise Rejection

Disc/Tape Phase-Modulated Readback Systems

NOTE:

#### **ORDERING INFORMATION**

| Device      | Temperature Range | Package              | Shipping <sup>†</sup> |

|-------------|-------------------|----------------------|-----------------------|

| NE592D8R2G  | 0 to +70°C        | SOIC-8<br>(Pb-Free)  | 2500 / Tape & Reel    |

| NE592D14R2G |                   | SOIC-14<br>(Pb-Free) | 2500 / Tape & Reel    |

#### **DISCONTINUED** (Note 6)

| NE592D8G  | 0 to +70°C | SOIC-8<br>(Pb-Free)  | 98 Units/Rail |

|-----------|------------|----------------------|---------------|

| NE592D14G |            | SOIC-14<br>(Pb-Free) | 55 Units/Rail |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <a href="https://example.com/BRD8011/D">BRD8011/D</a>.

<sup>6.</sup> **DISCONTINUED:** These devices are not recommended for new design. Please contact your **onsemi** representative for information. The most current information on these devices may be available on <a href="https://www.onsemi.com">www.onsemi.com</a>.

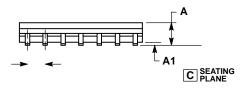

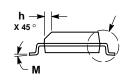

# SOIC 8 NB CASE 751-07 ISSUE AK

DATE 16 FEB 2011

SEATING PLANE

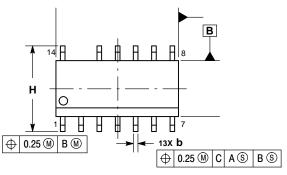

SOIC 14 NB CASE 751A-03 **ISSUE L**

#### **DATE 03 FEB 2016**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

5. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- SIDE.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code Α = Assembly Location

WL= Wafer Lot Υ = Year WW = Work Week G = Pb-Free Package

**STYLES ON PAGE 2**

#### SOIC 14 CASE 751A-03 ISSUE L

DATE 03 FEB 2016

STYLE 7:

PIN 1. ANODE/CATHODE

2. COMMON ANODE

3. COMMON CATHODE

4. ANODE/CATHODE

5. ANODE/CATHODE