# MOSFET Power Module 40 V, 30 A, Compact DIP

The STK984-190-E is a MOSFET power module containing 6 MOSFETs in a three-phase bridge (B6) configuration and a seventh MOSFET used as a reverse battery protection switch. The compact module is 29.6 mm 18.2 mm and is 4.3 mm high (see package drawing for specification details). The MOSFET module uses a DBC substrate for excellent

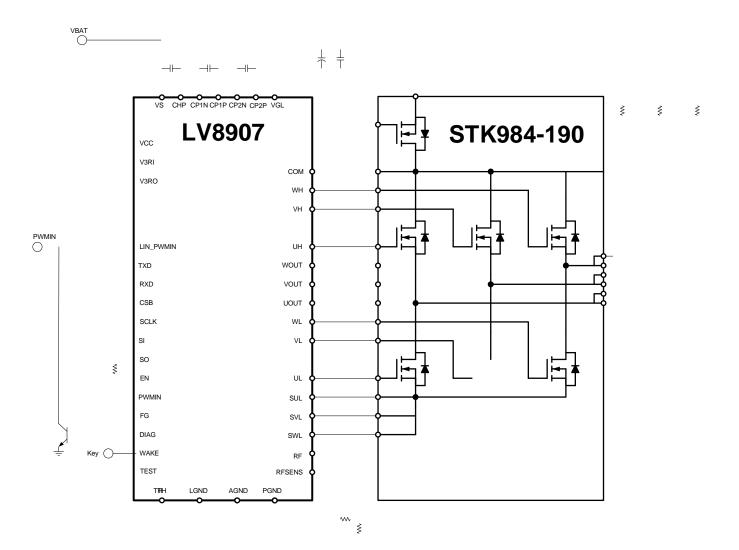

Figure 3: Block Diagram

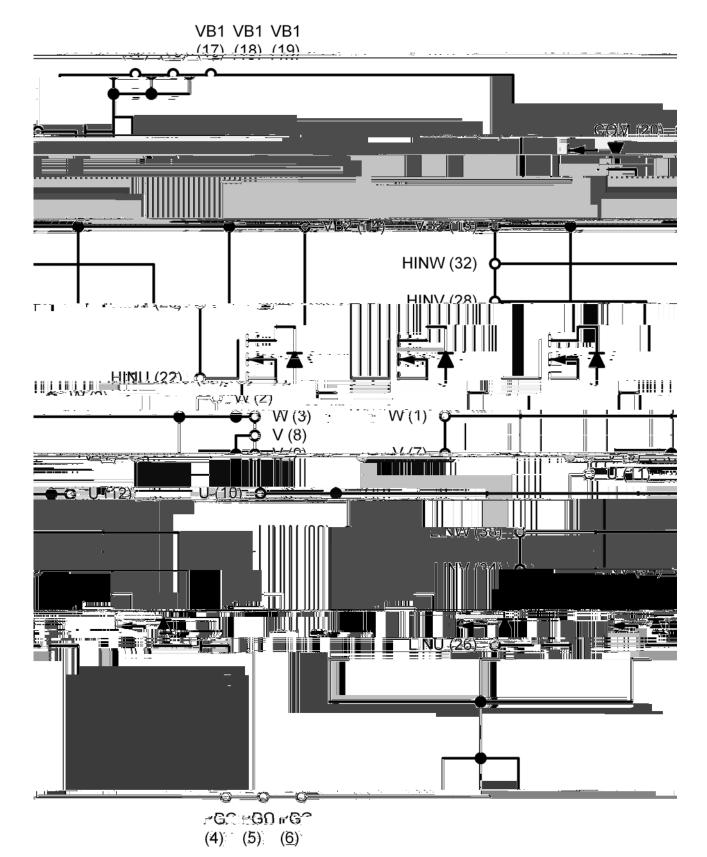

#### PIN FUNCTION DESCRIPTION

| Pin | Name | Description    |  |

|-----|------|----------------|--|

| 1   | W    | W Phase Output |  |

| 2   | W    | W Phase Output |  |

| 3   | W    | W Phase Output |  |

| 4   | PG   | Power Ground   |  |

| 5   | PG   | Power Ground   |  |

| 6   | PG   | Power Ground   |  |

| 7   | V    | V Phase Output |  |

| ΑВ | SOLUTE MAXIMUN         | RATINGS (Notes 1,2)        |                     |                    |                          |                   |

|----|------------------------|----------------------------|---------------------|--------------------|--------------------------|-------------------|

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

| 1. | Stresses exceeding the | hose listed in the Maximur | m Ratings table may | damage the device. | If any of these limits a | are exceeded, dev |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

|    |                        |                            |                     |                    |                          |                   |

#### **ELECTRICAL CHARACTERISTICS** (Note 4)

| Parameter                       | Symbol               | Test Conditions                                   | Min | Тур  | Max  | Unit  |

|---------------------------------|----------------------|---------------------------------------------------|-----|------|------|-------|

| Chip-Case Resistance            | j-c                  | Each MOSFET die to outside of case                | -   | -    | 4.1  | C/W   |

| Drain-to-Source Breakdown       | V <sub>BR(DSS)</sub> | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 250 μA    | 40  | -    | -    | V     |

| Voltage                         |                      |                                                   |     |      |      |       |

| Drain-to-Source Breakdown       | $V_{BR(DSS)}$        | Note 5                                            | -   | 40.8 | -    | mV/ C |

| Voltage Temperature Coefficient | /T <sub>J</sub>      |                                                   |     |      |      |       |

| Zero Gate Voltage Drain Current | I <sub>DSS</sub>     | $V_{GS} = 0 \text{ V}, V_{DS} = 40 \text{ V}$     | -   | -    | 1.0  | Α     |

| Gate-to-Source Leakage Current  | I <sub>GSS</sub>     | $V_{GS} = 0 \text{ V}, V_{GS} = \pm 20 \text{ V}$ |     |      | ±100 | nA    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. Typical data taken from packaged discrete device characteristics

#### **TYPICAL CHARACTERISTICS**

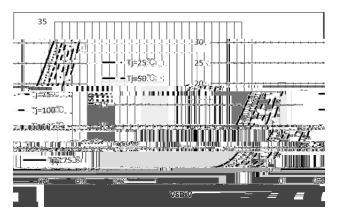

Figure 5 ID versus VDS for different temperatures (VGS = 10 V)

Figure 4 ID versus VDS for different VGS values (Tj = 175 C)

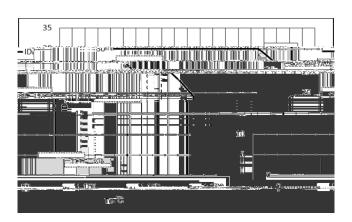

Figure 9 ISD versus VSD for different temperatures

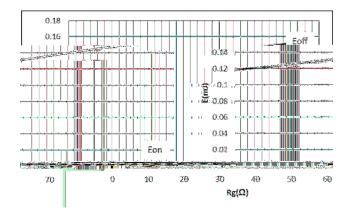

Figure 7 Switching losses versus drain current  $Tj = 175 \, C$ ,  $Id = 30 \, A$ ,  $Rg = 51 \, , L = 40 \, H$

Figure 6 Switching losses versus gate resistance  $Tj = 175 \, \text{C}$ ,  $Id = 30 \, \text{A}$ ,  $L = 40 \, \text{H}$

### **Mounting Instructions**

| Item      | Recommended Condition                                                                                                                                                          |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pitch     | 26.0±0.1 mm (Please refer to Package Outline Diagram)                                                                                                                          |  |

| Screw     | Diameter: M3 Screw head types: pan head, truss head, binding head                                                                                                              |  |

| Washer    | Plane washer dimensions (Figure 14) $D = 7 \text{ mm, } d = 3.2 \text{ mm and } t = 0.5 \text{ mm JIS B } 1256$                                                                |  |

| Heat sink | Material: Aluminum or Copper Warpage (the surface that contacts IPM): 50 to 50 m Screw holes must be countersunk. No contamination on the heat sink surface that contacts IPM. |  |

Torque

| PACKAGE DIMENSION | ONS |

|-------------------|-----|

|-------------------|-----|

unit: mm

CASE MODBL ISSUE A

4. PACKAGE IS MISSING PINS: 15, 16, 21, 2

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights not the rights of others. ON Semiconductor products are not designed intended or authorized for use as a critical component in life support including Typicals must be validated to each customer application by customer's technical experts. On Semiconductor does not convey any incense under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This liteŢJ67.669(S7w\beta(I)-1b)-9.7 r.1(i)-10(d9(S7w\betaCj)-9.7 r(S7w\beta(I-.1(4(es)\beta(I)-1(4(es)\beta(I)-269u1(i)-9.9((i)-9.9(40.6(fI)-1b)-9.S)d)-37 r.1(i)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-1)-10(d9(S7w\beta(I)-